Difference between revisions of "ATProgHead"

Jump to navigation

Jump to search

Blwikiadmin (talk | contribs) |

Blwikiadmin (talk | contribs) |

||

| Line 54: | Line 54: | ||

[[File:ATProghead-X2-PWB.PNG]] | [[File:ATProghead-X2-PWB.PNG]] | ||

| + | |||

| + | == Revisions == | ||

| + | |||

| + | === Revision X2 === | ||

| + | |||

| + | Revisions X2 is in development. | ||

| + | |||

| + | * Corrects issues found in Revision X1 boards. | ||

| + | * Adds 6 pin ISP connector as H2. | ||

| + | * [[GVSDuino]] changed to move D10 from pin 5 to pin 7 and add RST where D10 was previously. | ||

| + | **This allows GVSDuino to be programmed from the ISP connector and still support the ATProgHead adapter | ||

| + | *** Requires Rev X4 GVSDuino | ||

| + | <pre> | ||

| + | kiCompNL.py | ||

| + | |||

| + | First netlist: C:\Users\doug_000\Documents\GitHub\lb-boards\ATProgHead\ATProgHead-X1\ATProgHead.net | ||

| + | Number of Nets: 39 | ||

| + | Second netlist: C:\Users\doug_000\Documents\GitHub\lb-boards\ATProgHead\ATProgHead.net | ||

| + | Number of Nets: 39 | ||

| + | Mismatch in net (1): diff ['H1-7'] | ||

| + | Mismatch in net (1): diff ['H1-7'] | ||

| + | Mismatch in net (1): diff ['H1-7'] | ||

| + | Mismatch in net (1): diff ['H1-7'] | ||

| + | net is in 1 but not 2 ['MISO', 'U1-18', 'H1-1', 'U2-6'] | ||

| + | net is in 1 but not 2 ['SCK', 'U1-19', 'U2-7', 'H1-3'] | ||

| + | Mismatch in net (1): diff ['U1-16'] | ||

| + | Mismatch in net (1): diff ['U1-16'] | ||

| + | Mismatch in net (1): diff ['U1-16'] | ||

| + | Mismatch in net (1): diff ['U1-16'] | ||

| + | net is in 1 but not 2 ['RST', 'H1-5', 'U2-1', 'U1-1'] | ||

| + | net is in 1 but not 2 ['MOSI', 'U1-17', 'U2-5', 'H1-4'] | ||

| + | Mismatch in net (1): 5V diff ['D3-1', 'D2-1', 'D1-1'] | ||

| + | net is in 1 but not 2 ['PROG', 'R1-1', 'H1-8'] | ||

| + | net is in 1 but not 2 ['ERR', 'R2-1', 'H1-10'] | ||

| + | net is in 1 but not 2 ['HTBT', 'H1-12', 'R3-1'] | ||

| + | Mismatch in net (1): PG diff ['D1-2'] | ||

| + | Mismatch in net (1): ER diff ['D2-2'] | ||

| + | Mismatch in net (1): HB diff ['D3-2'] | ||

| + | Mismatch in net (1): diff ['U1-10', 'Y1-3'] | ||

| + | Mismatch in net (1): diff ['U1-10', 'Y1-3'] | ||

| + | Mismatch in net (1): diff ['U1-10', 'Y1-3'] | ||

| + | Mismatch in net (1): diff ['Y1-1', 'U1-9'] | ||

| + | Mismatch in net (1): diff ['Y1-1', 'U1-9'] | ||

| + | Mismatch in net (1): diff ['Y1-1', 'U1-9'] | ||

| + | Mismatch in net (2): ND diff ['D3-2', 'H2-6', 'D1-2', 'D2-2'] | ||

| + | Mismatch in net (2): 5V diff ['H2-2'] | ||

| + | Mismatch in net (2): diff ['H1-5'] | ||

| + | Mismatch in net (2): diff ['H1-5'] | ||

| + | Mismatch in net (2): diff ['H1-5'] | ||

| + | Mismatch in net (2): diff ['H1-5'] | ||

| + | net is in 2 but not 1 ['MISO-D12', 'U1-18', 'H2-1', 'H1-1', 'U2-6'] | ||

| + | net is in 2 but not 1 ['SCK-D13', 'U1-19', 'H2-3', 'H1-3', 'U2-7'] | ||

| + | net is in 2 but not 1 ['RST-D10', 'U1-1', 'U2-1', 'H2-5', 'H1-7'] | ||

| + | net is in 2 but not 1 ['MOSI-D11', 'H1-4', 'H2-4', 'U2-5', 'U1-17'] | ||

| + | net is in 2 but not 1 ['PROG-D7', 'R1-1', 'H1-8'] | ||

| + | net is in 2 but not 1 ['ERR-D8', 'R2-1', 'H1-10'] | ||

| + | net is in 2 but not 1 ['HTBT-D9', 'H1-12', 'R3-1'] | ||

| + | Mismatch in net (2): PG diff ['D1-1'] | ||

| + | Mismatch in net (2): ER diff ['D2-1'] | ||

| + | Mismatch in net (2): HB diff ['D3-1'] | ||

| + | Mismatch in net (2): diff ['U1-9', 'Y1-1'] | ||

| + | Mismatch in net (2): diff ['U1-9', 'Y1-1'] | ||

| + | Mismatch in net (2): diff ['U1-9', 'Y1-1'] | ||

| + | Mismatch in net (2): diff ['Y1-3', 'U1-10'] | ||

| + | Mismatch in net (2): diff ['Y1-3', 'U1-10'] | ||

| + | Mismatch in net (2): diff ['Y1-3', 'U1-10'] | ||

| + | Mismatch in net (2): diff ['U1-28'] | ||

| + | Mismatch in net (2): diff ['U1-28'] | ||

| + | Mismatch in net (2): diff ['U1-28'] | ||

| + | Mismatch in net (2): diff ['U1-28'] | ||

| + | </pre> | ||

Revision as of 13:12, 10 January 2020

Contents

ATmel Programmer Head

Description

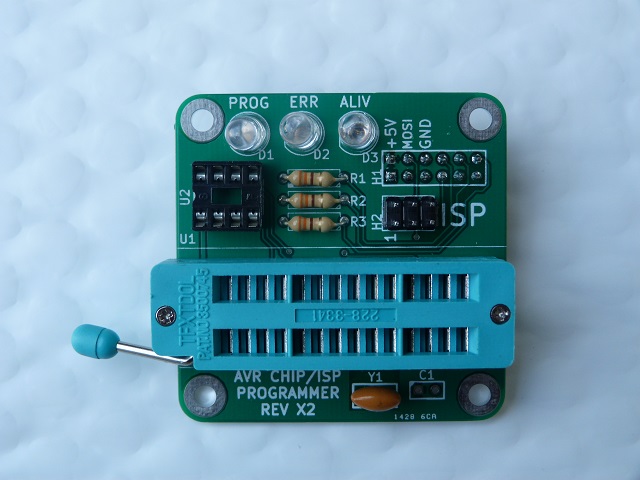

The ATmel Programming Head (ATProgHead) is used to program 28-pin and 8-pin Atmel (AVR) microprocessors.

Here is the ATProgHead installed on top of the GVSDuino (Rev X4 or higher) and a FTDI-USB-TTL card in a 3D printed case.

Features

ATProgHead board features include:

- Daughter card to the GVSDuino (Revision X4 or higher) and gets installed above the GVSDuino board

- Status LEDs

- PROG - Programming in progress

- ERR - Error while programming

- ALIV - Heartbeat

- On-board 16 MHz resonator

- Extended 12-pin ISP connector on bottom of board

- Separate 6-pin ISP header allows board to act as an ISP programmer

- The GVSDuino uses an FTDI-USB-TTL board for its USB host connection.

- ATProgHead supports ATMega328P, ATTiny85 and other Atmel AVR parts.

- Can be used to load bootloader onto factory fresh chips.

- Can be used to load sketches onto chips without the overhead of the bootloader.

- 28-pin ATMega328P socket has a Zero Insertion Force socket which allows for easier programming than standard sockets (no tools required).

- 8-pin DIP socket for ATTiny parts

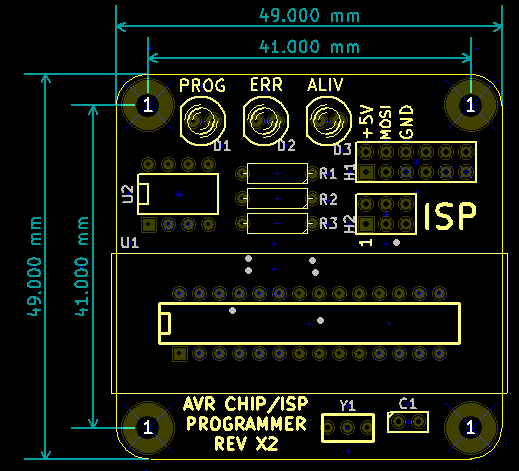

- 100mm square form factor

- 4-40 mounting hardware

- 3D printed standoffs for spacing off GVSDuino card

Compatible Software

- The board is compatible with ArduinoISP running on the GVSDuino.

- Details on programming ATTiny85 parts can be found here.

- Our ATProgHead ArduinoISP code is here (for our X1 board which had LED sense reversed).

Connectors

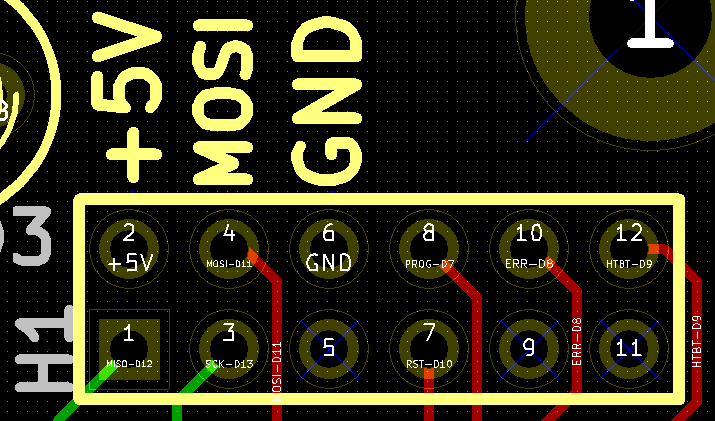

H1 - GVS Duino interconnect cable

The connector from the GVSDuino to the ATProgHead is:

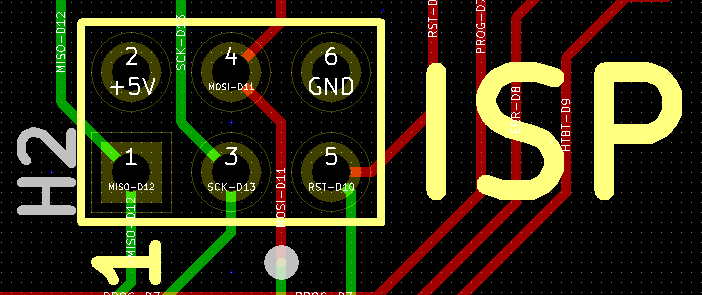

H2 - ISP Cable Connector

The ISP Connector pinout is:

Board Dimensions

Revisions

Revision X2

Revisions X2 is in development.

- Corrects issues found in Revision X1 boards.

- Adds 6 pin ISP connector as H2.

- GVSDuino changed to move D10 from pin 5 to pin 7 and add RST where D10 was previously.

- This allows GVSDuino to be programmed from the ISP connector and still support the ATProgHead adapter

- Requires Rev X4 GVSDuino

- This allows GVSDuino to be programmed from the ISP connector and still support the ATProgHead adapter

kiCompNL.py First netlist: C:\Users\doug_000\Documents\GitHub\lb-boards\ATProgHead\ATProgHead-X1\ATProgHead.net Number of Nets: 39 Second netlist: C:\Users\doug_000\Documents\GitHub\lb-boards\ATProgHead\ATProgHead.net Number of Nets: 39 Mismatch in net (1): diff ['H1-7'] Mismatch in net (1): diff ['H1-7'] Mismatch in net (1): diff ['H1-7'] Mismatch in net (1): diff ['H1-7'] net is in 1 but not 2 ['MISO', 'U1-18', 'H1-1', 'U2-6'] net is in 1 but not 2 ['SCK', 'U1-19', 'U2-7', 'H1-3'] Mismatch in net (1): diff ['U1-16'] Mismatch in net (1): diff ['U1-16'] Mismatch in net (1): diff ['U1-16'] Mismatch in net (1): diff ['U1-16'] net is in 1 but not 2 ['RST', 'H1-5', 'U2-1', 'U1-1'] net is in 1 but not 2 ['MOSI', 'U1-17', 'U2-5', 'H1-4'] Mismatch in net (1): 5V diff ['D3-1', 'D2-1', 'D1-1'] net is in 1 but not 2 ['PROG', 'R1-1', 'H1-8'] net is in 1 but not 2 ['ERR', 'R2-1', 'H1-10'] net is in 1 but not 2 ['HTBT', 'H1-12', 'R3-1'] Mismatch in net (1): PG diff ['D1-2'] Mismatch in net (1): ER diff ['D2-2'] Mismatch in net (1): HB diff ['D3-2'] Mismatch in net (1): diff ['U1-10', 'Y1-3'] Mismatch in net (1): diff ['U1-10', 'Y1-3'] Mismatch in net (1): diff ['U1-10', 'Y1-3'] Mismatch in net (1): diff ['Y1-1', 'U1-9'] Mismatch in net (1): diff ['Y1-1', 'U1-9'] Mismatch in net (1): diff ['Y1-1', 'U1-9'] Mismatch in net (2): ND diff ['D3-2', 'H2-6', 'D1-2', 'D2-2'] Mismatch in net (2): 5V diff ['H2-2'] Mismatch in net (2): diff ['H1-5'] Mismatch in net (2): diff ['H1-5'] Mismatch in net (2): diff ['H1-5'] Mismatch in net (2): diff ['H1-5'] net is in 2 but not 1 ['MISO-D12', 'U1-18', 'H2-1', 'H1-1', 'U2-6'] net is in 2 but not 1 ['SCK-D13', 'U1-19', 'H2-3', 'H1-3', 'U2-7'] net is in 2 but not 1 ['RST-D10', 'U1-1', 'U2-1', 'H2-5', 'H1-7'] net is in 2 but not 1 ['MOSI-D11', 'H1-4', 'H2-4', 'U2-5', 'U1-17'] net is in 2 but not 1 ['PROG-D7', 'R1-1', 'H1-8'] net is in 2 but not 1 ['ERR-D8', 'R2-1', 'H1-10'] net is in 2 but not 1 ['HTBT-D9', 'H1-12', 'R3-1'] Mismatch in net (2): PG diff ['D1-1'] Mismatch in net (2): ER diff ['D2-1'] Mismatch in net (2): HB diff ['D3-1'] Mismatch in net (2): diff ['U1-9', 'Y1-1'] Mismatch in net (2): diff ['U1-9', 'Y1-1'] Mismatch in net (2): diff ['U1-9', 'Y1-1'] Mismatch in net (2): diff ['Y1-3', 'U1-10'] Mismatch in net (2): diff ['Y1-3', 'U1-10'] Mismatch in net (2): diff ['Y1-3', 'U1-10'] Mismatch in net (2): diff ['U1-28'] Mismatch in net (2): diff ['U1-28'] Mismatch in net (2): diff ['U1-28'] Mismatch in net (2): diff ['U1-28']