Difference between revisions of "ER-DELAY-01"

Jump to navigation

Jump to search

Blwikiadmin (talk | contribs) (→Design) |

Blwikiadmin (talk | contribs) (→Nets) |

||

| Line 61: | Line 61: | ||

/J4-T,J29-6, | /J4-T,J29-6, | ||

/OUT,C14-2,J29-8, | /OUT,C14-2,J29-8, | ||

| + | /P2,C3-1,U1-2, | ||

| + | /P6,R1-1,U1-6, | ||

| + | /P7,C4-1,U1-7, | ||

| + | /P8,C5-1,U1-8, | ||

| + | /P9,C7-1,U1-9, | ||

| + | /P10,C7-2,U1-10, | ||

| + | /P11,C6-1,U1-11, | ||

| + | /P12,C6-2,R3-2,U1-12, | ||

| + | /P13,C8-2,R4-2,U1-13, | ||

| + | /P14,C8-1,R5-2,R9-1,U1-14, | ||

| + | /P15,C11-2,R6-1,R8-1,U1-15, | ||

| + | /P15A,C14-1,R8-2, | ||

| + | /P16,C11-1,R7-1,U1-16, | ||

| + | /P16A,C15-1,C16-1,R12-2,R6-2,R7-2, | ||

/POT1-2,C15-2,J28-18, | /POT1-2,C15-2,J28-18, | ||

/POT1-3,C12-2,J28-19, | /POT1-3,C12-2,J28-19, | ||

| Line 68: | Line 82: | ||

/VCO,J28-8,R1-2, | /VCO,J28-8,R1-2, | ||

GND,C1-2,C10-2,C13-2,C16-2,C18-2,C2-2,C3-2,C4-2,C5-2,C9-2,J28-20,J29-1,J29-15,J29-16,J9-3,J9-4,J9-5,J9-6,J9-7,J9-8,R13-1,U1-3,U1-4,U2-2, | GND,C1-2,C10-2,C13-2,C16-2,C18-2,C2-2,C3-2,C4-2,C5-2,C9-2,J28-20,J29-1,J29-15,J29-16,J9-3,J9-4,J9-5,J9-6,J9-7,J9-8,R13-1,U1-3,U1-4,U2-2, | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

Net-(C9-Pad1),C9-1,R3-1,R4-1,R5-1, | Net-(C9-Pad1),C9-1,R3-1,R4-1,R5-1, | ||

| − | |||

| − | |||

Net-(C12-Pad1),C12-1,C13-1,R9-2, | Net-(C12-Pad1),C12-1,C13-1,R9-2, | ||

| − | |||

| − | |||

Net-(C17-Pad1),C17-1,R12-1, | Net-(C17-Pad1),C17-1,R12-1, | ||

Net-(D1-Pad2),D1-2,RA1-1, | Net-(D1-Pad2),D1-2,RA1-1, | ||

| Line 97: | Line 98: | ||

Net-(J11-Pad2),J11-2,J14-2,J8-1,J8-20, | Net-(J11-Pad2),J11-2,J14-2,J8-1,J8-20, | ||

Net-(J14-Pad1),J14-1,RV1-1, | Net-(J14-Pad1),J14-1,RV1-1, | ||

| − | |||

Net-(RB1-Pad1),RB1-1,RV1-2, | Net-(RB1-Pad1),RB1-1,RV1-2, | ||

</pre> | </pre> | ||

Revision as of 16:21, 22 January 2023

Features

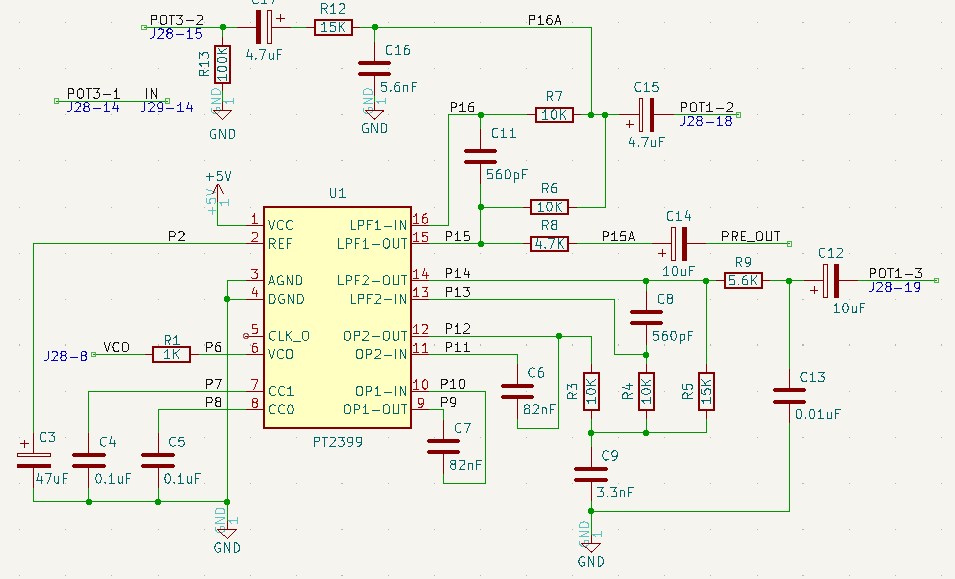

- PT2399 Delay/Echo

- The PT2399 is a CMOS single-chip echo processor IC

- A high sample rate ADC converts the analog data into a bitstream, which is then stored in internal 44Kbit RAM

- After processing, the bitstream is de-modulated by DAC and lowpass filter

- The internal VCO clock frequency determines the overall delay duration

- The user can easily modify the VCO frequency by changing the external resistance

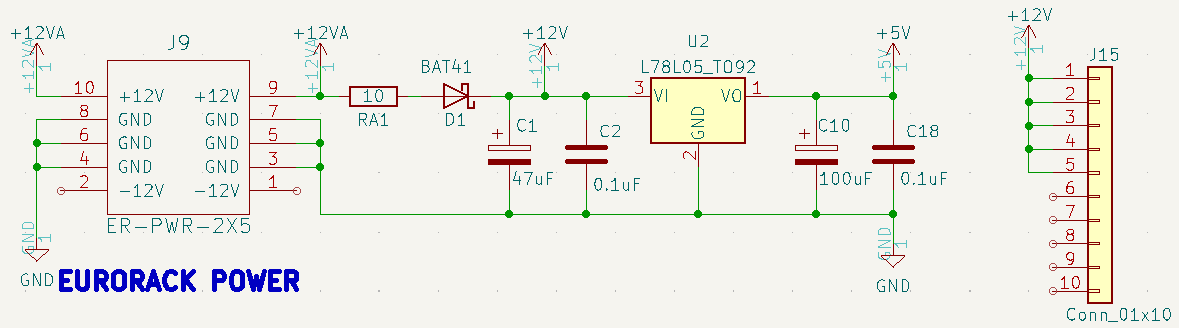

- Eurorack 3U, 6HP card

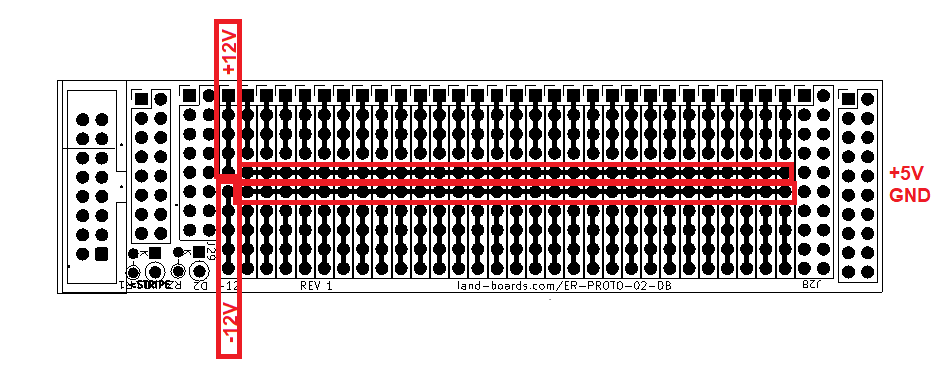

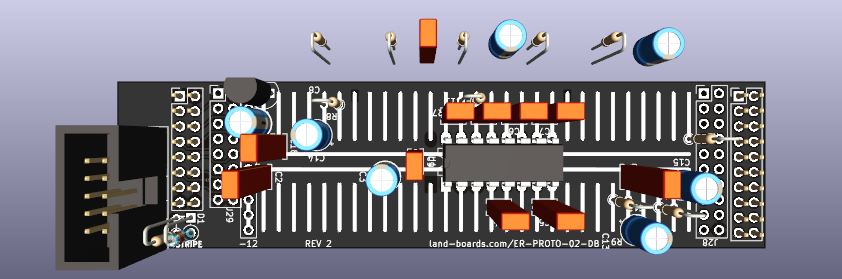

- Built on ER-PROTO-02 card

- PT2399 has a maximum current of 30mA

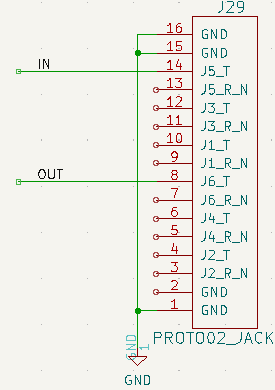

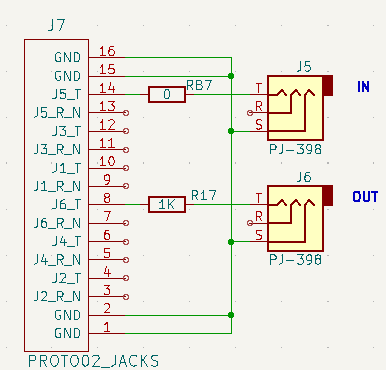

- Jacks

- J5 IN

- J6 OUT

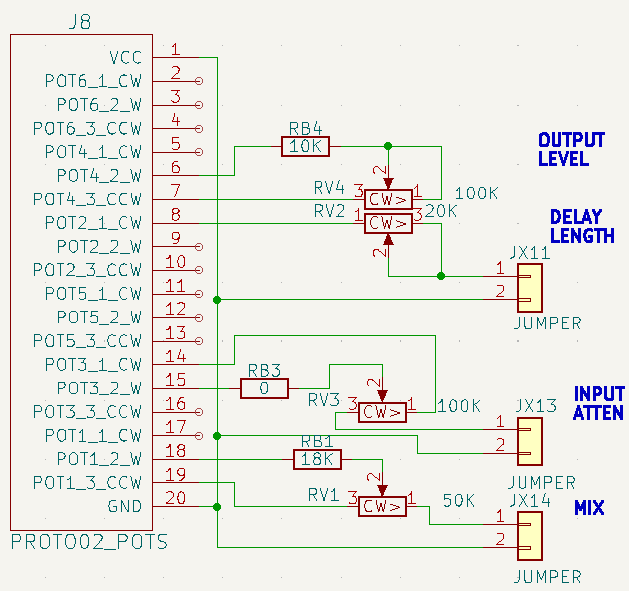

- Controls

- RV1 In/Out mix

- RV2 Delay Length

- 10 pin Eurorack power jack

Design

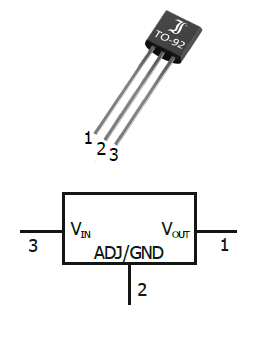

Daughtercard Prototyping Area

- PT2399 Delay IC

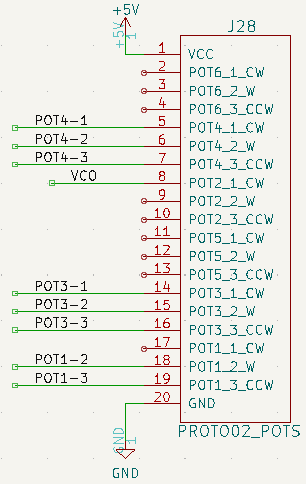

- Pots connector on Daughtercard

- Jacks connector on Daughtercard

- Power connector on Daughtercard

- Pots connector on Controls card

- Pots connector on Controls card

Nets

+5V,C10-1,C18-1,J28-1,U1-1,U2-1, +12V,C1-1,C2-1,D1-1,J15-1,J15-2,J15-3,J15-4,J15-5,U2-3, +12VA,J9-10,J9-9,RA1-2, /IN,C17-2,J29-14,R13-2, /J4-T,J29-6, /OUT,C14-2,J29-8, /P2,C3-1,U1-2, /P6,R1-1,U1-6, /P7,C4-1,U1-7, /P8,C5-1,U1-8, /P9,C7-1,U1-9, /P10,C7-2,U1-10, /P11,C6-1,U1-11, /P12,C6-2,R3-2,U1-12, /P13,C8-2,R4-2,U1-13, /P14,C8-1,R5-2,R9-1,U1-14, /P15,C11-2,R6-1,R8-1,U1-15, /P15A,C14-1,R8-2, /P16,C11-1,R7-1,U1-16, /P16A,C15-1,C16-1,R12-2,R6-2,R7-2, /POT1-2,C15-2,J28-18, /POT1-3,C12-2,J28-19, /POT3-1,J28-14, /POT3-2,J28-15, /POT3-3,J28-16, /VCO,J28-8,R1-2, GND,C1-2,C10-2,C13-2,C16-2,C18-2,C2-2,C3-2,C4-2,C5-2,C9-2,J28-20,J29-1,J29-15,J29-16,J9-3,J9-4,J9-5,J9-6,J9-7,J9-8,R13-1,U1-3,U1-4,U2-2, Net-(C9-Pad1),C9-1,R3-1,R4-1,R5-1, Net-(C12-Pad1),C12-1,C13-1,R9-2, Net-(C17-Pad1),C17-1,R12-1, Net-(D1-Pad2),D1-2,RA1-1, Net-(J5-PadS),J5-S,J6-R,J7-15,J7-16, Net-(J5-PadT),J5-T,RB7-1, Net-(J6-PadS),J6-S,J7-1,J7-2, Net-(J6-PadT),J6-T,R17-1, Net-(J7-Pad8),J7-8,R17-2, Net-(J7-Pad14),J7-14,RB7-2, Net-(J8-Pad8),J8-8,RV2-1, Net-(J8-Pad18),J8-18,RB1-2, Net-(J8-Pad19),J8-19,RV1-3, Net-(J11-Pad1),J11-1,RV2-2,RV2-3, Net-(J11-Pad2),J11-2,J14-2,J8-1,J8-20, Net-(J14-Pad1),J14-1,RV1-1, Net-(RB1-Pad1),RB1-1,RV1-2,