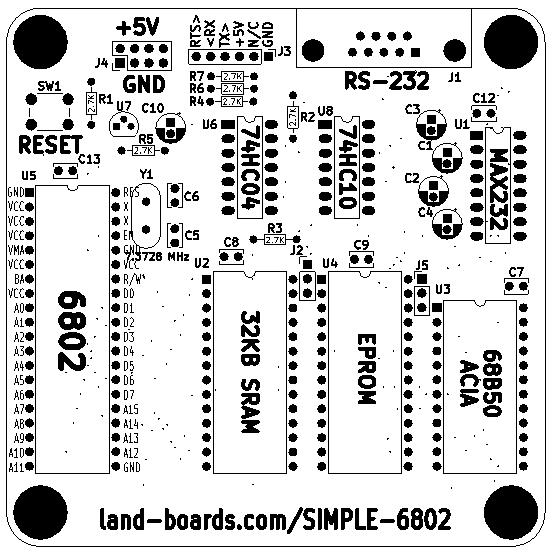

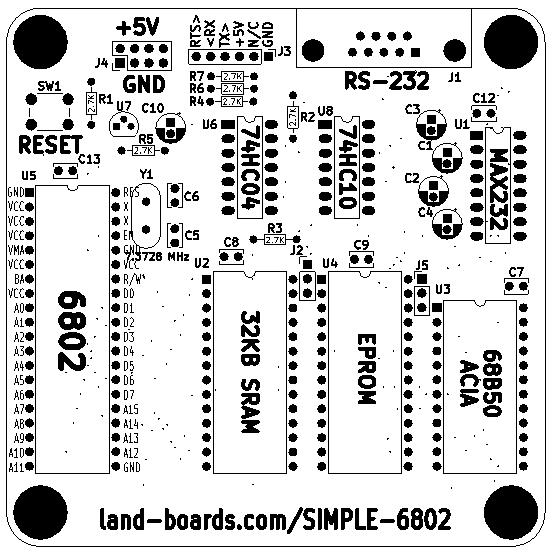

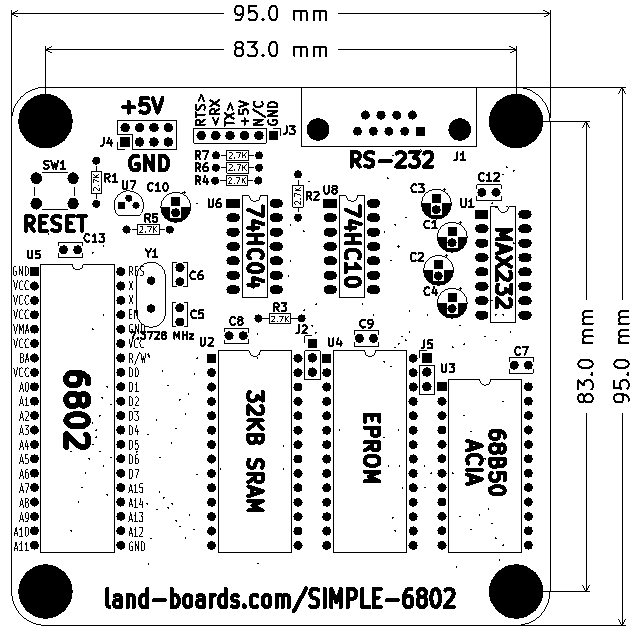

Features

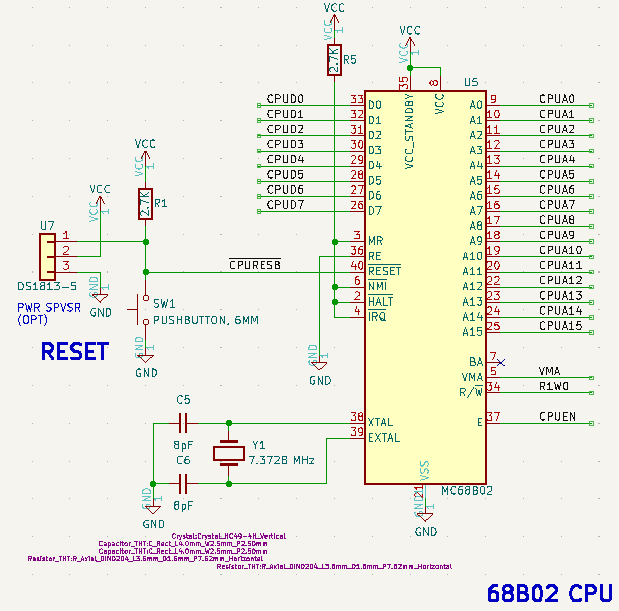

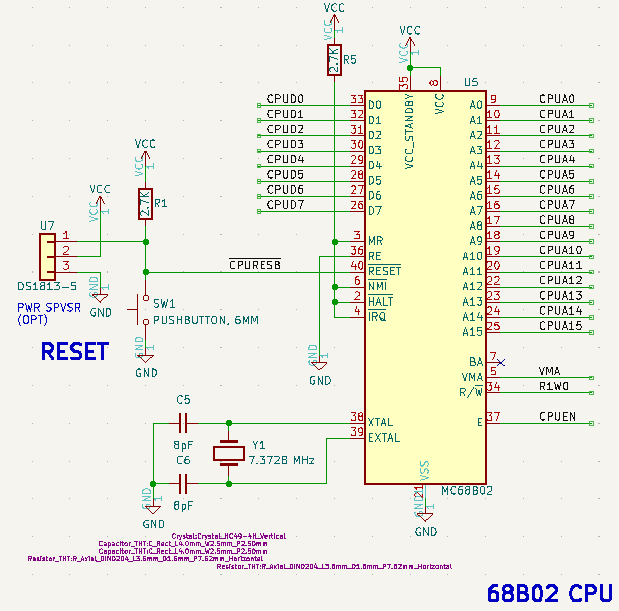

- 68B02 CPU

- 1.8432 MHz clock

- MC6802 is fully compatible with MC6800 but without messy two-phase clocking

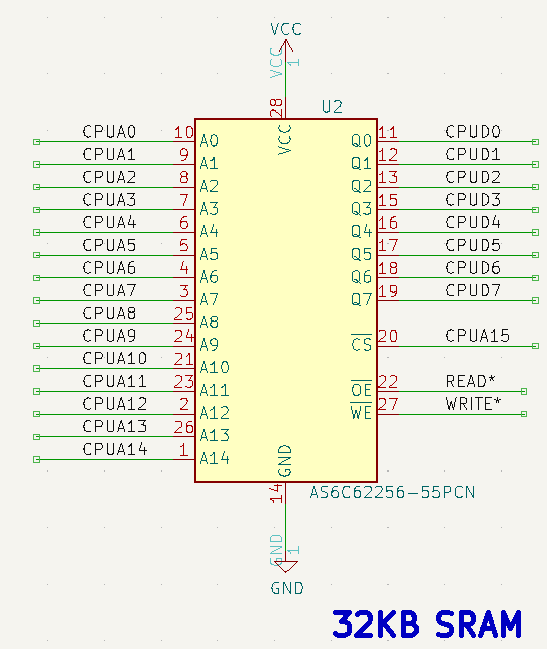

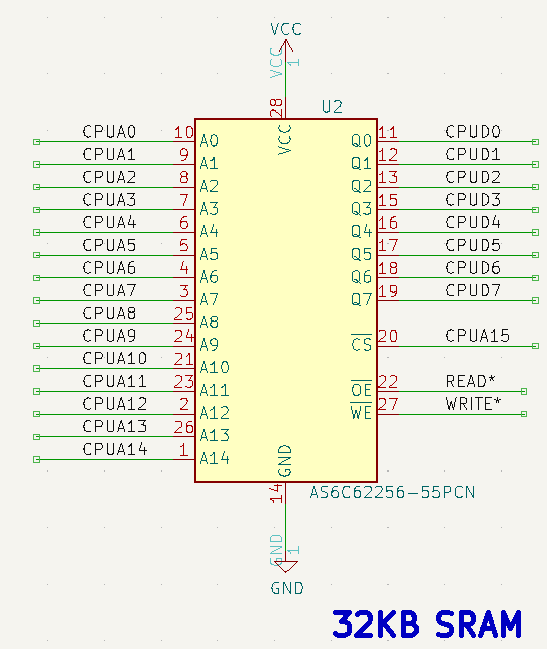

- 32KB SRAM

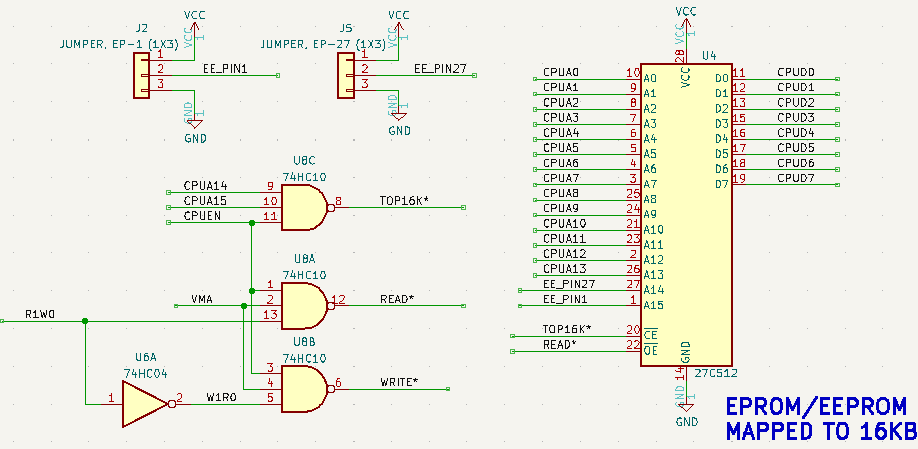

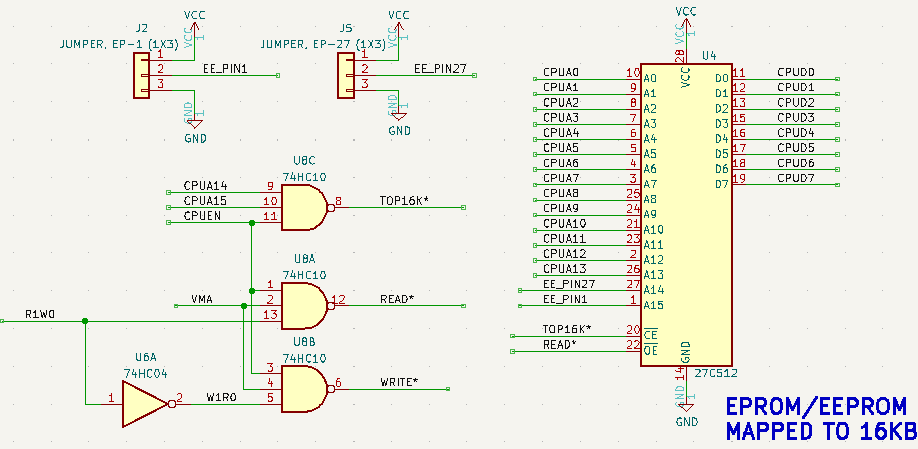

- 16KB EPROM/EEPROM

- 16KB reserved

- 8KB (28C64 parts can be used)

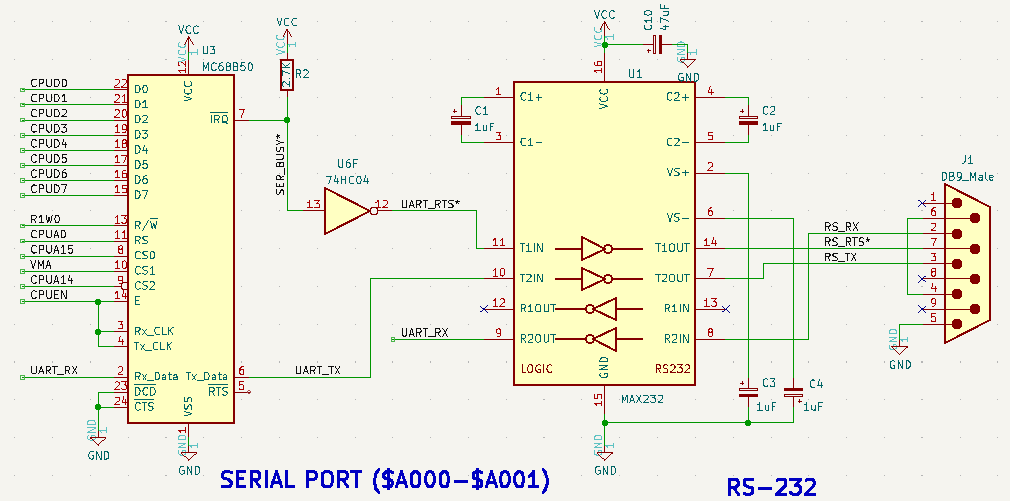

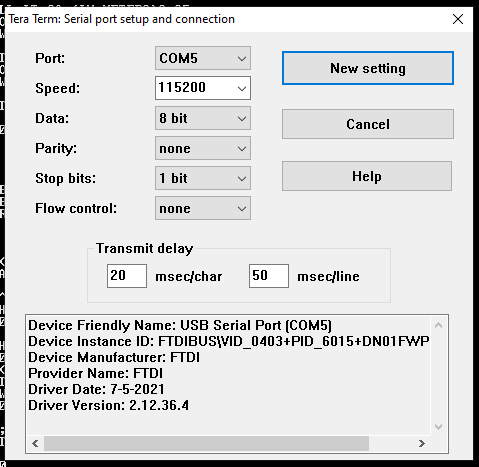

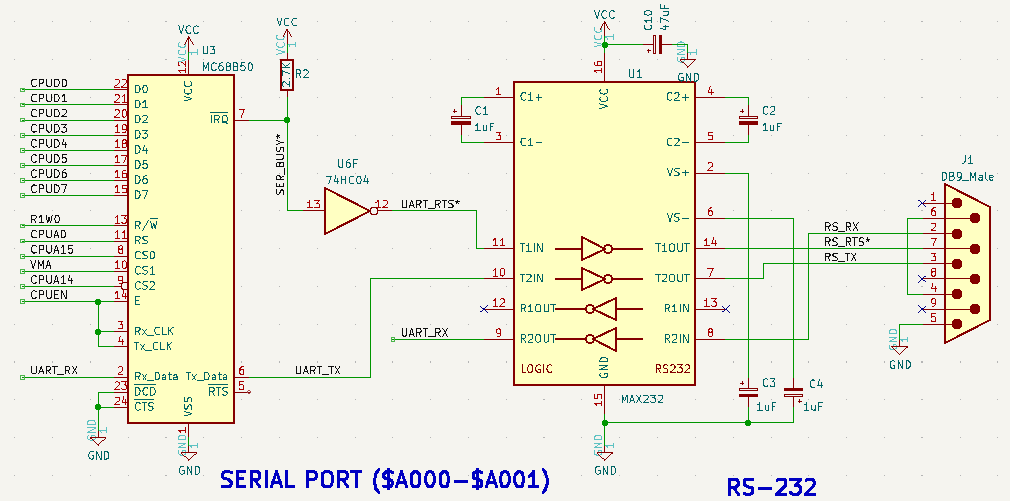

- 68B50 Serial Port (ACIA)

- RS-232 port

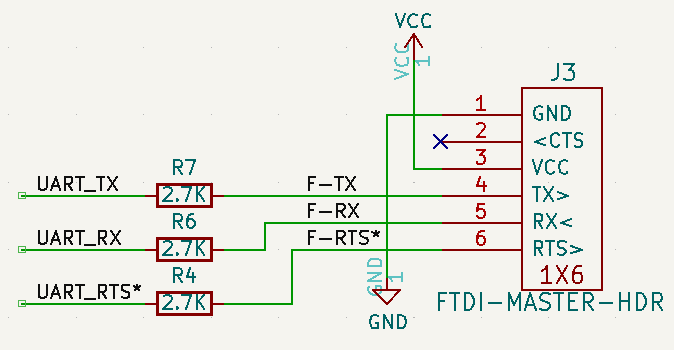

- Header for FTDI

- 115,200 baud

- Reset switch with optional Power Supervisor

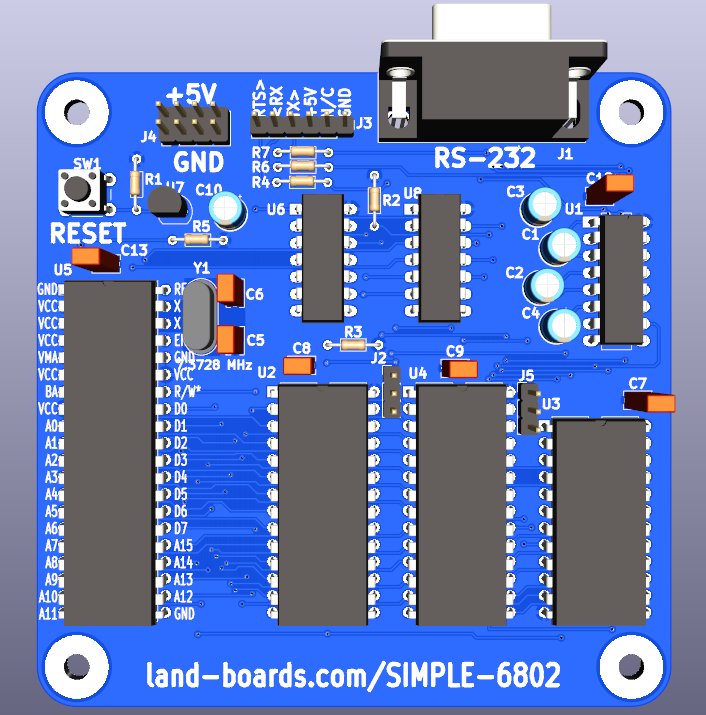

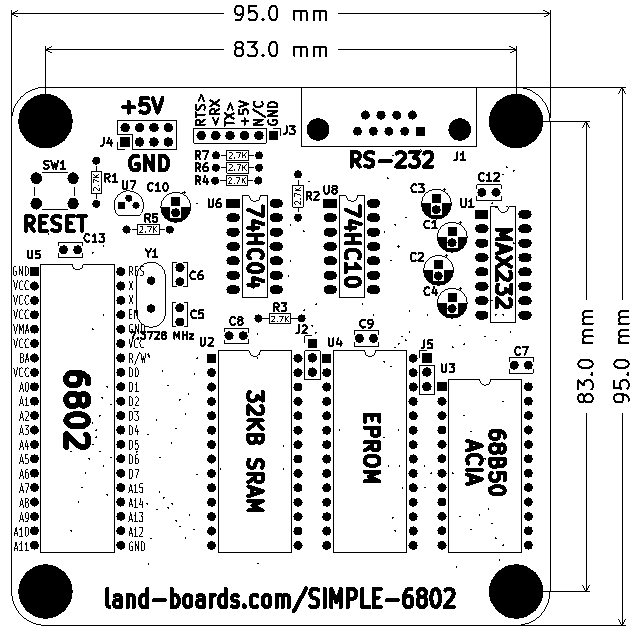

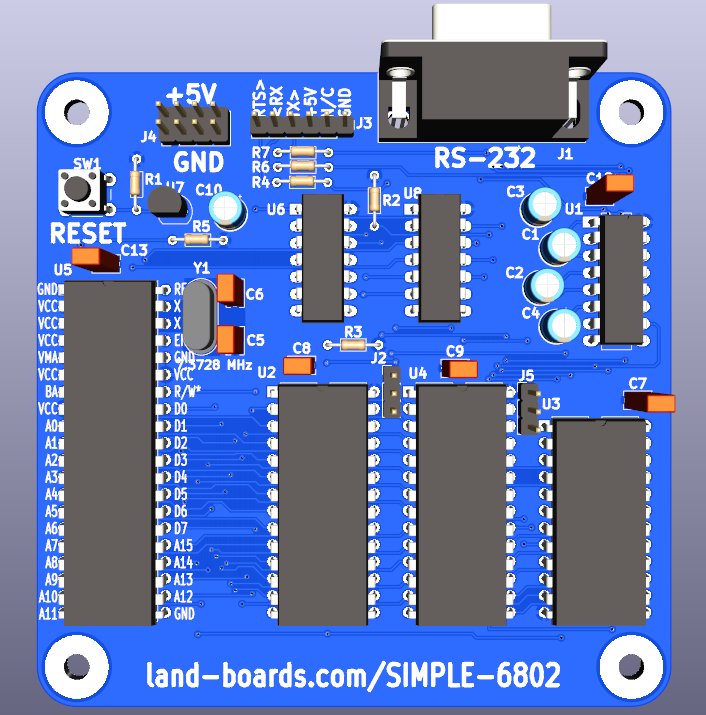

- 95x95mm card

- (4) 6-32 mounting holes

Memory Map

- 0x0000-0x7FFF 32KB SRAM

- 0x8000-0xBFFF Serial (ACIA)

- 0xC000-0xCFFF 16KB EPROM

Chipset

Design

J1 - RS-232 Serial

- N/C

- Receive

- Transmit

- Loop to pin 6

- GND

- Loop to pin 4

- RTS

- N/C

- N/C

J2 / J5 - EPROM/EEPROM Select Jumpers

- J2 - EPROM Pin 1 jumper

- 1-2 for 28C64, 28C256 (Pull WE to VCC)

- 2-3 for 27256, 27SF256, 27512 (Pull A14 to GND)

- J5 - EPROM Pin 27 jumper

EEPROM Pin Table

| 27512

|

27256

|

27SF256

|

28C256

|

27128

|

2764

|

28C64

|

PIN

|

|

PIN

|

2764

|

28C64

|

27128

|

28C256

|

27SF256

|

27256

|

27512

|

| A15

|

VPP

|

VPP

|

A14

|

VPP

|

VPP

|

N/C

|

1

|

|

28

|

VCC

|

VCC

|

VCC

|

VCC

|

VCC

|

VCC

|

VCC

|

| A12

|

A12

|

A12

|

A12

|

A12

|

A12

|

A12

|

2

|

|

27

|

PGM

|

WE*

|

PGM

|

WE*

|

A14

|

A14

|

A14

|

| A7

|

A7

|

A7

|

A7

|

A7

|

A7

|

A7

|

3

|

|

26

|

A13

|

N/C

|

A13

|

A13

|

A13

|

A13

|

A13

|

| A6

|

A6

|

A6

|

A6

|

A6

|

A6

|

A6

|

4

|

|

25

|

A8

|

A8

|

A8

|

A8

|

A8

|

A8

|

A8

|

| A5

|

A5

|

A5

|

A5

|

A5

|

A5

|

A5

|

5

|

|

24

|

A9

|

A9

|

A9

|

A9

|

A9

|

A9

|

A9

|

| A4

|

A4

|

A4

|

A4

|

A4

|

A4

|

A4

|

6

|

|

23

|

A11

|

A11

|

A11

|

A11

|

A11

|

A11

|

A11

|

| A3

|

A3

|

A3

|

A3

|

A3

|

A3

|

A3

|

7

|

|

22

|

OE*

|

OE*

|

OE*

|

OE*

|

OE*

|

OE*

|

OE*

|

| A2

|

A2

|

A2

|

A2

|

A2

|

A2

|

A2

|

8

|

|

21

|

A10

|

A10

|

A10

|

A10

|

A10

|

A10

|

A10

|

| A1

|

A1

|

A1

|

A1

|

A1

|

A1

|

A1

|

9

|

|

20

|

CE*

|

CE*

|

CE*

|

CE*

|

CE*

|

CE*

|

CE*

|

| A0

|

A0

|

A0

|

A0

|

A0

|

A0

|

A0

|

10

|

|

19

|

D7

|

D7

|

D7

|

D7

|

D7

|

D7

|

D7

|

| D0

|

D0

|

D0

|

D0

|

D0

|

D0

|

D0

|

11

|

|

18

|

D6

|

D6

|

D6

|

D6

|

D6

|

D6

|

D6

|

| D1

|

D1

|

D1

|

D1

|

D1

|

D1

|

D1

|

12

|

|

17

|

D5

|

D5

|

D5

|

D5

|

D5

|

D5

|

D5

|

| D2

|

D2

|

D2

|

D2

|

D2

|

D2

|

D2

|

13

|

|

16

|

D4

|

D4

|

D4

|

D4

|

D4

|

D4

|

D4

|

| GND

|

GND

|

GND

|

GND

|

GND

|

GND

|

GND

|

14

|

|

15

|

D3

|

D3

|

D3

|

D3

|

D3

|

D3

|

D3

|

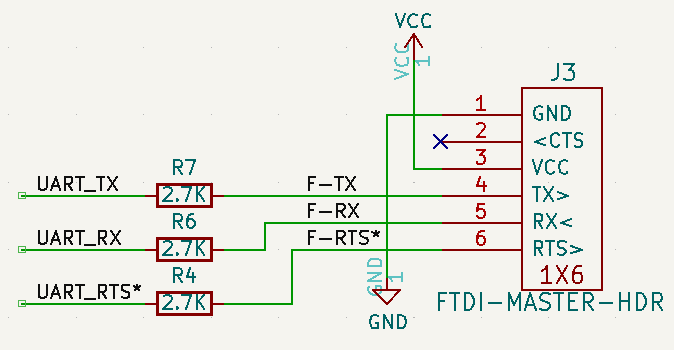

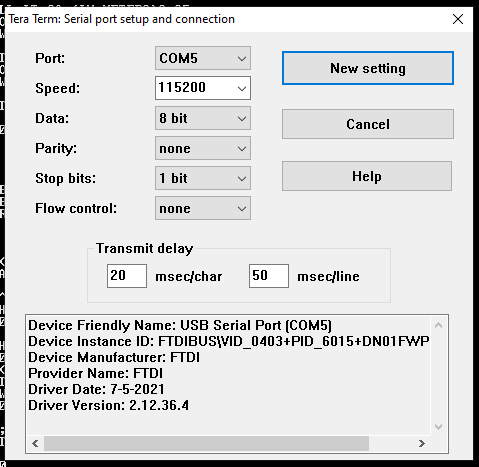

J3 - FTDI / TTL Serial

- Requires a FTDI cross-over cable

- GND

- RTS* (out)

- +5V

- Receive (in)

- Transmit (out)

- N/C

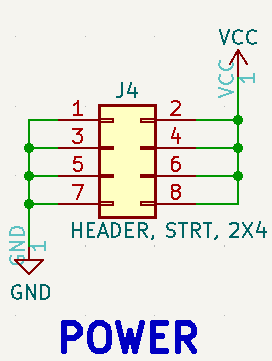

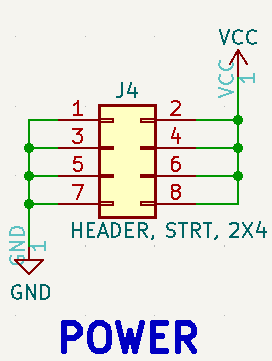

J4 - 5V Power

First Unit Checkout

Install Sockets

Install Passives

Power

- Install 2x4 at J4

- Power card via J4 with 5V

- Check power pins on parts

Software

SmithBUG Builds for SIMPLE-MC6802 CPU Card

Building Code

- Uses a68 assembler

- Command line makes S-Record output

- Use srec_cat to shift from EPROM absolute addresses to 0x0000 as HEX file

4KB Build

A68 SMITHBUG_SIMPLE-6802_F000.ASM -l SMITHBUG_SIMPLE-6802_F000.LST -s SMITHBUG_SIMPLE-6802_F000.S

srec_cat SMITHBUG_SIMPLE-6802_F000.s -offset - -minimum-addr SMITHBUG_SIMPLE-6802_F000.s -o smithbug_F000.hex -Intel

8KB Build

A68 SMITHBUG_SIMPLE-6802_E000.ASM -l SMITHBUG_SIMPLE-6802_E000.LST -s SMITHBUG_SIMPLE-6802_E000.S

srec_cat SMITHBUG_SIMPLE-6802_E000.s -offset - -minimum-addr SMITHBUG_SIMPLE-6802_E000.s -o smithbug_E000.hex -Intel

16KB Build

A68 SMITHBUG_SIMPLE-6802_C000.ASM -l SMITHBUG_SIMPLE-6802_C000.LST -s SMITHBUG_SIMPLE-6802_C000.S

srec_cat SMITHBUG_SIMPLE-6802_C000.s -offset - -minimum-addr SMITHBUG_SIMPLE-6802_C000.s -o smithbug_C000.hex -Intel

SmithBUG Commands

; M MOVE MEMORY

; E CHANGE MEMORY

; G GO TO PROGRAM

; R PRINT

; T TRACE PROGRAM

; @ ASCII CONVERSION

; H PRINTER ON

; V VIEW MEMORY

; I FILL MEMORY

; J JUMP TO TARGET PROGRAM

; F FIND

; Q HARDWARE LOCATION

; D DISASSEMBLE CODE

; K CONTINUE AFTER BREAK

; 1 BREAKPOINT ONE

; 2 BREAKPOINT TWO

; & S1 LOAD PROGRAM

; * HARDWARE LOCATION (TBA)

; O ECHO ON

; N ECHO OFF

Demo Software

FIGFORTH

- FIGFORTH

- Enter command to srecord loader

&

- Using TermTerm, File, Send File

- Send fig-FORTH_6800.s19

- Type S9 to exit srecord loader

- Responds with

Forth-68

OK

Performance

Mechanicals

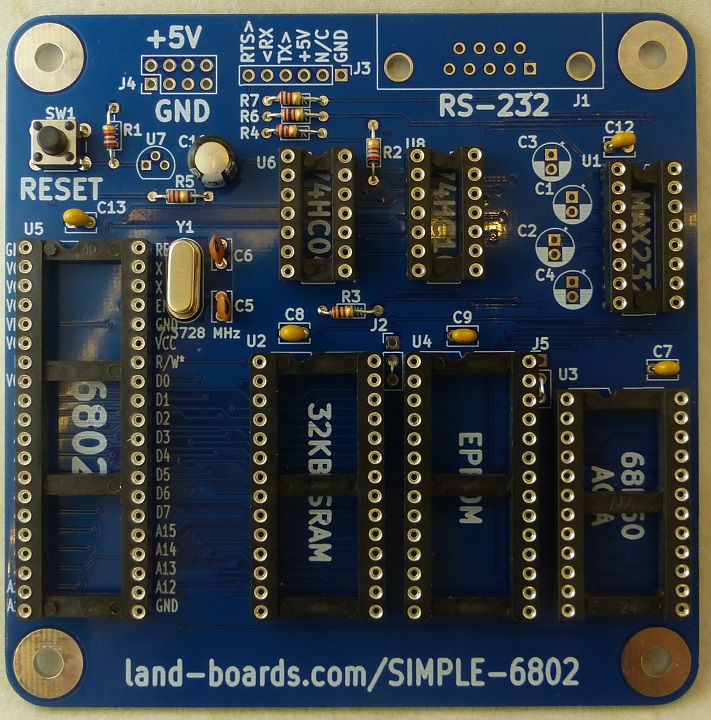

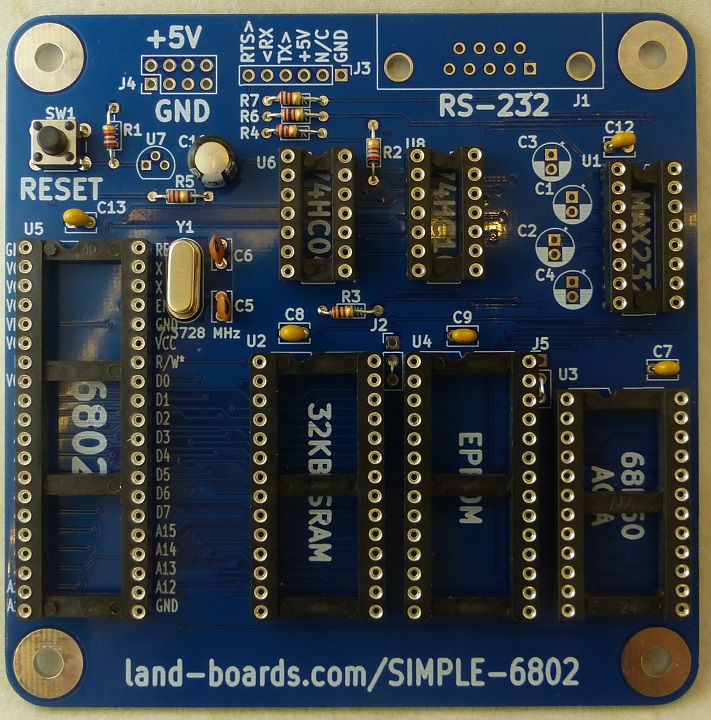

Assembly Sheet

SIMPLE-6802 Rev 1 Assembly Sheet