Difference between revisions of "PDP-8 Front Panel"

Jump to navigation

Jump to search

Blwikiadmin (talk | contribs) |

Blwikiadmin (talk | contribs) |

||

| Line 14: | Line 14: | ||

** DEP pushbutton - Store value from Value Slide Switches to memory | ** DEP pushbutton - Store value from Value Slide Switches to memory | ||

** LDA pushbutton - Store value from Value Slide Switches to Accumulator | ** LDA pushbutton - Store value from Value Slide Switches to Accumulator | ||

| − | ** RES - Reset pushbutton - | + | ** RES - Reset pushbutton - Resets CPU |

** PB1 - spare | ** PB1 - spare | ||

* LNK - Link value slide switch | * LNK - Link value slide switch | ||

Revision as of 14:04, 18 April 2021

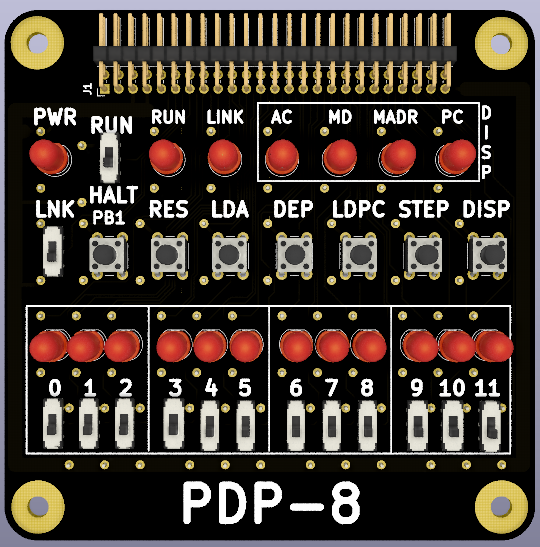

Features

- 12 Value LEDs

- Display options: PC, Memory Address, Memory Data, Accumulator

- 12 Load Value Slide Switches

- Enter values: PC, Memory Address, Memory Data, Accumulator

- Display select pushbutton

- Cycles between PC, Memory Address, Memory Data, Accumulator

- Pushbutton Switches

- STEP pushbutton - Increment PC

- LDPC pushbutton - Load PC from Value Slide Switches

- DEP pushbutton - Store value from Value Slide Switches to memory

- LDA pushbutton - Store value from Value Slide Switches to Accumulator

- RES - Reset pushbutton - Resets CPU

- PB1 - spare

- LNK - Link value slide switch

- DISP LEDs

- PC - 12 LEDs display Program Counter value

- PC - 12 LEDs display Memory Address value

- PC - 12 LEDs display Memory Data value

- PC - 12 LEDs display Accumulator value

- LINK LED - Displays Link value

- FN1 spare LED

- RUN/HALT slide switch

- PWR - Power LED

PDP-8 FPGA Design

- PDP-8 PFGA Design - GitHub repo

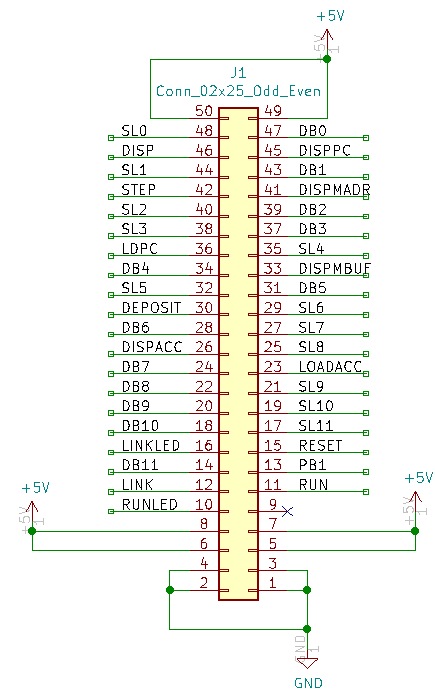

J1 Connector

- 50 pin connector matches RETRO-EP4CE15 Card

- Extra power and ground pins (not on RETRO-EP4CE15 Card)

- Pins 3,4 = GND

- Pins 5-8 = VCC

- Pin 9 = N/C

- Extra power and ground pins (not on RETRO-EP4CE15 Card)