Difference between revisions of "SIMPLE-Z80"

Jump to navigation

Jump to search

Blwikiadmin (talk | contribs) |

Blwikiadmin (talk | contribs) |

||

| Line 25: | Line 25: | ||

** 0x80-0x81 - Serial port (ACIA) | ** 0x80-0x81 - Serial port (ACIA) | ||

| − | == Connectors == | + | == Headers / Connectors == |

=== J1 - RS-232 Serial === | === J1 - RS-232 Serial === | ||

Revision as of 17:31, 12 September 2022

Contents

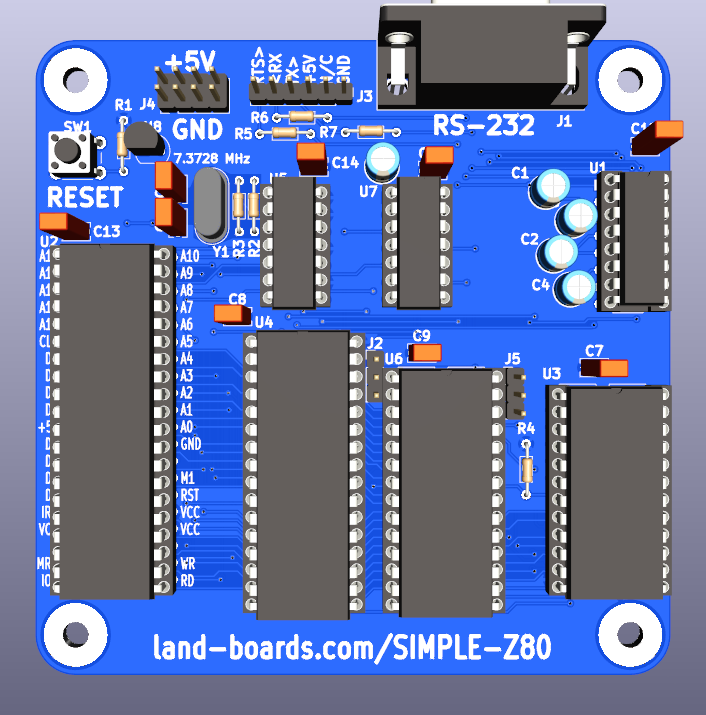

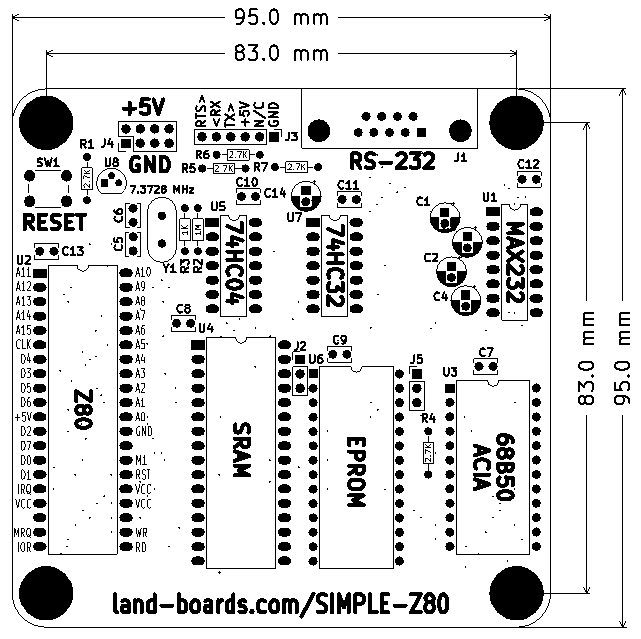

Features

- Build of Grant Searles's Simple Z80 CPU

- Runs BASIC

- Z80 CPU

- 7.3728 MHz clock

- 56KB SRAM (uses 128KB parts)

- 8KB EPROM/EEPROM

- 68B50 Serial Port (ACIA)

- RS-232 port

- Header for FTDI

- 115,200 baud

- Reset switch with optional Power Supervisor

- 95x95mm card

- (4) 6-32 mounting holes

Memory Map

- 0x0000-0x1FFF 8KB ROM

- 0x2000-0xFFFF 56KB SRAM

- I/O

- 0x00-0x7F - Free

- 0x80-0x81 - Serial port (ACIA)

Headers / Connectors

J1 - RS-232 Serial

- N/C

- Receive

- Transmit

- Loop to pin 6

- GND

- Loop to pin 4

- RTS

- N/C

- N/C

J2/J5 - EPROM/EEPROM Select Jumpers

| PART | J2 PIN 1 | J5 PIN 27 |

|---|---|---|

| 27128 EPROM | VPP (5V) | PGM (5V) |

| 27C256 EPROM | VPP (5V) | A14 (GND) |

| 27C512 EPROM | A15 (GND) | A14 (GND) |

| SST27SF256 EEPROM | VPP (5V) | A14 (GND) |

| SST27SF512 EEPROM | A15 (GND) | A14 (GND) |

J3 - FTDI / TTL Serial

- GND

- RTS* (out)

- +5V

- Receive (in)

- Transmit (out)

- N/C

J4 - 5V Power

- 2x4 header