Difference between revisions of "LB-65CXX-01"

Jump to navigation

Jump to search

Blwikiadmin (talk | contribs) |

Blwikiadmin (talk | contribs) |

||

| Line 4: | Line 4: | ||

* 65C02 or 65C816 CPU | * 65C02 or 65C816 CPU | ||

| − | * 2 MHz Oscillator on card | + | * 2 MHz (typical) Oscillator on card |

* Reset switch/power monitor | * Reset switch/power monitor | ||

* Address decoder PLD drives RAM/ROM/IO chip selects | * Address decoder PLD drives RAM/ROM/IO chip selects | ||

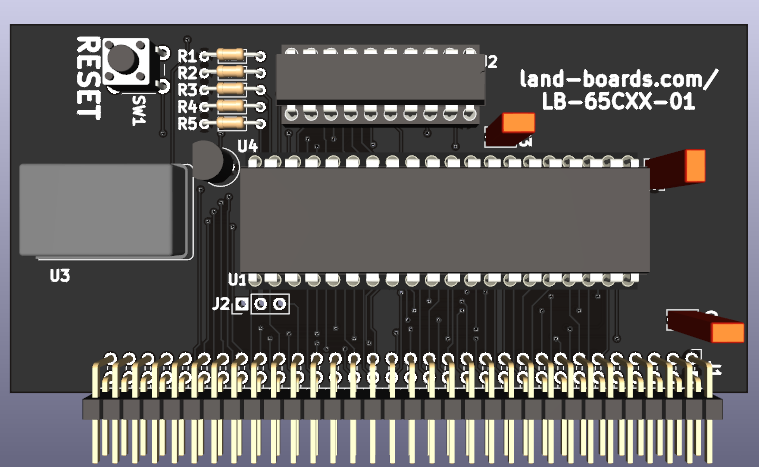

Revision as of 23:55, 18 August 2024

Contents

Features

- 65C02 or 65C816 CPU

- 2 MHz (typical) Oscillator on card

- Reset switch/power monitor

- Address decoder PLD drives RAM/ROM/IO chip selects

- 100x50mm card

Design

Memory Map

0x0000-0x7FFF - 32KB SRAM 0x8000-0x8FFF - 4KB I/O space 0x9000-0xBFFF - 12 KB SRAM (Using 128KB SRAM) 0xC000-0xFFFF - 16KB EPROM space

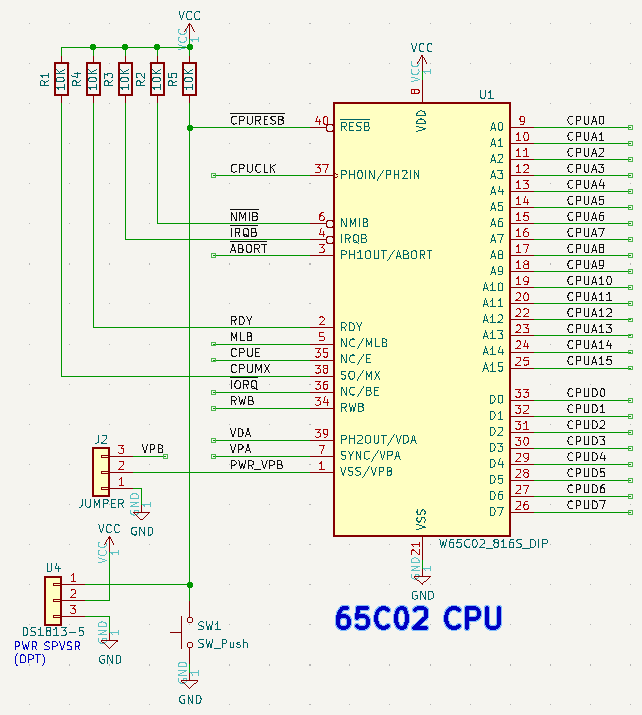

CPU

- 65C02 or 65C816 CPU

- 2 MHz

- Install jumper J2:1-2 if CPU is not a WDC 65C02 or WDC 65C816

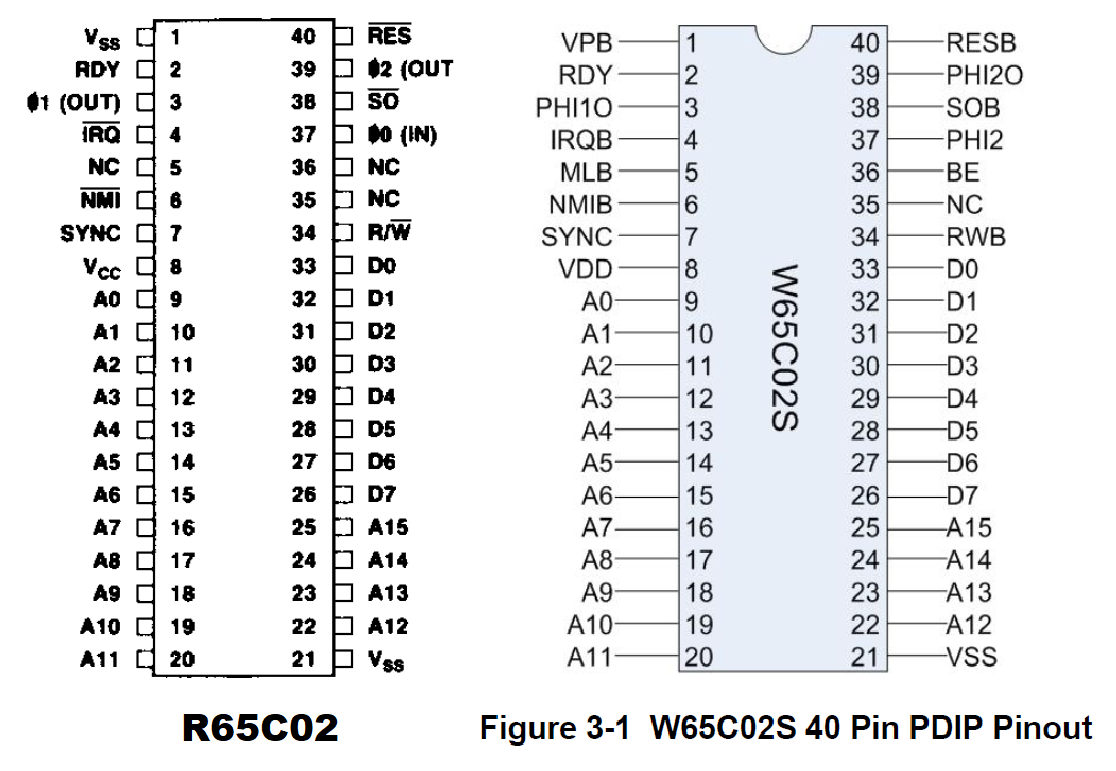

R65C02 vs W65C02 CPUs

R65C02 vs W65C02 pin differences

- Pin 1

- R65C02 = VSS J2:1-2

- W65C02 = VPB J2:2-3 - Vector Pull

- Pin 5

- R65C02 = NC

- W65C02 = MLB - Memory Lock

- Pin 36

- R65C02 = NC

- W65C02 = BE - Bus Enable

Oscillator

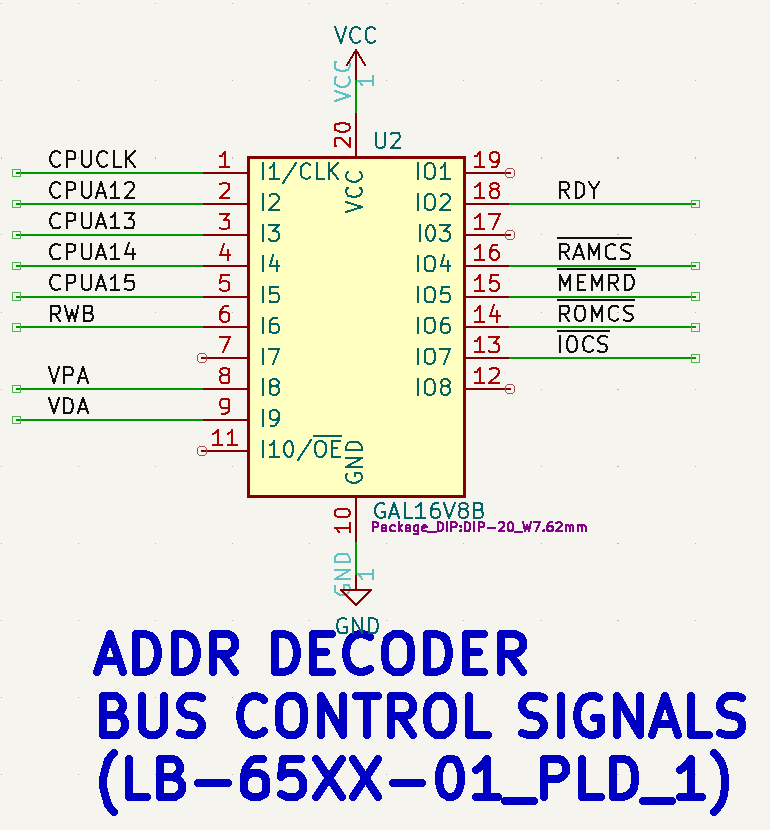

PLD

PLD Listing

Name LB-65CXX-01_PLD; Partno ATF16V8B; Date 08/18/24; Revision 01; Designer DOUG G; Company LAND BOARDS LLC; Assembly LB65CXX01_U2; Location Rustbelt, US; Device G16V8; /* 65C816 Control */ /* Control inputs */ PIN 1 = CLK; PIN 2 = CPUA12; PIN 3 = CPUA13; PIN 4 = CPUA14; PIN 5 = CPUA15; PIN 6 = CPUREAD; PIN 8 = VPA; PIN 9 = VDA; /* Counter data inputs */ PIN 13 = !IOCS; PIN 14 = !ROMCS; PIN 15 = !MEMRD; PIN 16 = !RAMCS; PIN 18 = RDY; RAMCS = !CPUA15 & VDA /* 0x0000-0x7FFF (32KB/64KB SRAM) */ # CPUA15 & !CPUA14 & !CPUA13 & CPUA12 & VDA /* 0x9000-0x9FFF (128KB SRAM) */ # CPUA15 & !CPUA14 & CPUA13 & VDA; /* 0xA000-0xBFFF (128KB SRAM) */ IOCS = CPUA15 & !CPUA14 & !CPUA13 & !CPUA12 & VDA; /* 0x8000-0x8FFF (4KB space) */ ROMCS = CPUA15 & CPUA14 & CPUREAD & VDA; /* 0xC000-0xFFFF (16KB space) */ MEMRD = CPUREAD & VDA; /* RDY = VPA # VDA; */

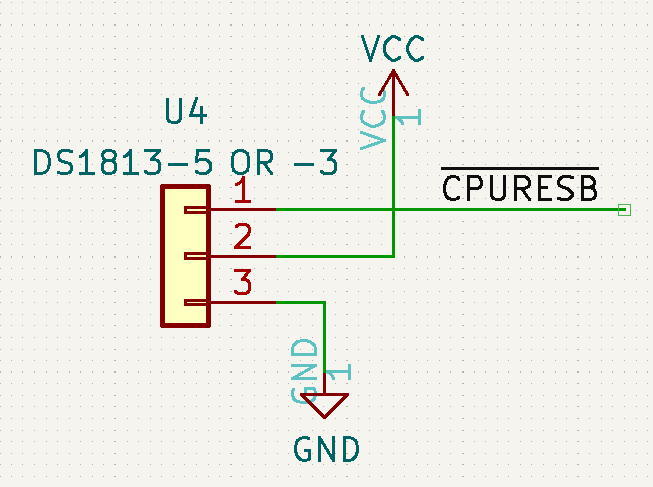

Reset Controller

- DS1813-5 Reset Controller

- 5V Power Monitor

- Reset controller

- Reset pushbutton to ground

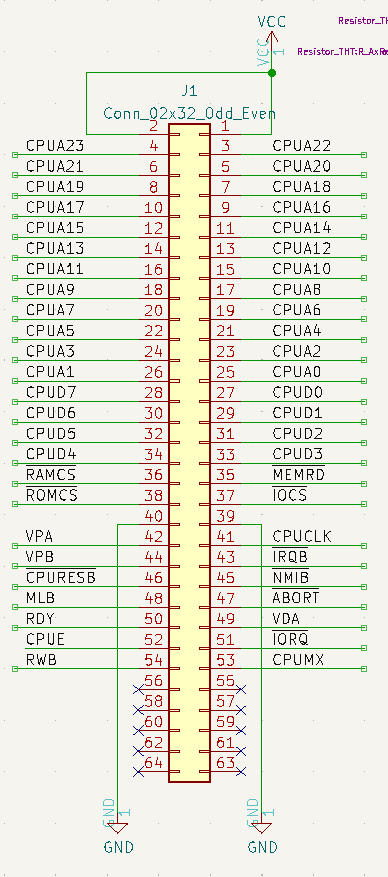

Backplane connector

RAMCS = !CPUA15 & VDA /* 0x0000-0x7FFF (32KB/64KB SRAM) */

- CPUA15 & !CPUA14 & !CPUA13 & CPUA12 & VDA /* 0x9000-0x9FFF (128KB SRAM) */

- CPUA15 & !CPUA14 & CPUA13 & VDA; /* 0xA000-0xBFFF (128KB SRAM) */

IOCS = CPUA15 & !CPUA14 & !CPUA13 & !CPUA12 & VDA; /* 0x8000-0x8FFF (4KB space) */

ROMCS = CPUA15 & CPUA14 & CPUREAD & VDA; /* 0xC000-0xFFFF (16KB space) */