Difference between revisions of "LB-68B50-01"

Jump to navigation

Jump to search

Blwikiadmin (talk | contribs) (→Rev 1) |

Blwikiadmin (talk | contribs) |

||

| Line 22: | Line 22: | ||

* Baud Rate Clock (38.4k baud oscillator) | * Baud Rate Clock (38.4k baud oscillator) | ||

| − | === XIAO RP2040 CPU === | + | === XIAO RP2040 CPU - Rev 1 === |

| + | |||

| + | * Fatal flaw, can't use the RP2040 since the UART voltages are 5V and the RP2040 doesn't work at 5V | ||

[[file:LB-68B50-01_RP2040.PNG]] | [[file:LB-68B50-01_RP2040.PNG]] | ||

Revision as of 22:07, 23 August 2024

Contents

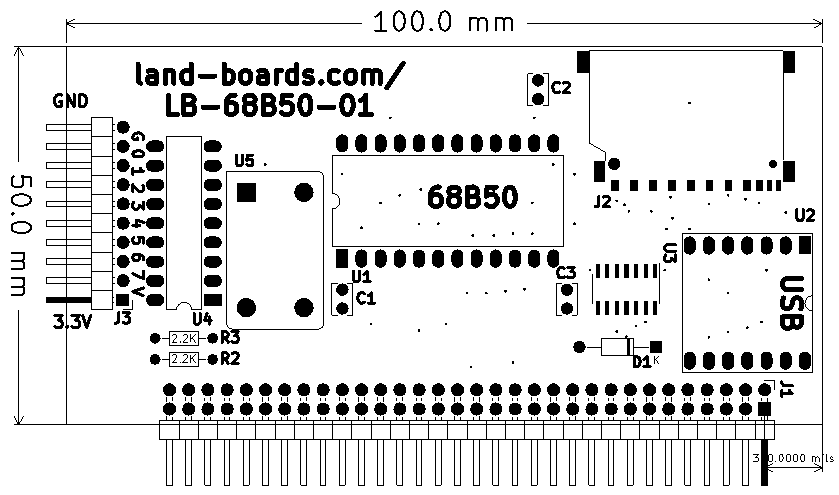

Features

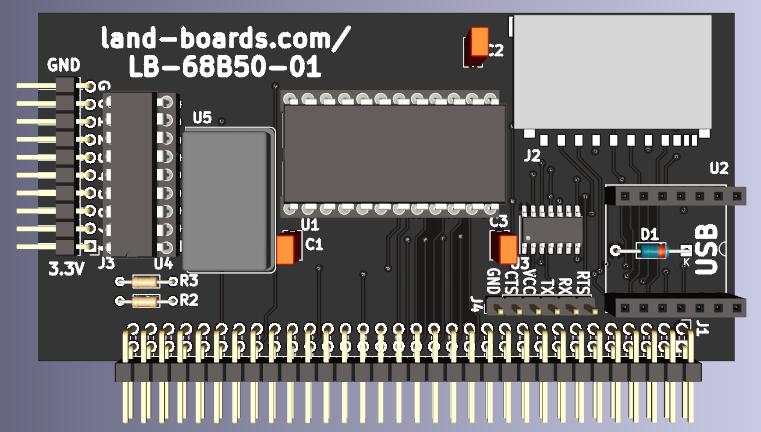

- Serial/Parallel I/O Card

- 68B50 UART

- 1.8432 MHz oscillator

- Baud Rate Clock (38.4k baud oscillator)

- XIAO RP2040 CPU

- USB/Serial

- 8-bit parallel port expander

- SD card

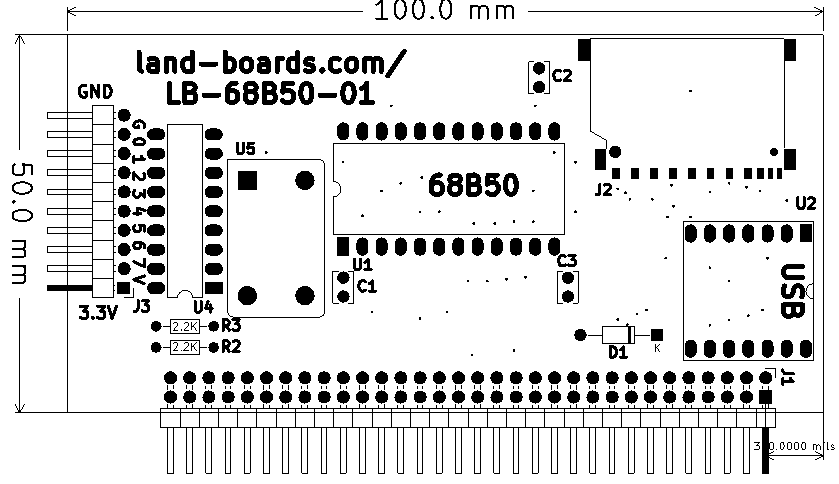

- 100x50mm card

Design

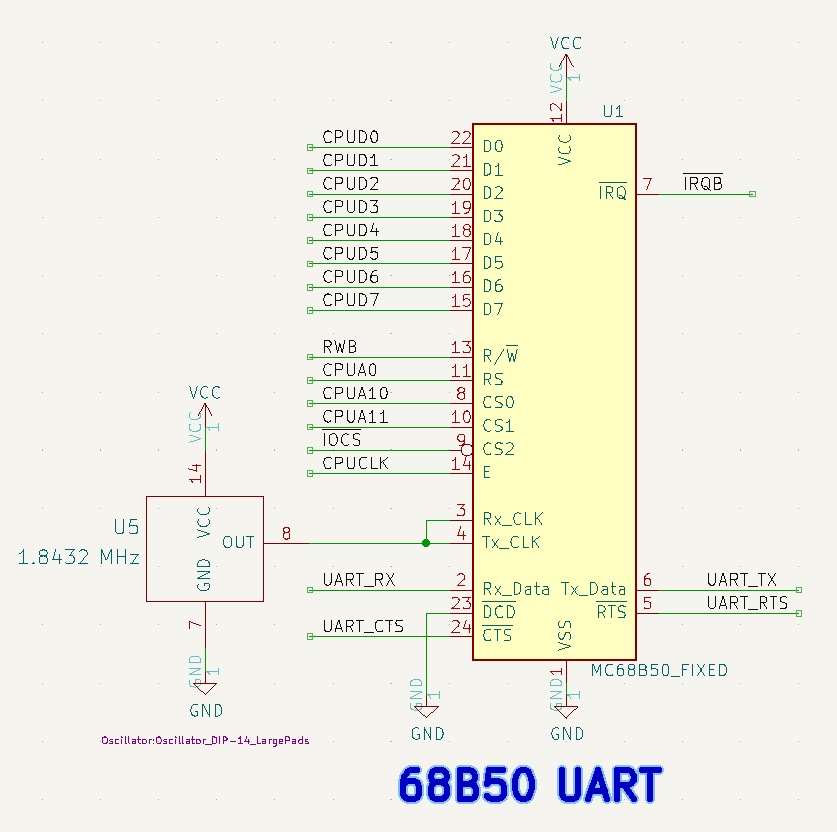

ACIA

- 68B50 UART

- Baud Rate Clock (38.4k baud oscillator)

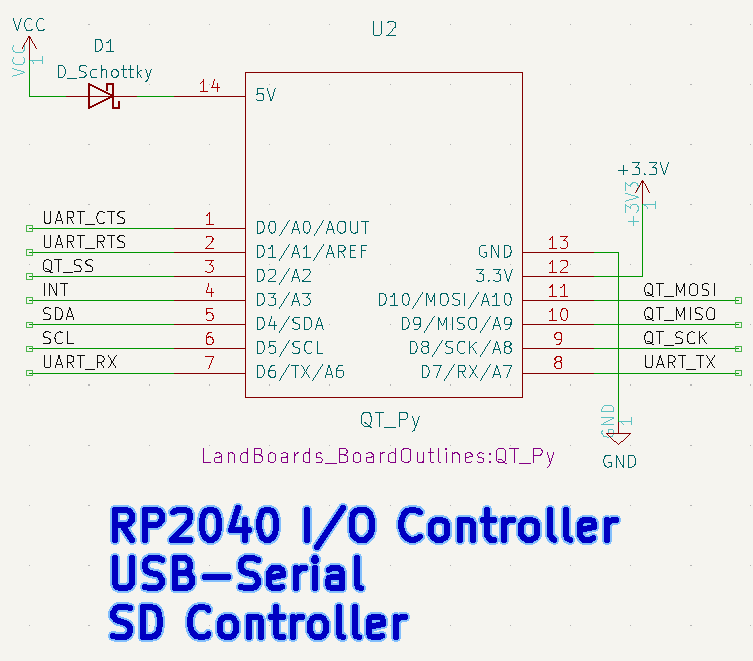

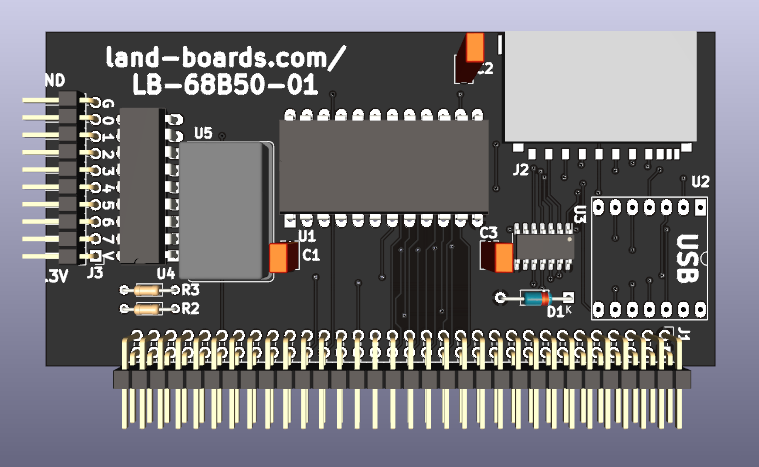

XIAO RP2040 CPU - Rev 1

- Fatal flaw, can't use the RP2040 since the UART voltages are 5V and the RP2040 doesn't work at 5V

- USB/Serial

- Drive SPI I2C 8-bit parallel port expander

- SD card

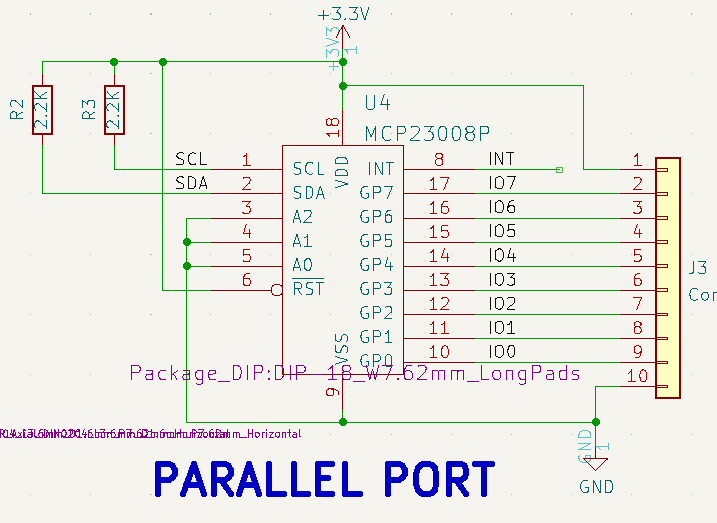

Parallel I/O Port

- 3.3V levels

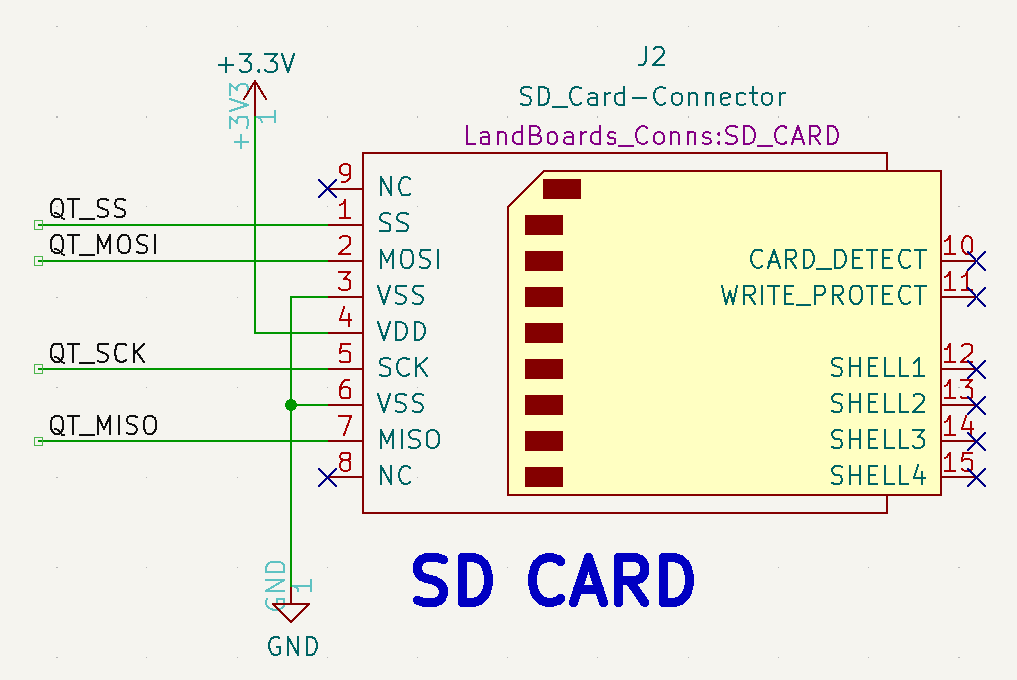

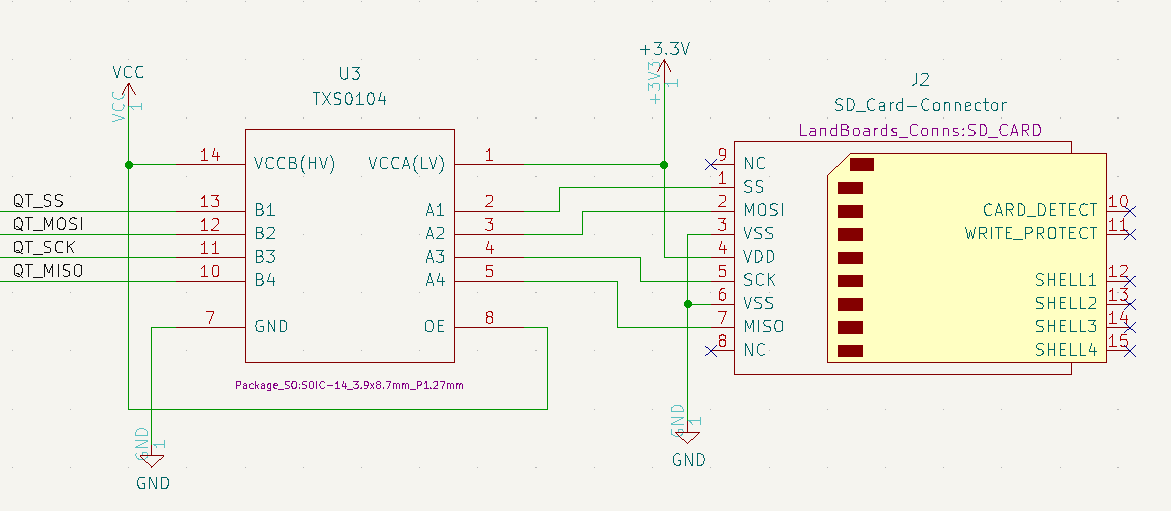

SD Card (Rev 2)

SD Card (Rev1)

- Need to not install level translators

- Need to short across the SD card lines

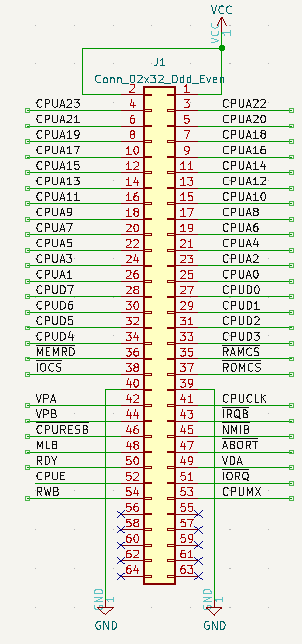

Backplane

Mechanicals

Rev 2

- Move J3 GND, VCC silkscreen over

Rev 1

Checkout

Rev 2

- Removed U2 voltage translator

- Lift pin U1-8

- Lift pin U1-10

- Connect U1-8 to U1-10 to Vcc

Rev 1

- Do not install level translator U3

- Short across the SD card lines

- Jumper U2-13 to U2-2

- Jumper U2-12 to U2-3

- Jumper U2-11 to U2-4

- Jumper U2-10 to U2-5

- Cut etch U1-8

- Cut etch U1-10

- Add jumper U1-8 to U1-10 to U1-12

- Cut etch U1-14 (E pin of ACIA)

- Add jumper U1-14 to J1-49 (VDA)