Difference between revisions of "LB-6802-01"

Jump to navigation

Jump to search

Blwikiadmin (talk | contribs) |

Blwikiadmin (talk | contribs) (→Design) |

||

| Line 14: | Line 14: | ||

== Design == | == Design == | ||

| − | === CPU | + | |

| − | === | + | === CPU === |

| + | |||

| + | [[FILE:LB-6802-01_CPU.PNG]] | ||

| + | |||

| + | === Power Supervisor/Reset === | ||

| + | |||

| + | [[FILE:LB-6802-01_RESET_PWR_SUPER.PNG]] | ||

| + | |||

=== PLD === | === PLD === | ||

| + | |||

| + | [[FILE:]] | ||

| + | |||

==== PLD Listing ==== | ==== PLD Listing ==== | ||

| + | |||

| + | [[FILE:LB-6802-01_PLD.PNG]] | ||

| + | |||

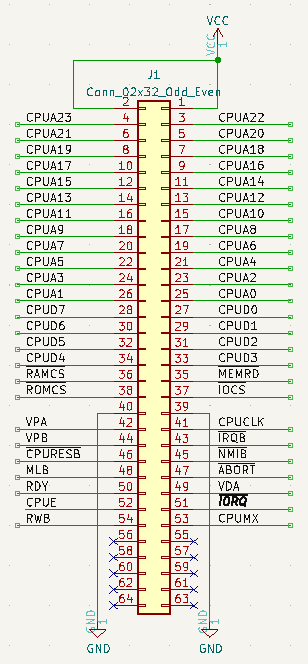

=== Backplane Connector === | === Backplane Connector === | ||

| + | |||

| + | [[FILE:LB-6802-01_BKPL.PNG]] | ||

| + | |||

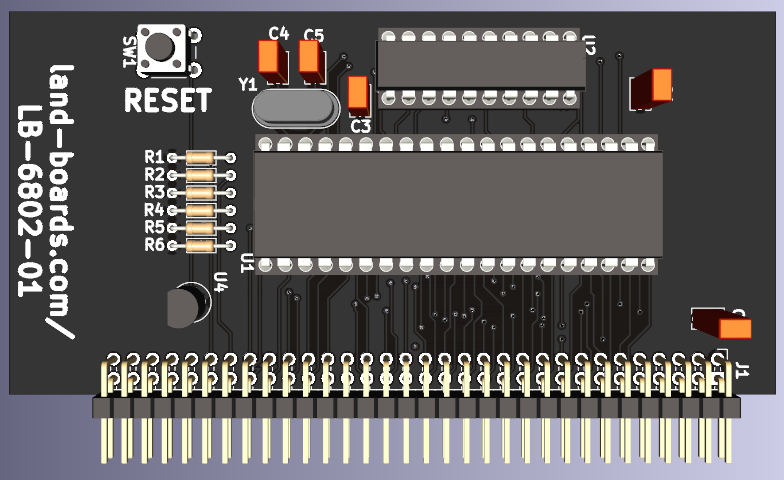

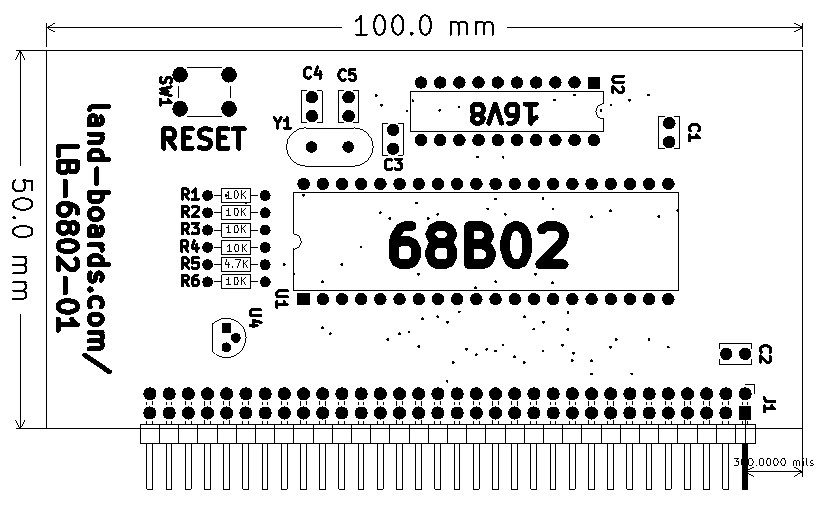

== Mechanicals == | == Mechanicals == | ||

Revision as of 15:18, 24 August 2024

Contents

Features

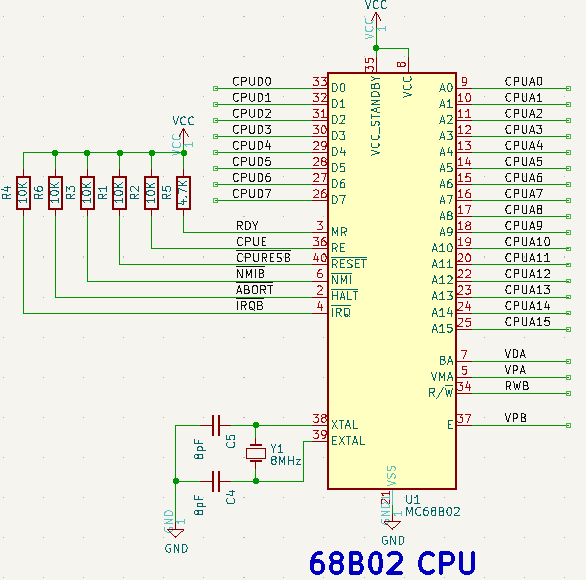

- 68B02 CPU

- 1.8432 MHz clock

- MC6802 is fully compatible with MC6800 but without messy two-phase clocking

Memory Map

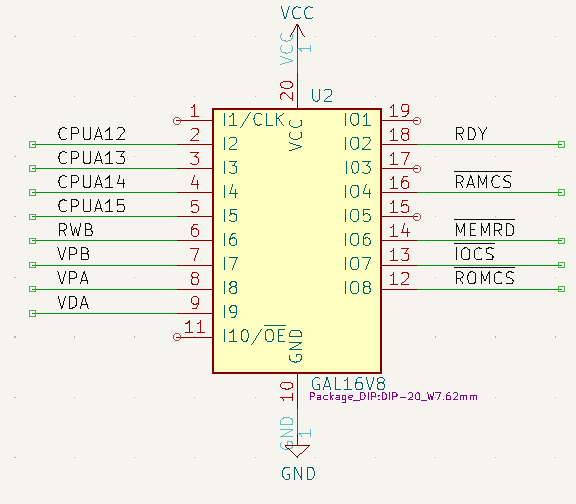

- 0x0000-0x7FFF 32KB SRAM

- 0x8000-0xBFFF Serial (68B50 ACIA)

- 0xC000-0xFFFF 16KB EPROM

Design

CPU

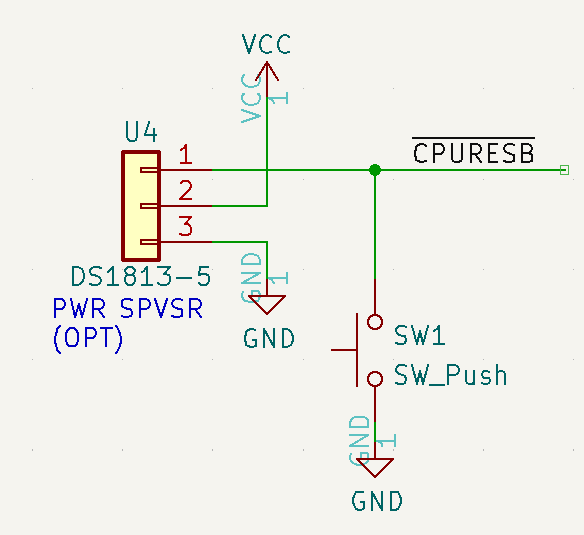

Power Supervisor/Reset

PLD

[[FILE:]]