Difference between revisions of "LB-68B50-02"

Jump to navigation

Jump to search

Blwikiadmin (talk | contribs) |

Blwikiadmin (talk | contribs) (→ACIA) |

||

| Line 13: | Line 13: | ||

=== ACIA === | === ACIA === | ||

| + | |||

* 68B50 UART | * 68B50 UART | ||

* Baud Rate Clock (115,200 baud oscillator) | * Baud Rate Clock (115,200 baud oscillator) | ||

[[file:LB-68B50-02_ACIA-Rev1.PNG]] | [[file:LB-68B50-02_ACIA-Rev1.PNG]] | ||

| + | |||

| + | === PLD === | ||

| + | |||

| + | [[file:LB-68B50-02_U2_PLD.PNG]] | ||

=== J2 - FTDI Header) === | === J2 - FTDI Header) === | ||

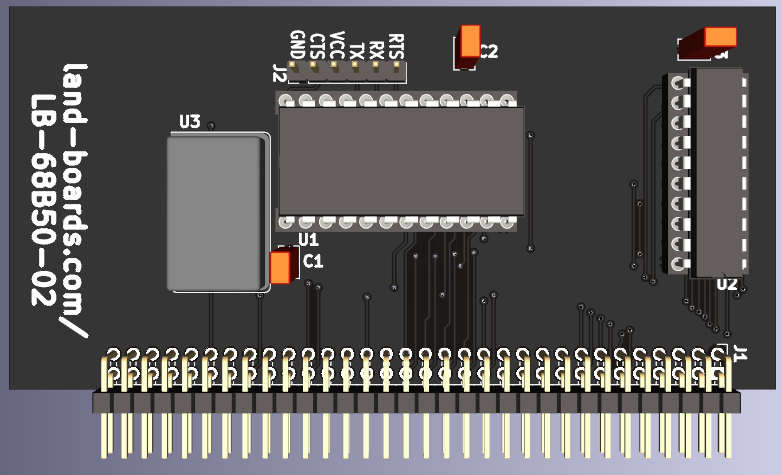

Revision as of 23:56, 24 August 2024

Contents

Features

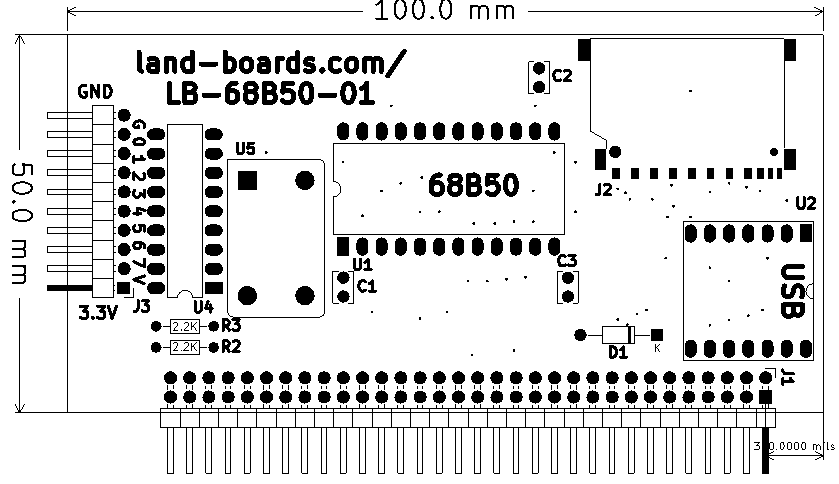

- Serial/Parallel I/O Card

- 68B50 UART

- 1.8432 MHz oscillator

- Baud Rate Clock (115,200 baud oscillator)

- Control PLD

- 100x50mm card

Design

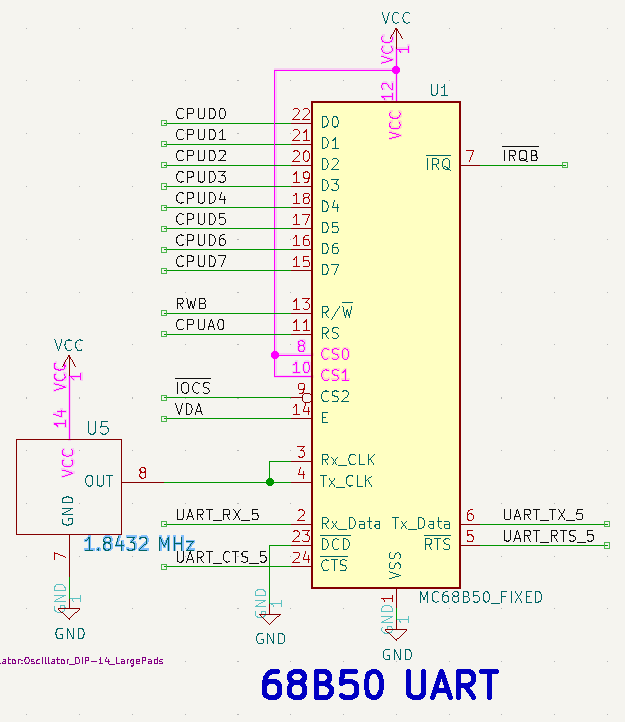

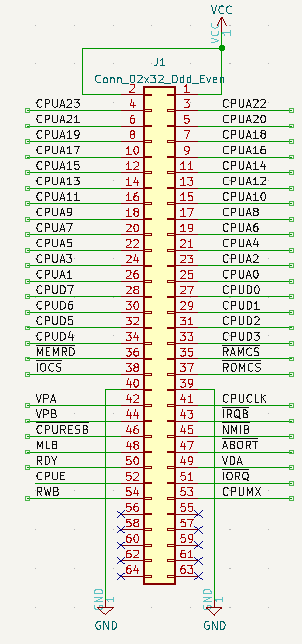

ACIA

- 68B50 UART

- Baud Rate Clock (115,200 baud oscillator)

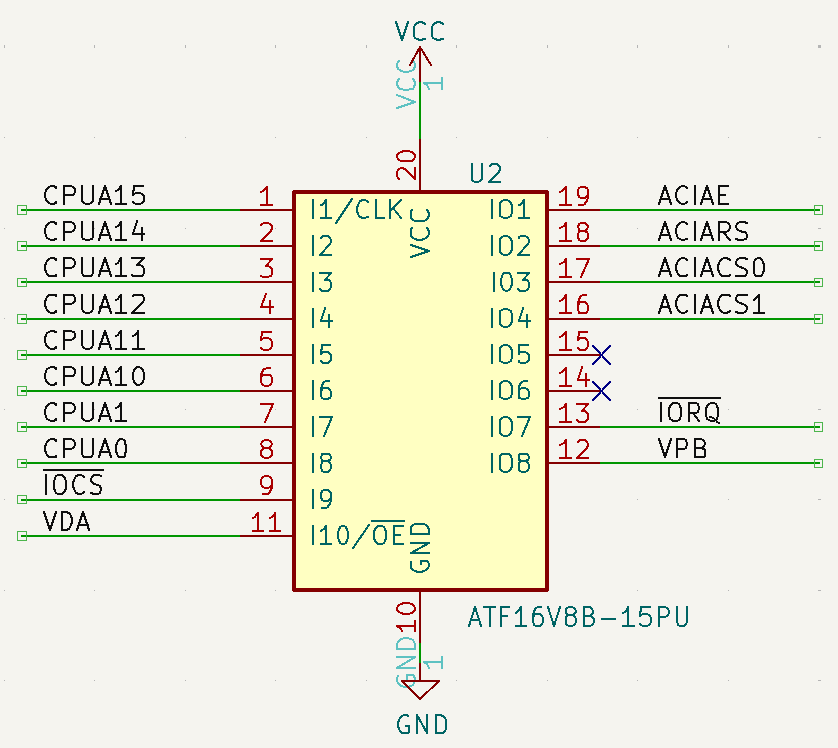

PLD

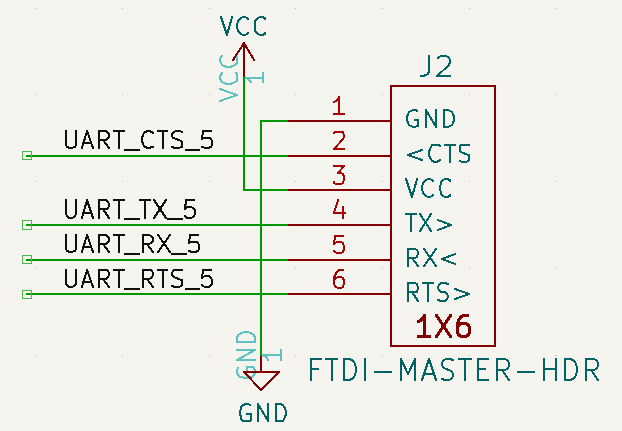

J2 - FTDI Header)

- 5V levels

- Pinout

- GND

- CTS (in)

- VCC

- TX (out)

- RX (in)

- RTS (out)

Backplane

Mechanicals

Rev 2

- Move J3 GND, VCC silkscreen over