Difference between revisions of "LB-68B50-02"

Jump to navigation

Jump to search

Blwikiadmin (talk | contribs) (→Rev 1) |

Blwikiadmin (talk | contribs) (→PLD) |

||

| Line 22: | Line 22: | ||

[[file:LB-68B50-02_U2_PLD.PNG]] | [[file:LB-68B50-02_U2_PLD.PNG]] | ||

| + | |||

| + | ==== PLD Listing ==== | ||

| + | |||

| + | <pre> | ||

| + | Name LB-65CXX-01_PLD; | ||

| + | Partno ATF16V8B; | ||

| + | Date 08/19/24; | ||

| + | Revision 01; | ||

| + | Designer DOUG G; | ||

| + | Company LAND BOARDS LLC; | ||

| + | Assembly LB65CXX01_U2; | ||

| + | Location Rustbelt, US; | ||

| + | Device G16V8; | ||

| + | |||

| + | /* | ||

| + | 65C816 Control | ||

| + | */ | ||

| + | |||

| + | /* Control inputs */ | ||

| + | PIN 1 = CPUA15; | ||

| + | PIN 2 = CPUA14; | ||

| + | PIN 3 = CPUA13; | ||

| + | PIN 4 = CPUA12; | ||

| + | PIN 5 = CPUA11; | ||

| + | PIN 6 = CPUA10; | ||

| + | PIN 7 = CPUA1; | ||

| + | PIN 8 = CPUA0; | ||

| + | PIN 9 = !IOCS; | ||

| + | PIN 11 = VDA; | ||

| + | PIN 12 = VPB; | ||

| + | PIN 14 = !IORQ; | ||

| + | |||

| + | /* Address Decode and Chip Select outputs */ | ||

| + | PIN 16 = ACIACS1; | ||

| + | PIN 17 = ACIACS0; | ||

| + | PIN 18 = ACIARS; | ||

| + | PIN 19 = ACIAE; | ||

| + | |||

| + | ACIACS1 = VPB; | ||

| + | |||

| + | ACIACS0 = VPB; | ||

| + | |||

| + | ACIARS = CPUA0; | ||

| + | |||

| + | ACIAE = VPB; | ||

| + | </pre> | ||

=== J2 - FTDI Header) === | === J2 - FTDI Header) === | ||

Revision as of 00:11, 25 August 2024

Contents

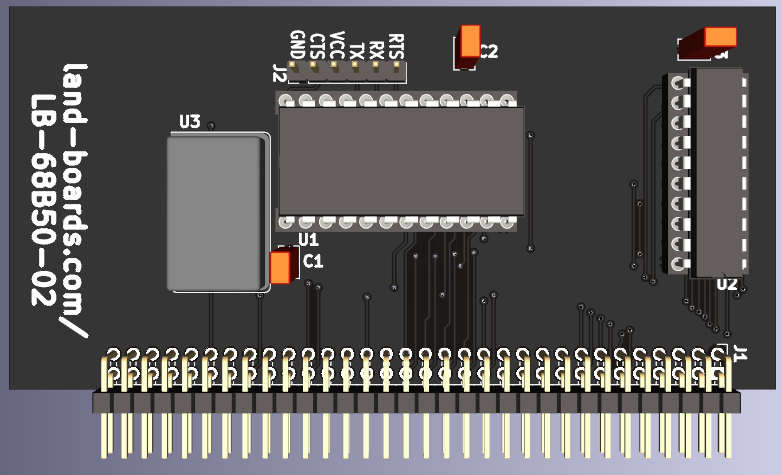

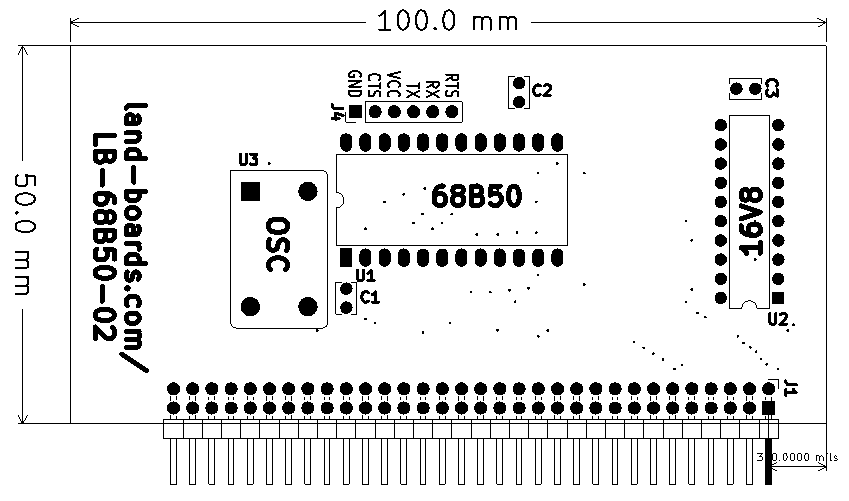

Features

- Serial/Parallel I/O Card

- 68B50 UART

- 1.8432 MHz oscillator

- Baud Rate Clock (115,200 baud oscillator)

- Control PLD

- 100x50mm card

Design

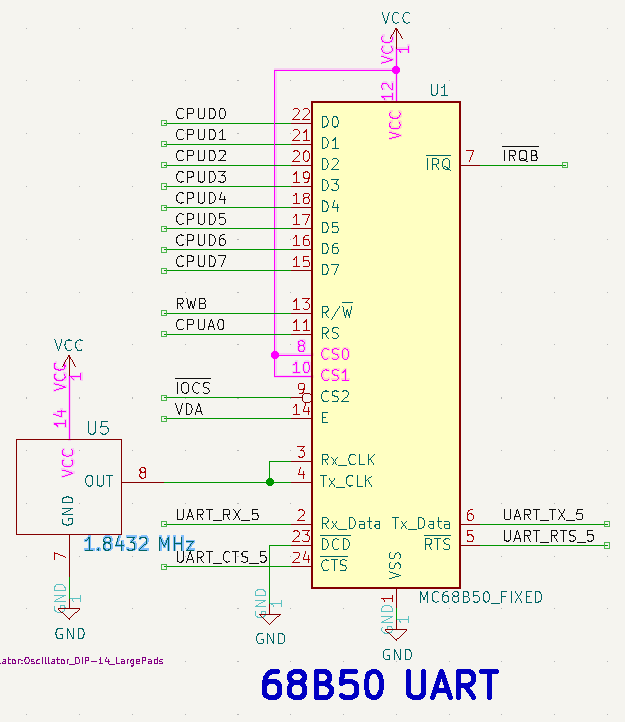

ACIA

- 68B50 UART

- Baud Rate Clock (115,200 baud oscillator)

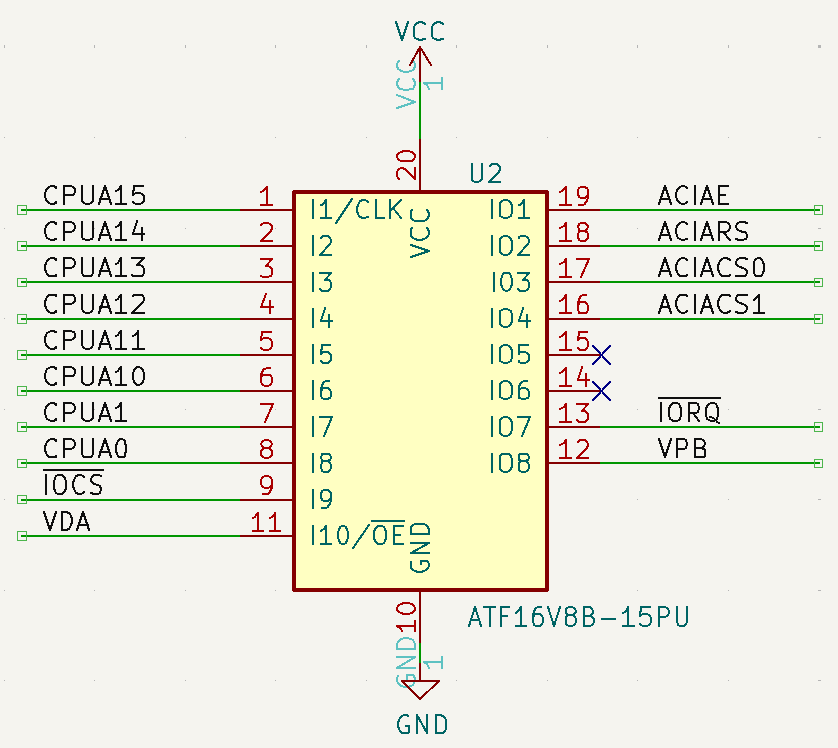

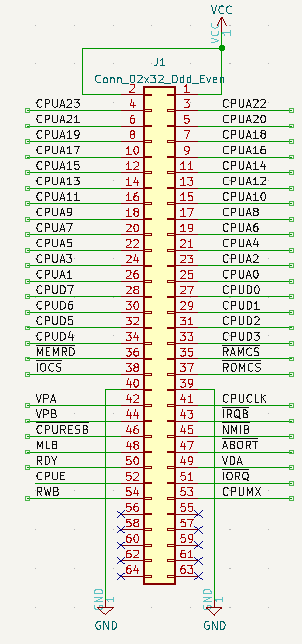

PLD

PLD Listing

Name LB-65CXX-01_PLD; Partno ATF16V8B; Date 08/19/24; Revision 01; Designer DOUG G; Company LAND BOARDS LLC; Assembly LB65CXX01_U2; Location Rustbelt, US; Device G16V8; /* 65C816 Control */ /* Control inputs */ PIN 1 = CPUA15; PIN 2 = CPUA14; PIN 3 = CPUA13; PIN 4 = CPUA12; PIN 5 = CPUA11; PIN 6 = CPUA10; PIN 7 = CPUA1; PIN 8 = CPUA0; PIN 9 = !IOCS; PIN 11 = VDA; PIN 12 = VPB; PIN 14 = !IORQ; /* Address Decode and Chip Select outputs */ PIN 16 = ACIACS1; PIN 17 = ACIACS0; PIN 18 = ACIARS; PIN 19 = ACIAE; ACIACS1 = VPB; ACIACS0 = VPB; ACIARS = CPUA0; ACIAE = VPB;

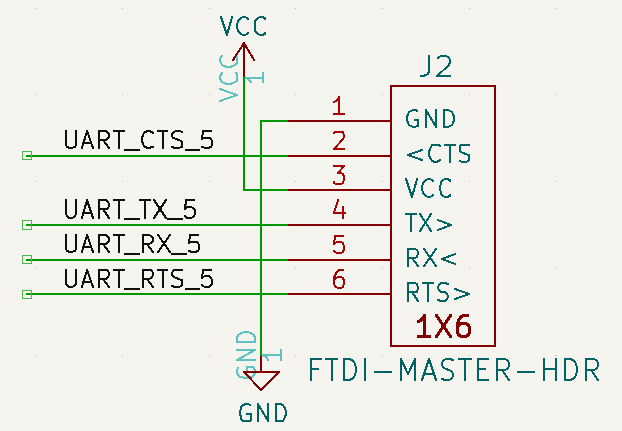

J2 - FTDI Header)

- 5V levels

- Pinout

- GND

- CTS (in)

- VCC

- TX (out)

- RX (in)

- RTS (out)