Difference between revisions of "LB-6802-01"

Jump to navigation

Jump to search

Blwikiadmin (talk | contribs) (→CPU) |

Blwikiadmin (talk | contribs) |

||

| Line 88: | Line 88: | ||

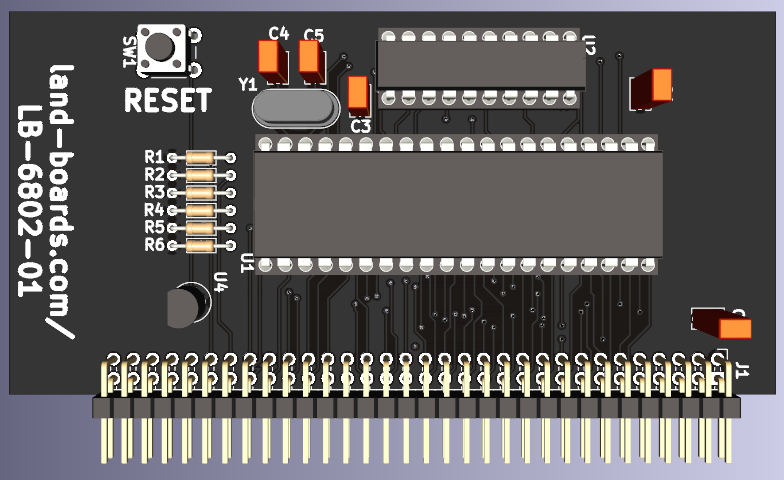

[[FILE:LB-6802-01_BKPL.PNG]] | [[FILE:LB-6802-01_BKPL.PNG]] | ||

| + | |||

| + | == Software == | ||

| + | |||

| + | * [https://archive.org/details/How_to_Program_and_Interface_the_6800_By_Andrew_C_Staugaard_1980/page/260/mode/2up How to Program and Interface the 6800 By Andrew C. Staugaard, Jr. 1980] | ||

| + | * [http://www.8bit-era.cz/6800.html#addr8-desc 6800 instruction set] | ||

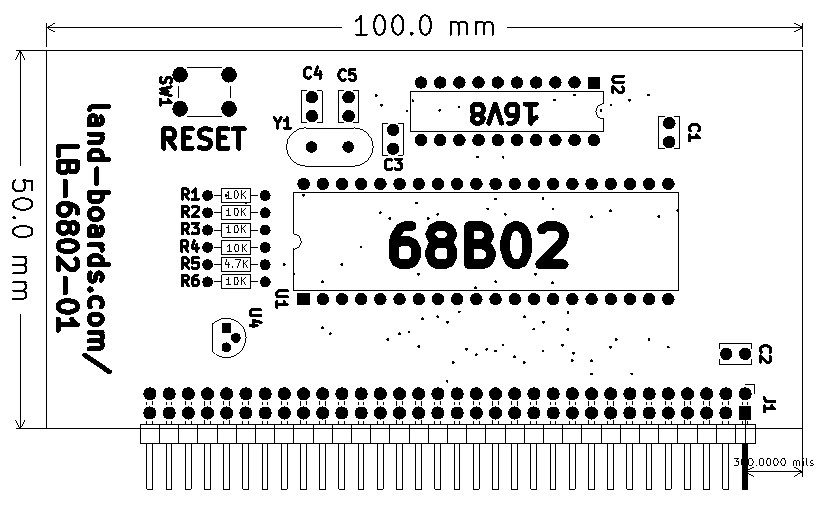

== Mechanicals == | == Mechanicals == | ||

Revision as of 16:52, 31 August 2024

Contents

Features

- 68B02 CPU

- 1.8432 MHz clock

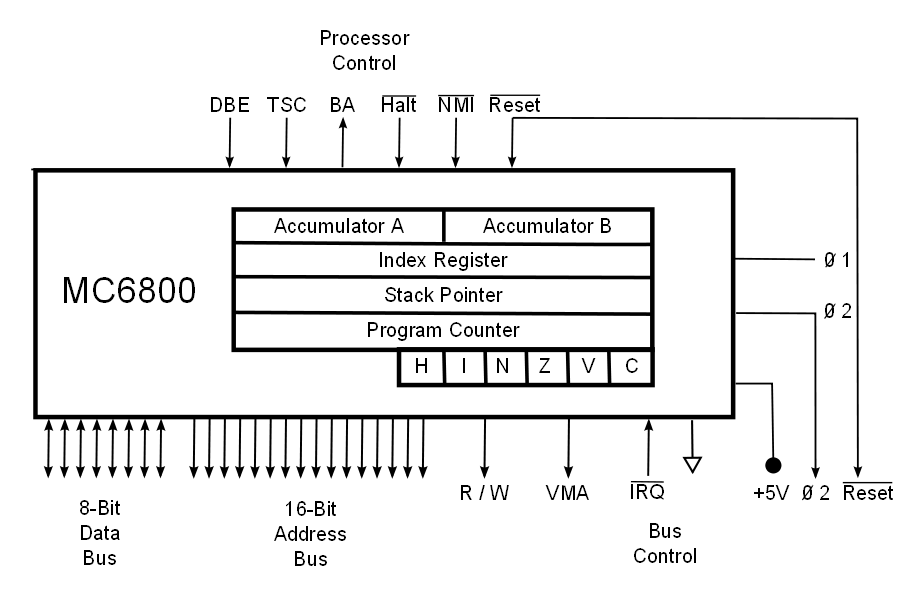

- MC6802 is fully compatible with MC6800 but without messy two-phase clocking

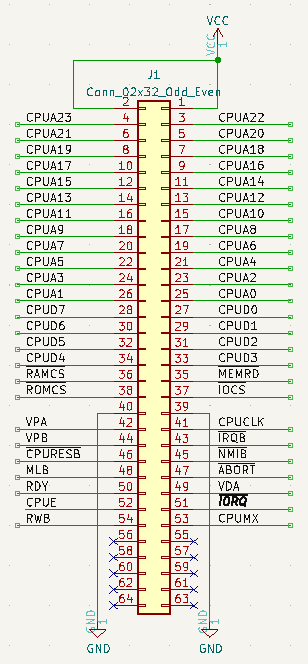

Memory Map

- 0x0000-0x7FFF 32KB SRAM

- 0x8000-0xBFFF Serial (68B50 ACIA)

- 0xC000-0xFFFF 16KB EPROM

Design

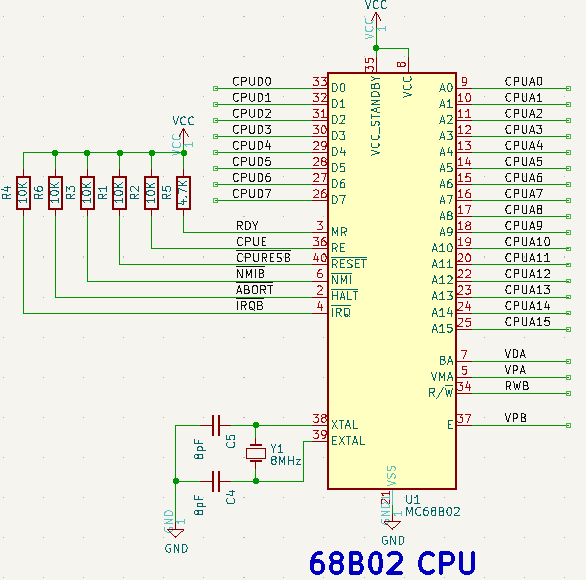

CPU

MC6800 Block Diagram

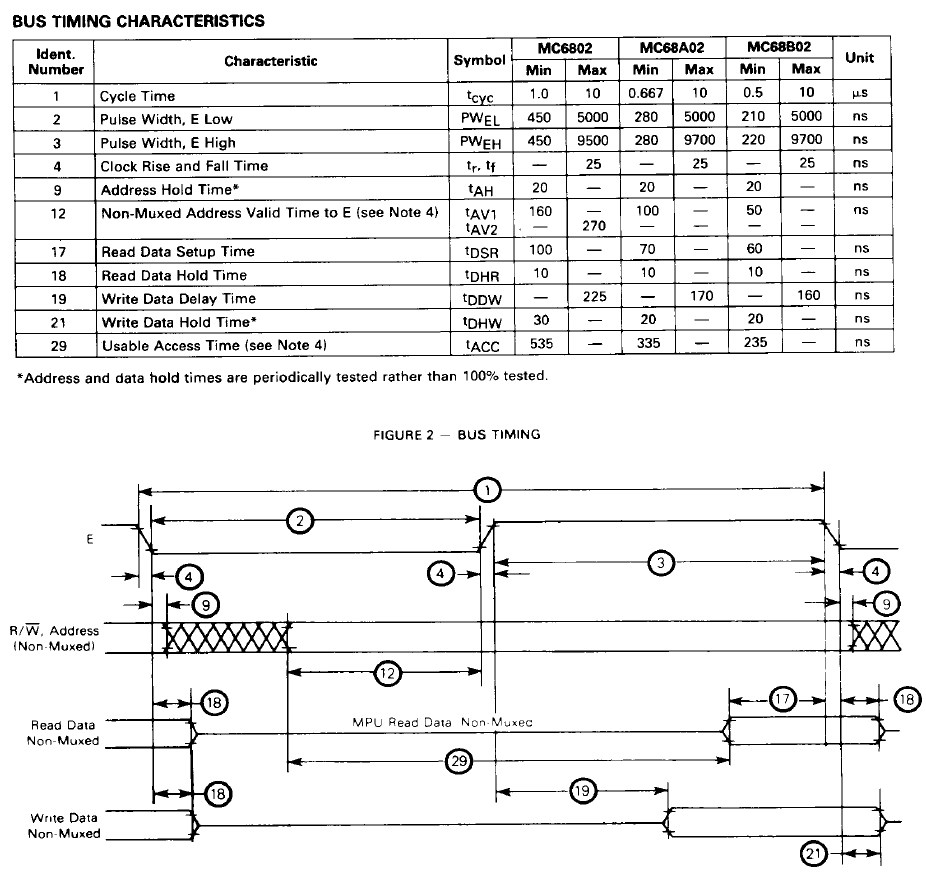

Bus Timing

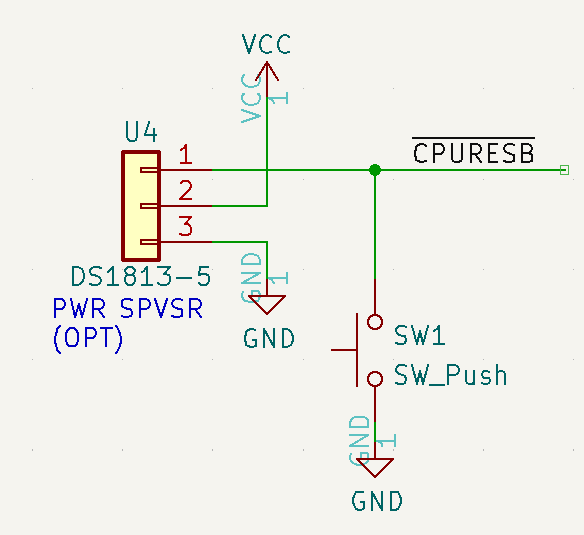

Power Supervisor/Reset

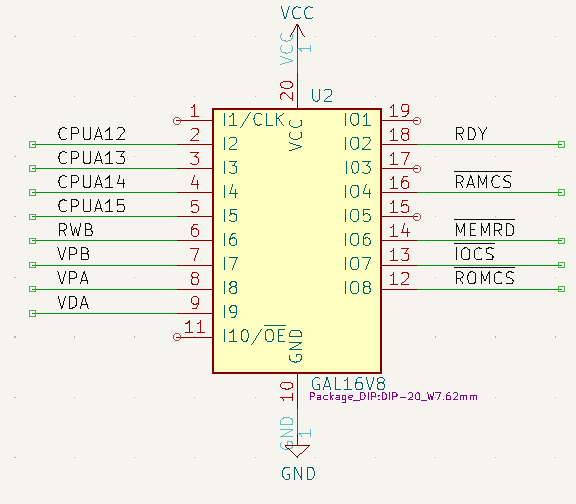

PLD

- ATF16V8B part

- TL866ii Plus Programmer

PLD Listing

Name LB-6802-01_PLD; Partno ATF16V8B; Date 08/24/24; Revision 01; Designer DOUG G; Company LAND BOARDS LLC; Assembly LB680201_U2; Location Rustbelt, US; Device G16V8; /* */ /* Control inputs */ PIN 1 = CLK; PIN 2 = CPUA12; PIN 3 = CPUA13; PIN 4 = CPUA14; PIN 5 = CPUA15; PIN 6 = CPUREAD; PIN 7 = VPB; /* Added as wire on Rev 1 PCB */ PIN 8 = VPA; PIN 9 = VDA; /* Address Decode and Chip Select outputs */ PIN 12 = !ROMCS; PIN 13 = !IOCS; PIN 14 = !MEMRD; PIN 16 = !RAMCS; PIN 18 = RDY; ROMCS = CPUA15 & CPUA14 & VPB; RAMCS = !CPUA15 & VPB /* 0x0000-0x7FFF 32KB SRAM */ # CPUA15 & !CPUA14 & !CPUA13 & VPB; /* 0x8000-0x9FFF Free (8KB */ IOCS = CPUA15 & !CPUA14 & CPUA13 & VPB; /* 0xA000-0xBFFF Serial (ACIA) */ RDY = VPB; MEMRD = CPUREAD & VPB;