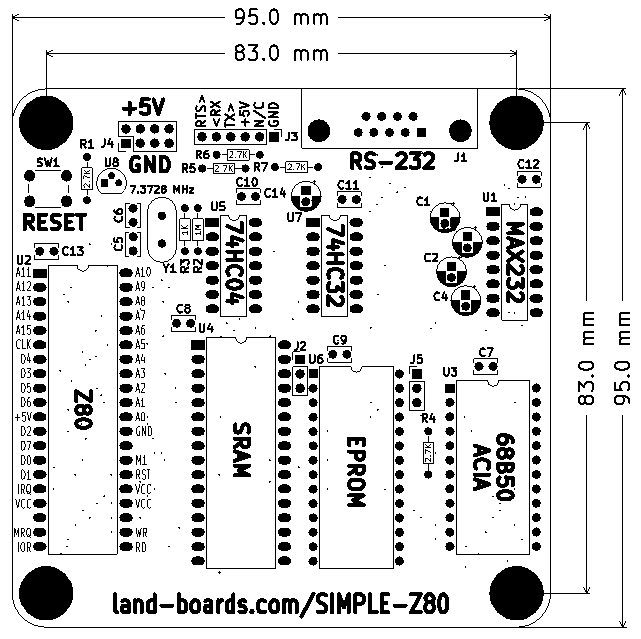

Features

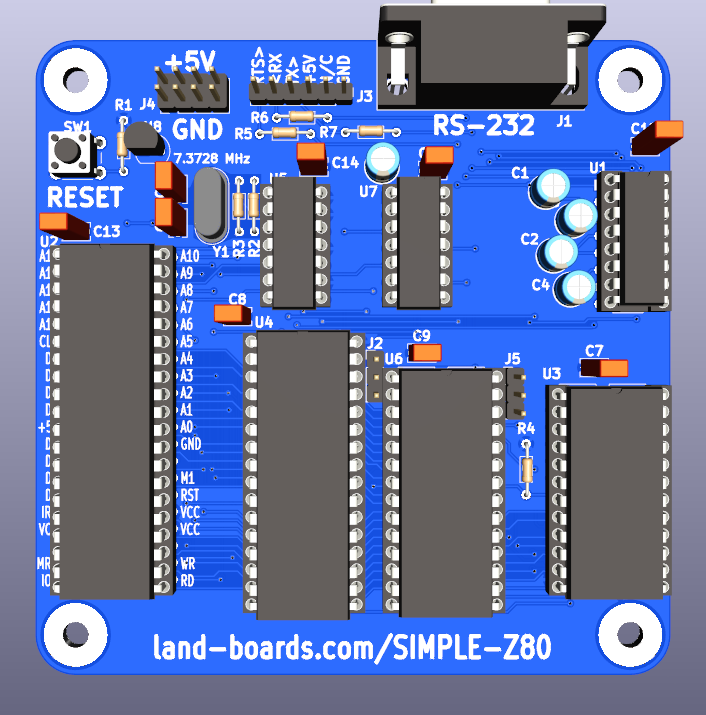

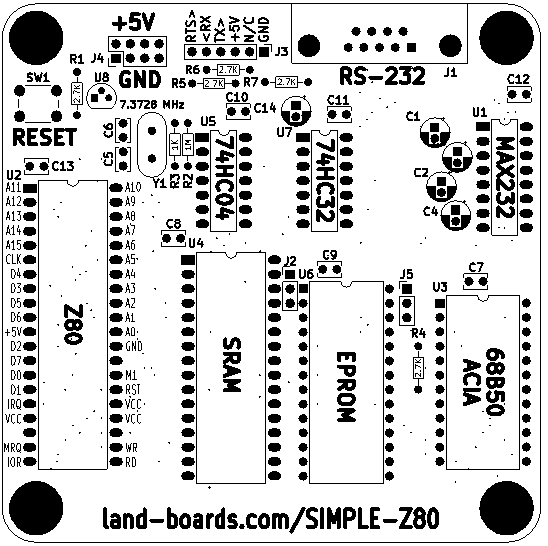

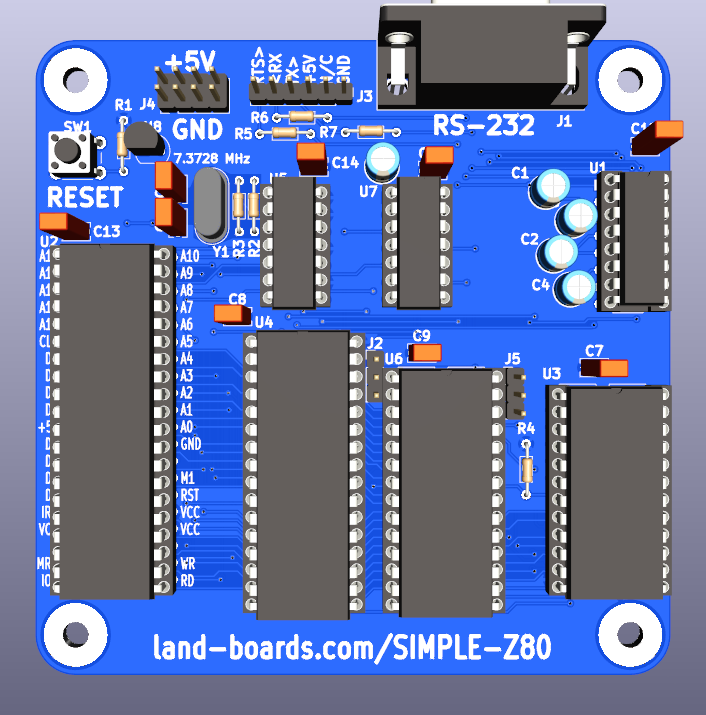

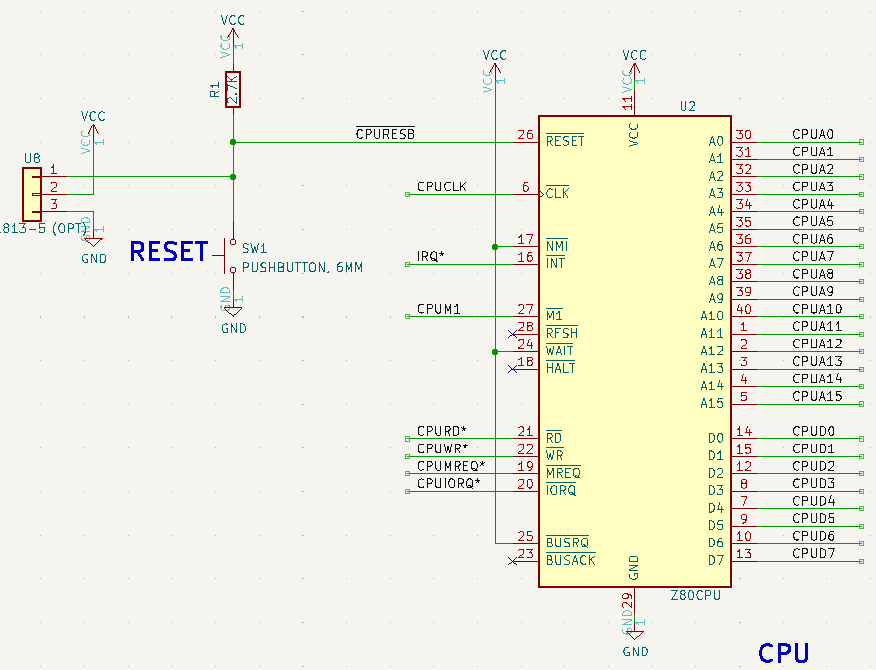

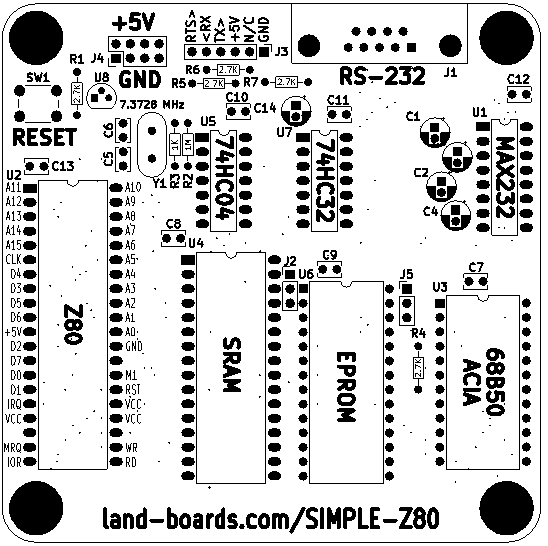

- Build of Grant Searles's Simple Z80 CPU

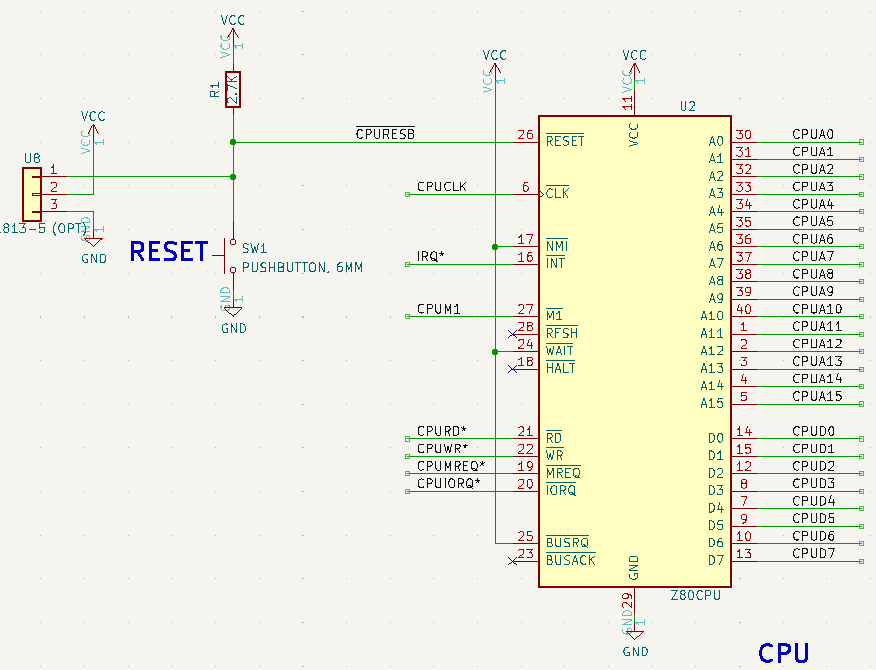

- Z80 CPU

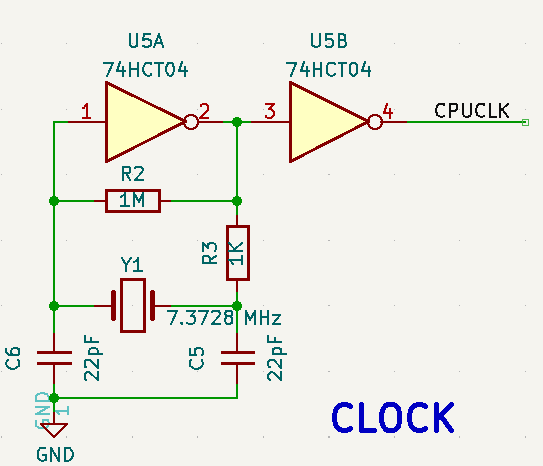

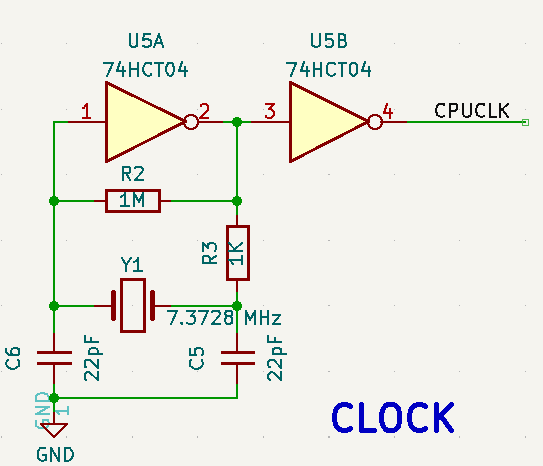

- 7.3728 MHz clock

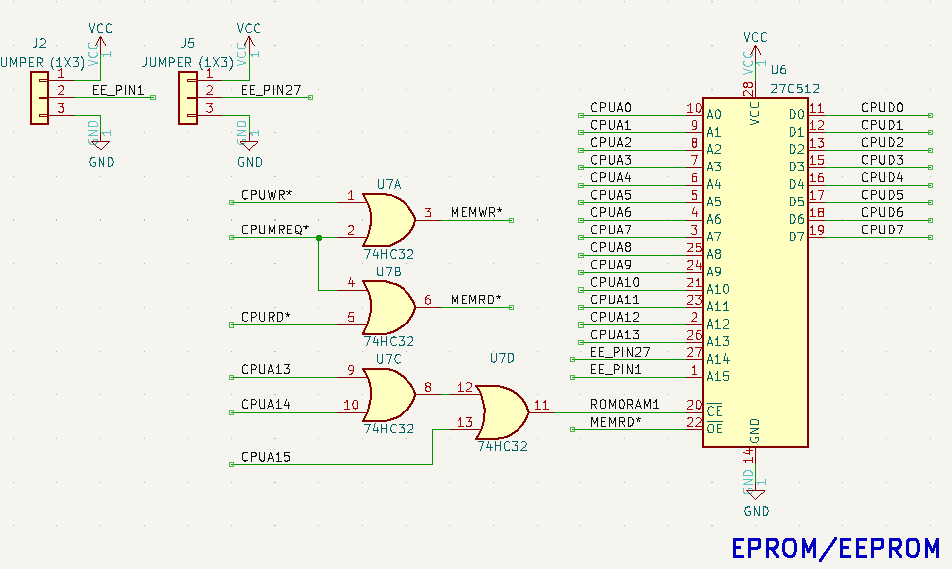

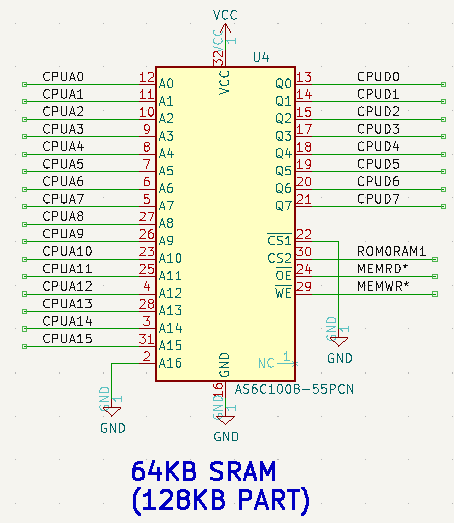

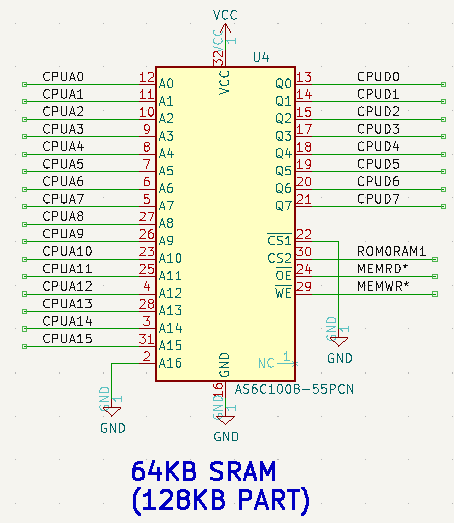

- 56KB SRAM (uses 128KB parts)

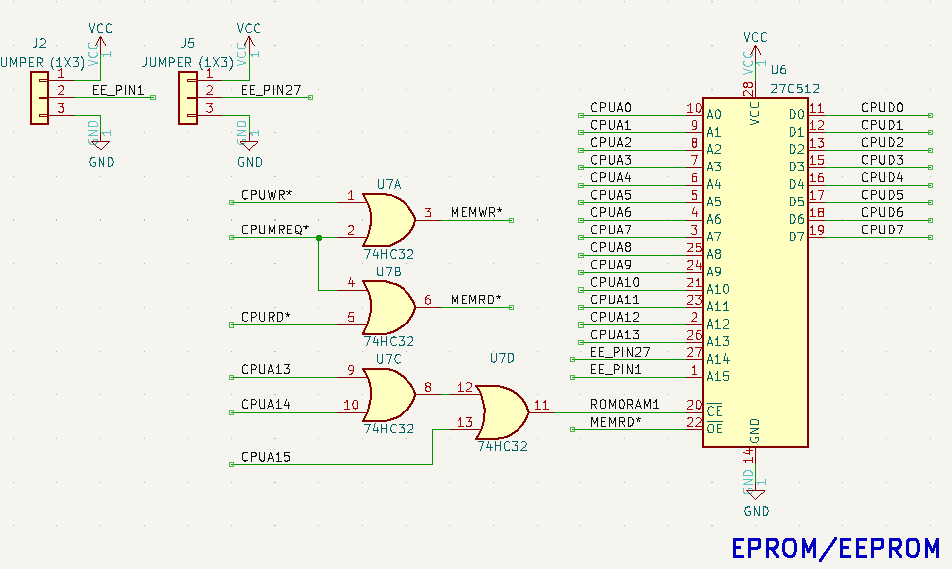

- 8KB EPROM/EEPROM

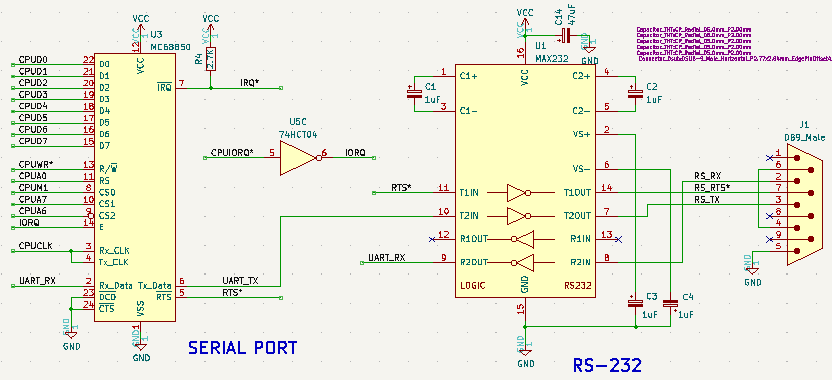

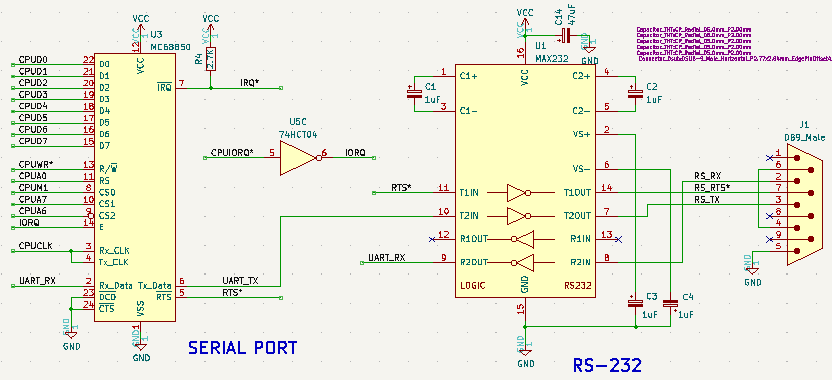

- 68B50 Serial Port (ACIA)

- RS-232 port

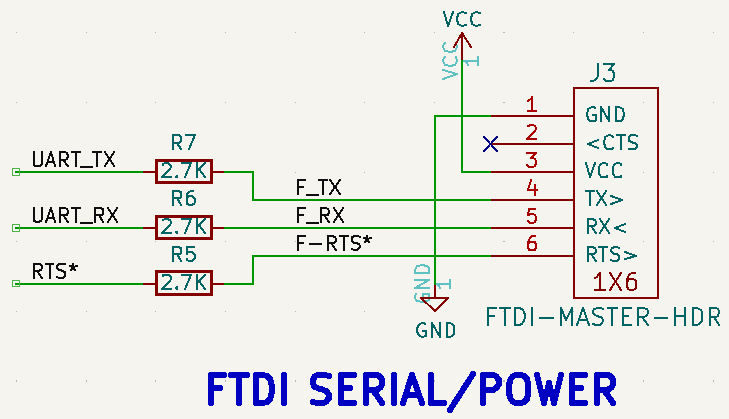

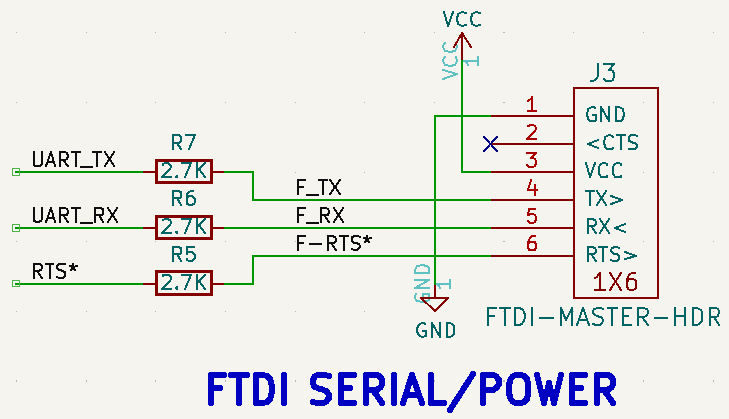

- Header for FTDI

- 115,200 baud

- Reset switch with optional Power Supervisor

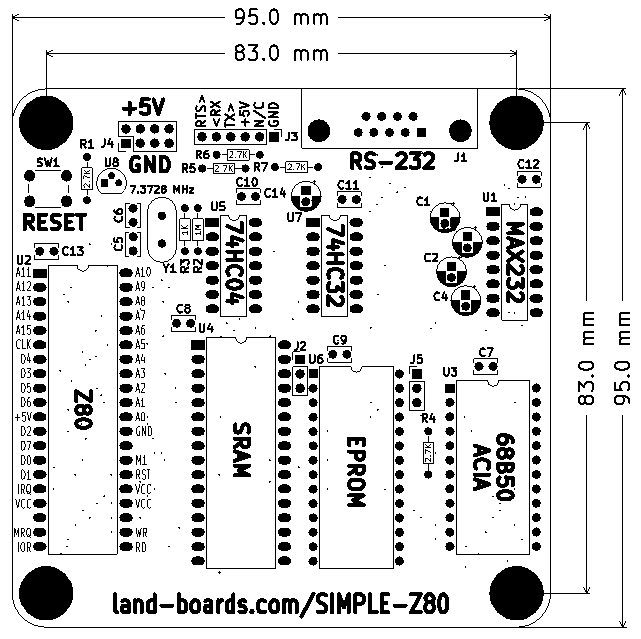

- 95x95mm card

- (4) 6-32 mounting holes

Memory Map

- 0x0000-0x1FFF 8KB ROM

- 0x2000-0xFFFF 56KB SRAM

- I/O

- 0x00-0x7F - Free

- 0x80-0x81 - Serial port (ACIA)

Chip Set

Design

J1 - RS-232 Serial

- N/C

- Receive

- Transmit

- Loop to pin 6

- GND

- Loop to pin 4

- RTS

- N/C

- N/C

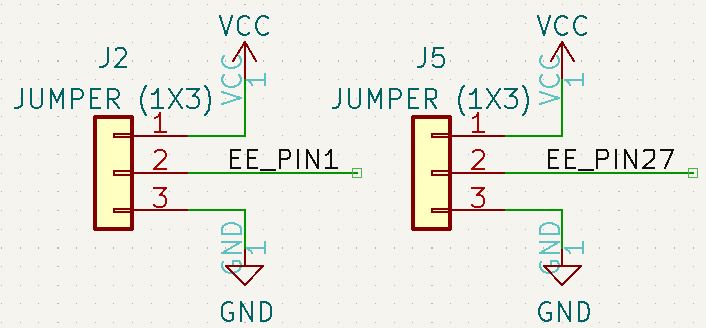

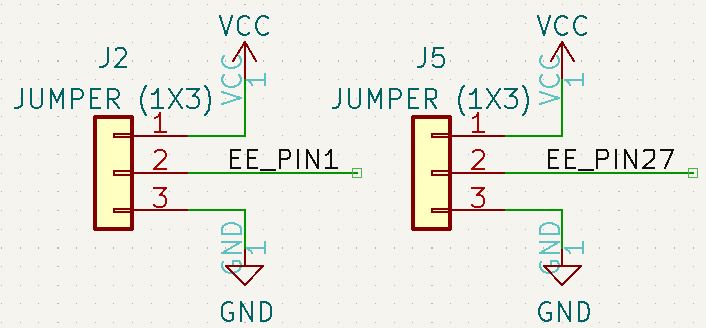

J2/J5 - EPROM/EEPROM Select Jumpers

| 27512

|

27256

|

27128

|

2764

|

28C64

|

PIN

|

|

PIN

|

2764

|

28C64

|

27128

|

27256

|

27512

|

| A15

|

VPP

|

VPP

|

VPP

|

N/C

|

1 (J2)

|

|

28

|

VCC

|

VCC

|

VCC

|

VCC

|

VCC

|

| A12

|

A12

|

A12

|

A12

|

A12

|

2

|

|

27 (J5)

|

PGM

|

WE*

|

PGM

|

A14

|

A14

|

| A7

|

A7

|

A7

|

A7

|

A7

|

3

|

|

26

|

A13

|

N/C

|

A13

|

A13

|

A13

|

| A6

|

A6

|

A6

|

A6

|

A6

|

4

|

|

25

|

A8

|

A8

|

|

A8

|

A8

|

| A5

|

A5

|

A5

|

A5

|

A5

|

5

|

|

24

|

A9

|

A9

|

|

A9

|

A9

|

| A4

|

A4

|

A4

|

A4

|

A4

|

6

|

|

23

|

A11

|

A11

|

|

A11

|

A11

|

| A3

|

A3

|

A3

|

A3

|

A3

|

7

|

|

22

|

OE*

|

OE*

|

|

OE*

|

OE*

|

| A2

|

A2

|

A2

|

A2

|

A2

|

8

|

|

21

|

A10

|

A10

|

|

A10

|

A10

|

| A1

|

A1

|

A1

|

A1

|

A1

|

9

|

|

20

|

CE*

|

CE*

|

|

CE*

|

CE*

|

| A0

|

A0

|

A0

|

A0

|

A0

|

10

|

|

19

|

D7

|

D7

|

|

D7

|

D7

|

| D0

|

D0

|

D0

|

D0

|

D0

|

11

|

|

18

|

D6

|

D6

|

|

D6

|

D6

|

| D1

|

D1

|

D1

|

D1

|

D1

|

12

|

|

17

|

D5

|

D5

|

|

D5

|

D5

|

| D2

|

D2

|

D2

|

D2

|

D2

|

13

|

|

16

|

D4

|

D4

|

|

D4

|

D4

|

| GND

|

GND

|

GND

|

GND

|

GND

|

14

|

|

15

|

D3

|

D3

|

|

D3

|

D3

|

J3 - FTDI / TTL Serial

- GND

- RTS* (out)

- +5V

- Receive (in)

- Transmit (out)

- N/C

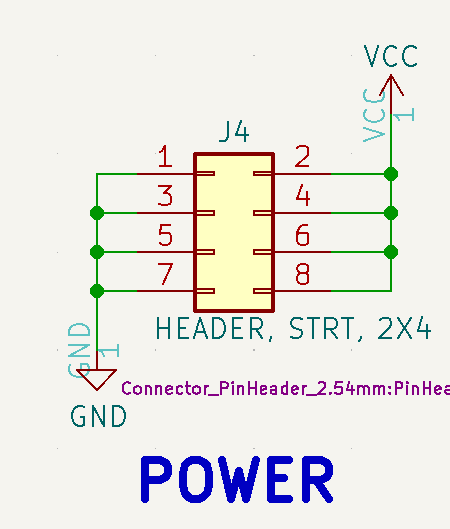

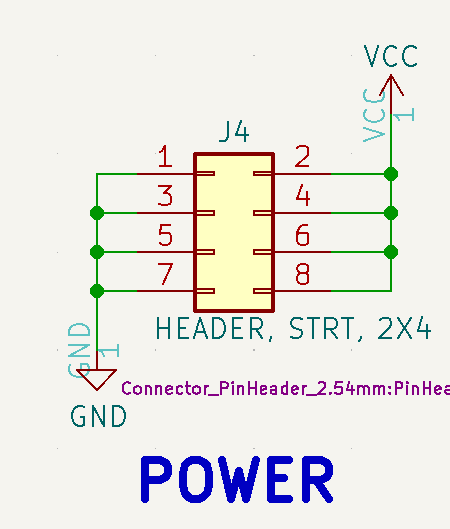

J4 - 5V Power

Software

Mechanicals

Assembly Sheet

SIMPLE-Z80 Rev 1 Assembly Sheet