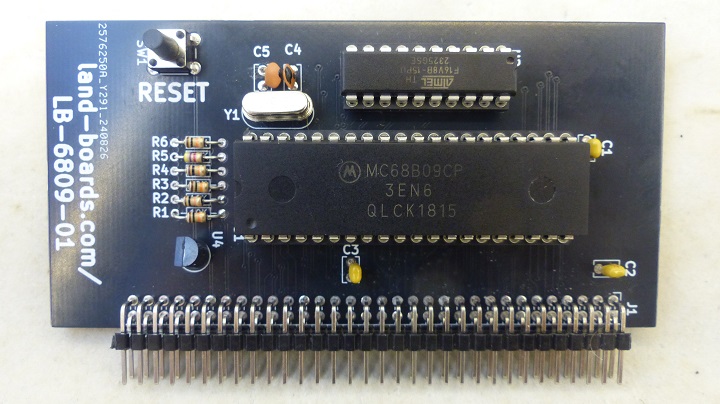

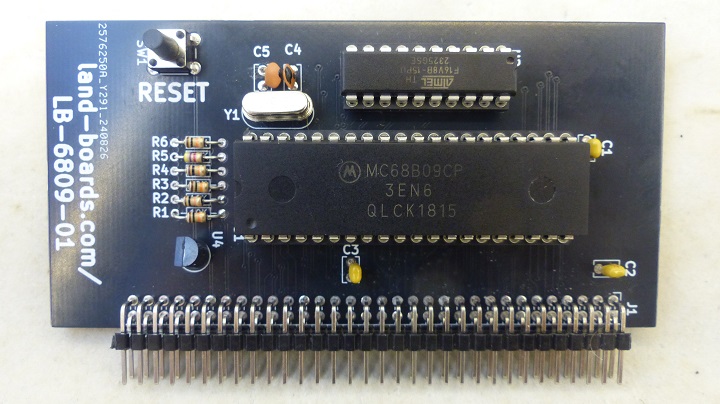

Features

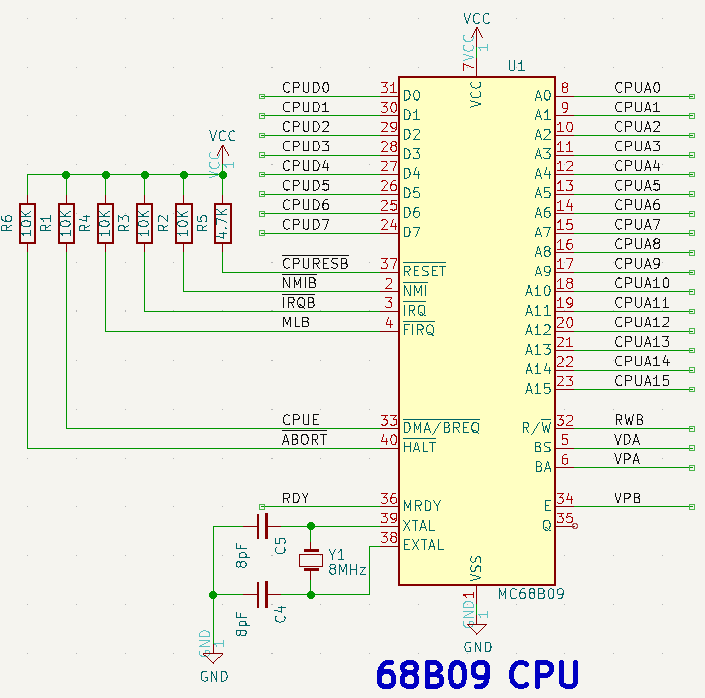

- 68B09 CPU

- 8 MHZ crystal on card

- Reset switch/power monitor

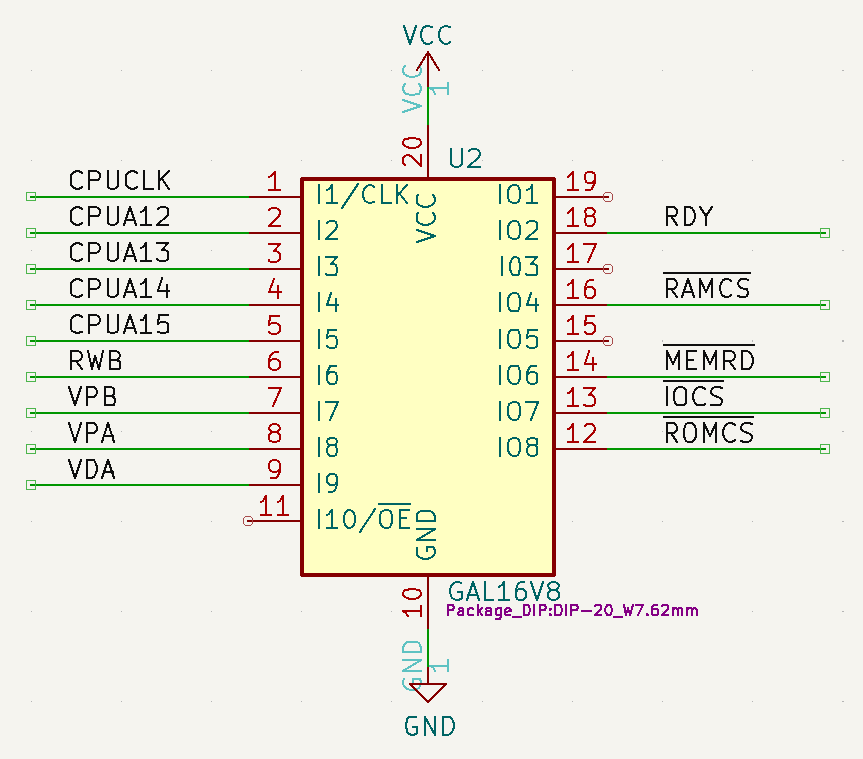

- Address decoder PLD drives RAM/ROM/IO chip selects

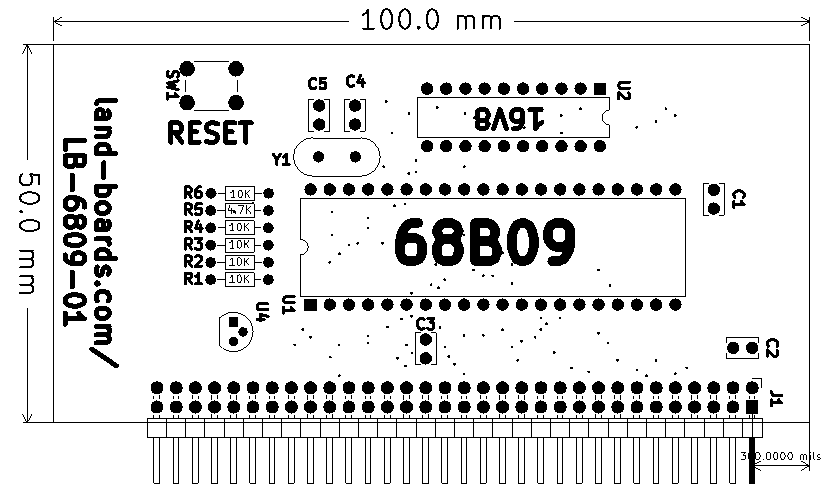

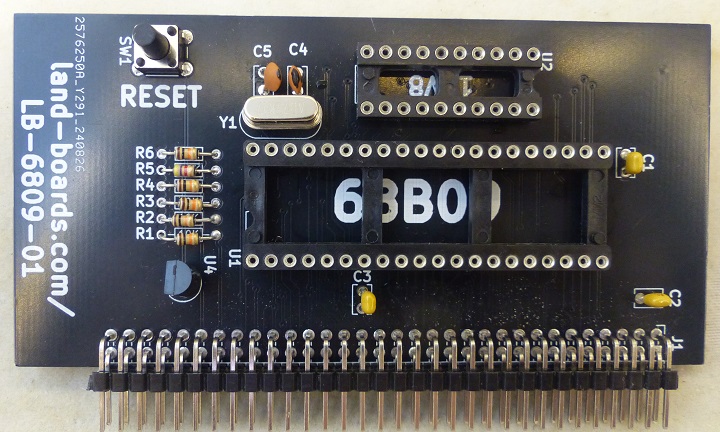

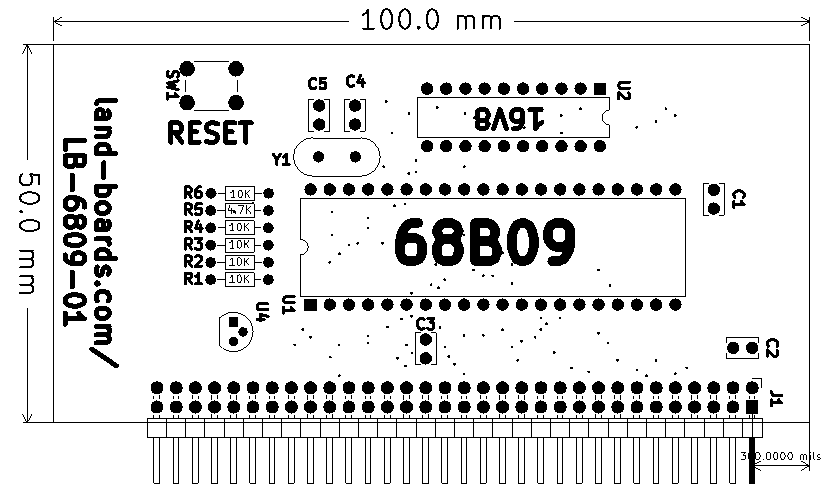

- 100x50mm card

Memory Map

- 0x0000-0x7FFF 32KB SRAM

- 0x8000-0x9FFF Free Space (8KB)

- 0xA000-0xBFFF Serial (ACIA)

- 0xC000-0xFFFF 16KB EPROM

Design

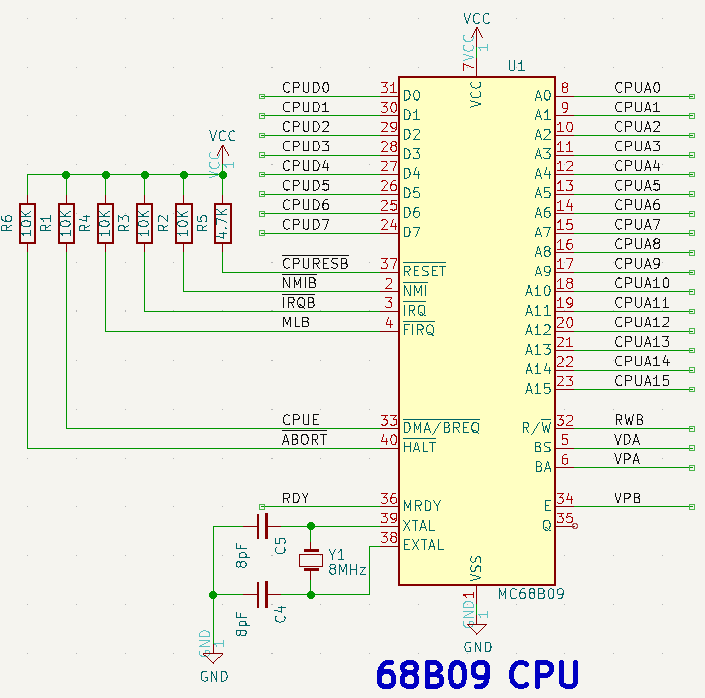

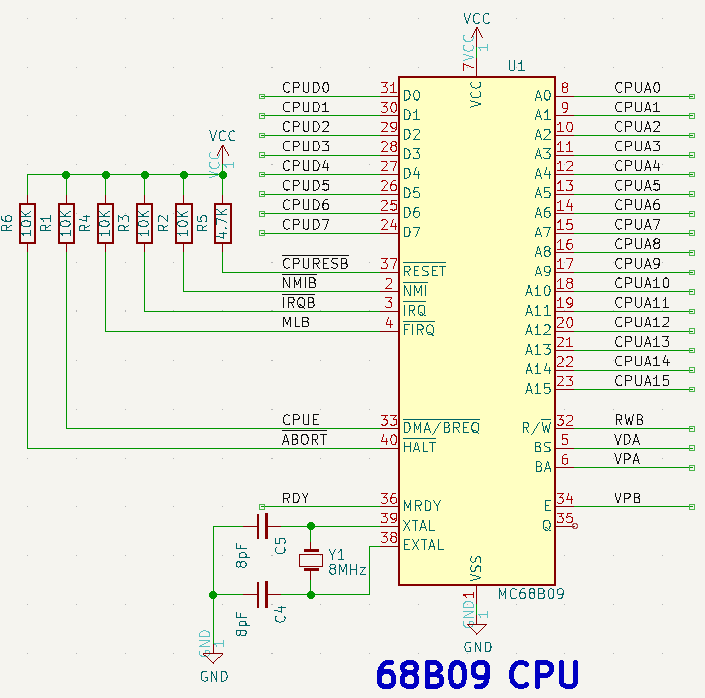

68B09 CPU

- 8 MHz clock

- Runs effectively at 2 MHz

CPU

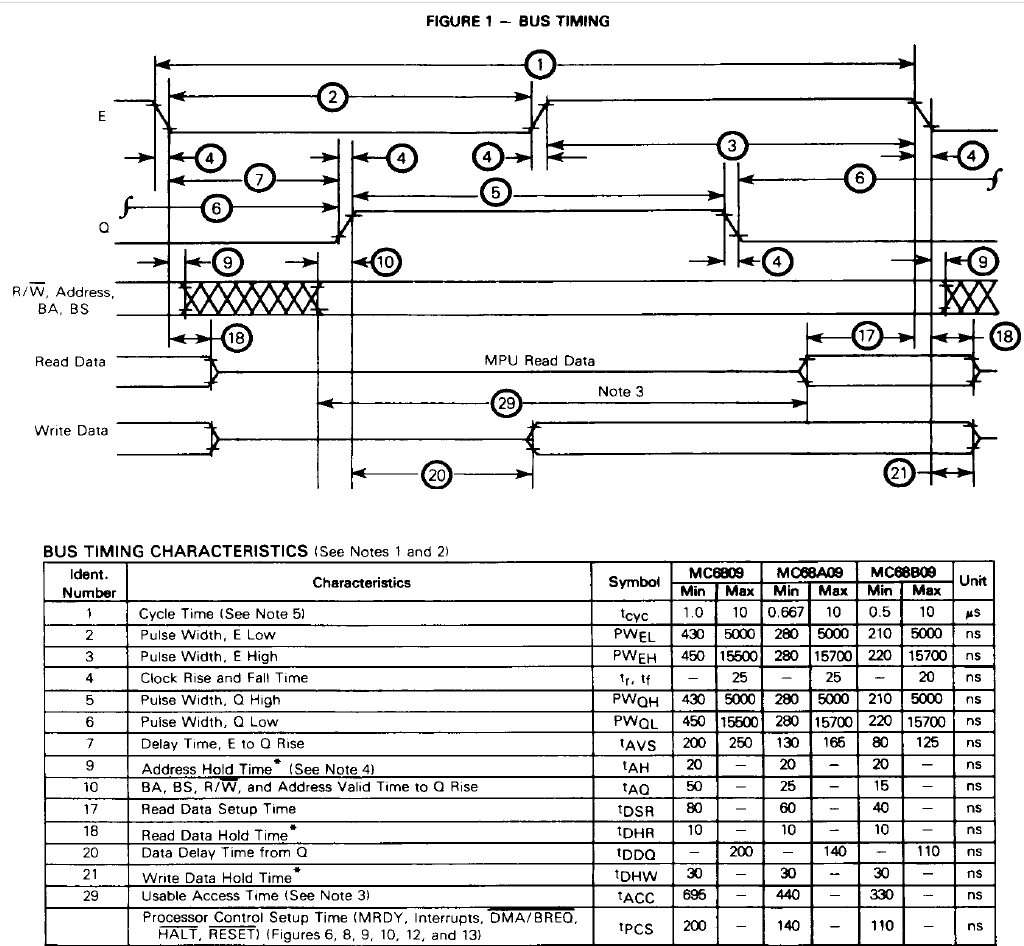

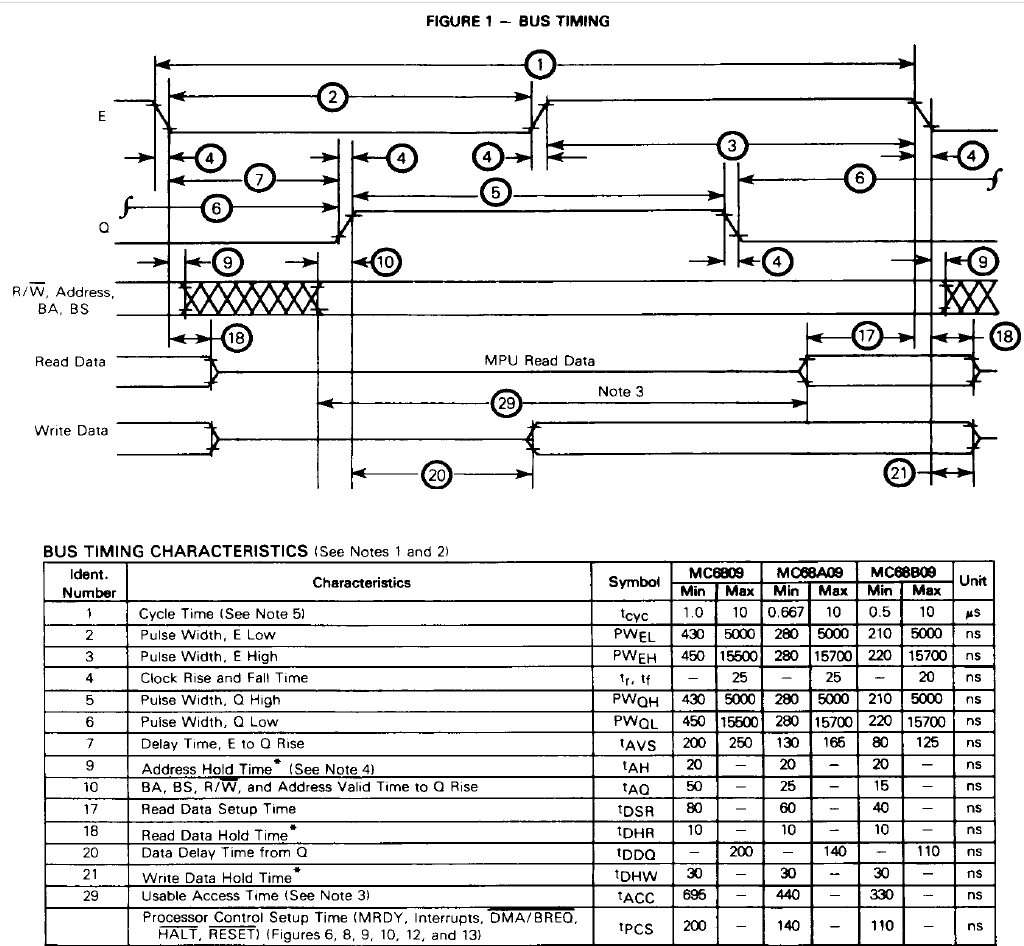

CPU Timing

Clock

Crystal

- Uses CPU internal oscillator

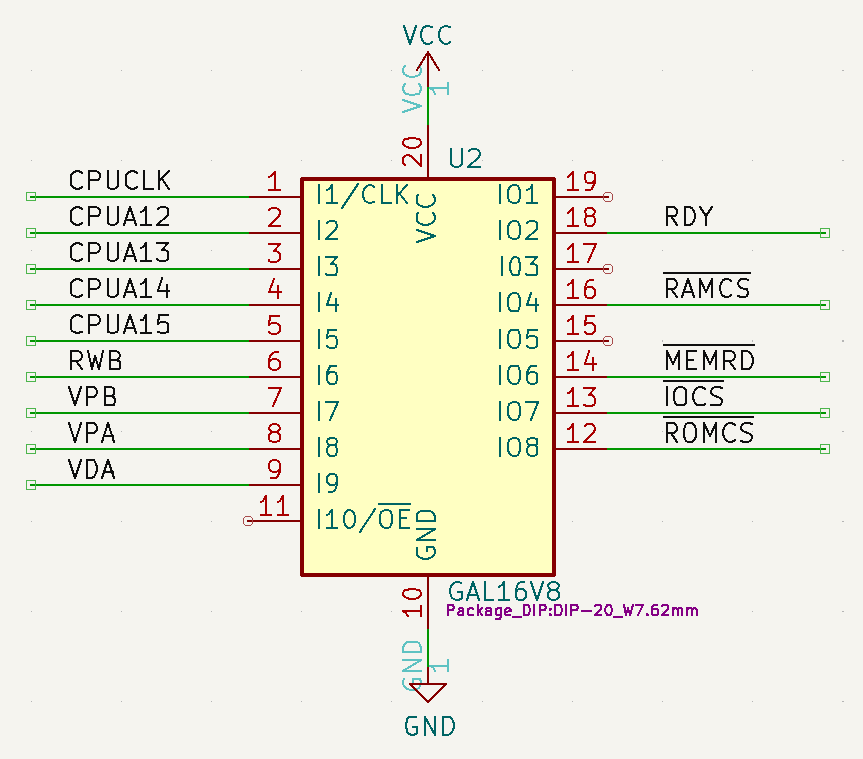

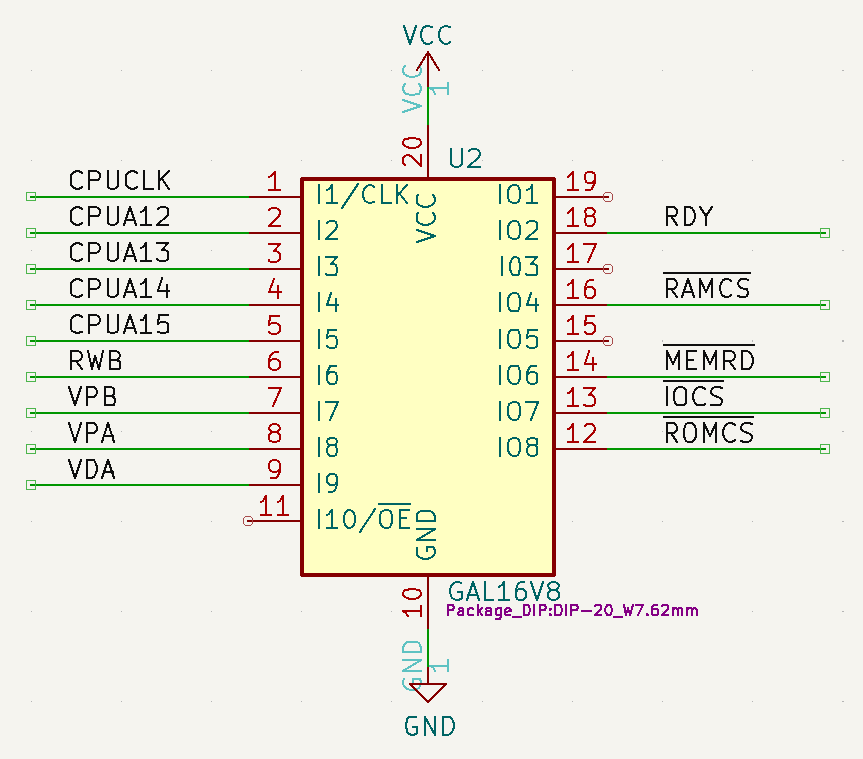

PLD

PLD Listing

Name LB-6809-01_PLD;

Partno ATF16V8B;

Date 09/05/24;

Revision 01;

Designer DOUG G;

Company LAND BOARDS LLC;

Assembly LB680901_U2;

Location Rustbelt, US;

Device G16V8;

/*

*/

/* Control inputs */

PIN 1 = CLK;

PIN 2 = CPUA12;

PIN 3 = CPUA13;

PIN 4 = CPUA14;

PIN 5 = CPUA15;

PIN 6 = CPUREAD;

PIN 7 = VPB; /* Added as wire on Rev 1 PCB */

PIN 8 = VPA;

PIN 9 = VDA;

PIN 11 = D0;

/* Address Decode and Chip Select outputs */

PIN 12 = !ROMCS;

PIN 13 = !IOCS;

PIN 14 = !MEMRD;

PIN 15 = LED;

PIN 16 = !RAMCS;

PIN 17 = LEDSTR;

PIN 18 = RDY;

ROMCS = CPUA15 & CPUA14 & CPUREAD;

LEDSTR = CPUA15 & CPUA14 & !CPUREAD & VPB;

LED = LEDSTR & D0

# LED & !LEDSTR;

RAMCS = !CPUA15 & CPUREAD /* 0x0000-0x7FFF 32KB SRAM */

# !CPUA15 & !CPUREAD & VPB

# CPUA15 & !CPUA14 & !CPUA13 & CPUREAD /* 0x8000-0x9FFF Free (8KB */

# CPUA15 & !CPUA14 & !CPUA13 & !CPUREAD & VPB;

IOCS = CPUA15 & !CPUA14 & CPUA13 & VPB; /* 0xA000-0xBFFF Serial (ACIA) */

RDY = VPB;

MEMRD = CPUREAD;

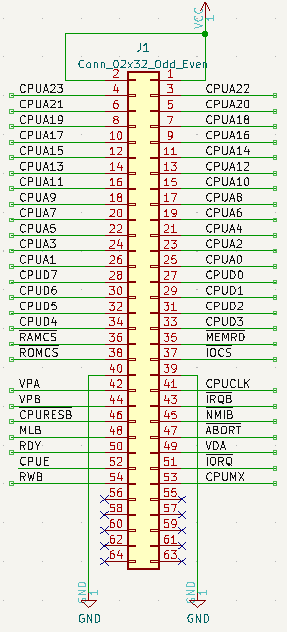

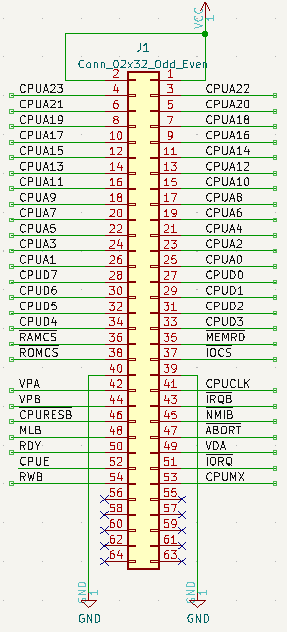

Backplane connector

Software

Build 6809 Assembly Code (Windows 64-bit)

- Run asm6809 in Windows CMD prompt window

[path_to_asm6809.exe_program\]asm6809 loop.asm -H -l -o loop.hex

- -H option creates hex record file to download to programmer

- -l fileName option creates listing file

- -o filename option followed by output file name

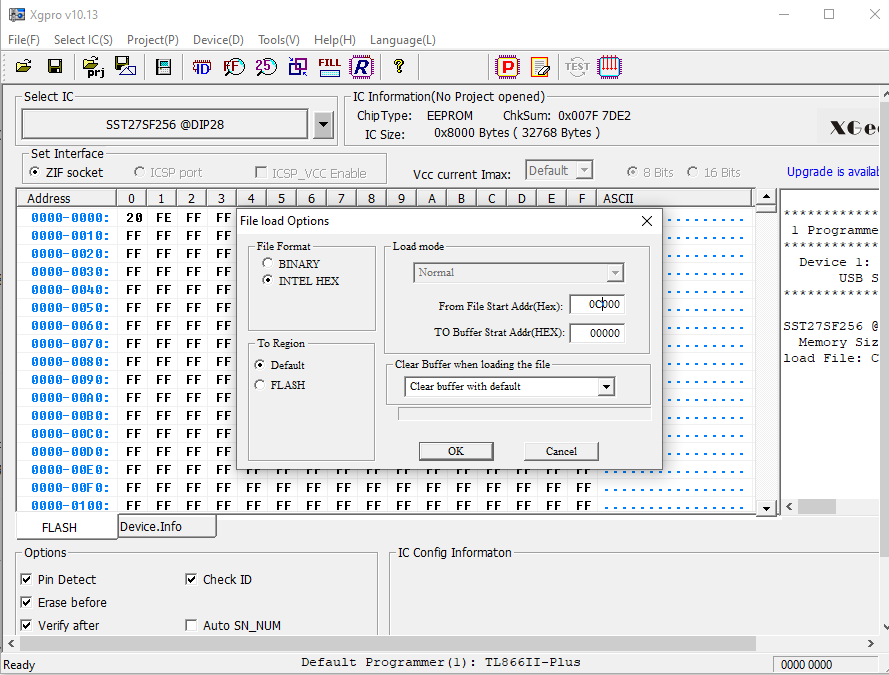

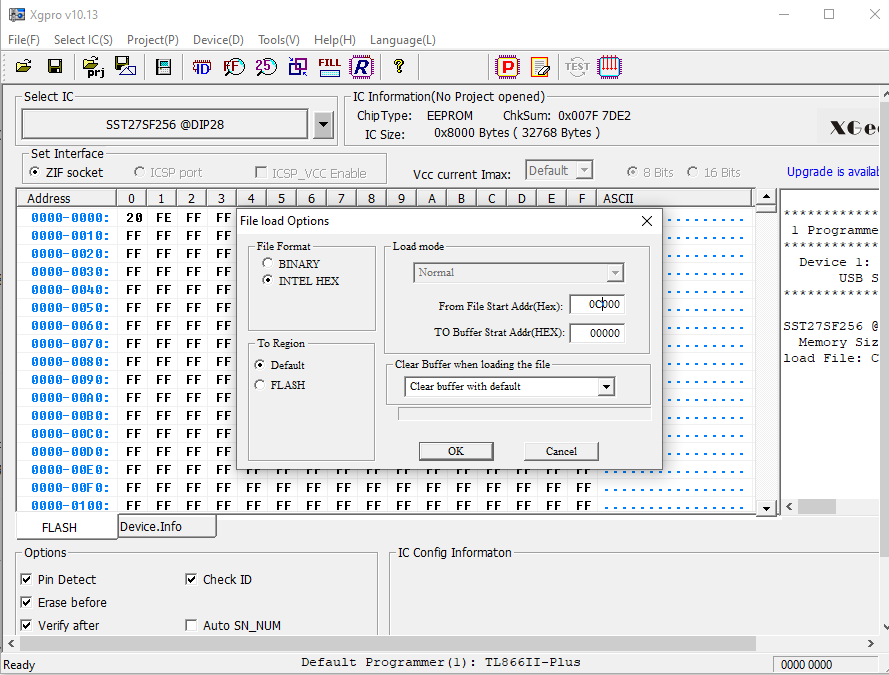

Programming using TL866

ROM access test code (loop.asm)

..\..\M6809_Assembler\asm6809-2.13-w64\asm6809 loop.asm -H -l loop.lst -o loop.hex

ORG $C000

RESVEC BRA RESVEC

ORG $FFFE

LBFFE FDB RESVEC ; RESET

:02C0000020FE20

:02FFFE00C00041

:00000001FF

LED Blink code (blink.asm)

- Added PLD code to make a trigger on pin 17 when EPROM address 0xC000-0xF000 is written

- Code doesn't use any RAM (CPU and EPROM only)

- LED is on U2-15 to GNS w/ 1.8K resistor

- Assemble blink.asm code

- See Rev 2 checkout notes for LED

..\..\M6809_Assembler\asm6809-2.13-w64\asm6809 blink.asm -H -l blink.lst -o blink.hex

- Works, blinks LED at about 2 Hz

- Can use this as a SRAM test outout

- Fast blink = Fail

- Slow blink = Pass

SRAM Test (ramLoop.asm)

- ramLoop.asm - GitHub

- Loops on SRAM write/read on LB-6809-01 card

- Turn on LED if the test passes

- Turn off LED if the test fails

- Passes

SRAM Test (ramTest1.asm)

- ramTest1.asm - GitHub

- Write/read SRAM write/read single location on LB-MEM-02 card

- Blink LED slowly if the test passes

- Blink LED quickly if the test fails

- Passes

SRAM Test (ramTest.asm)

- ramTest.asm - GitHub

- Write/read SRAM write/read on all SRAM on LB-MEM-02 card

- Test single location with 0x55/0xaa

- Test all RAM with ramp

- Tests all locations but repeats ever 256 bytes so addresses are not completely tested

- Ramp upper 7 address lines with a ramp

- Blink LED slowly if the test passes

- Blink LED quickly if the test fails

- Test takes 0.6 secs

- Passes

ACIATest.asm

- AciaTest.asm

- Wrote code with Microsoft Pilot with minor modifications

- Required etch cut and added wire on LB-6850-02 card

- Loops back data typed in

Reference Designs

Mechanicals

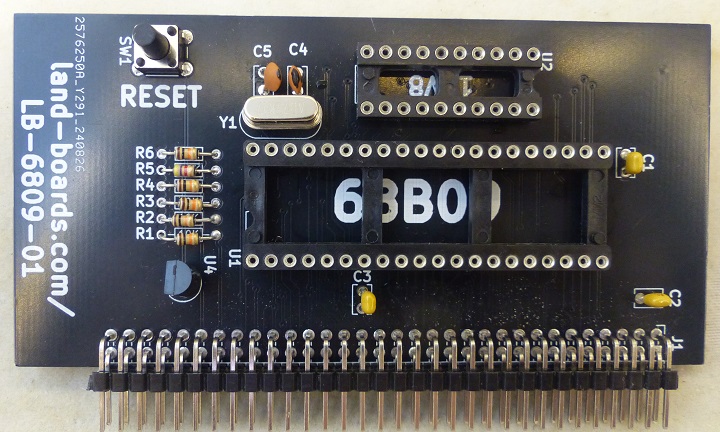

Rev 2

Checkout

Rev 2 Checkout

- Built

- Worked with NOP Tester

- Got 8 MHz crystal

- E signal is 2 MHz- good

- Add LED that can be written under program control

- Add wire U1-31 to U2-11 (D0)

- Add LEDSTR when strobe write to 0xC000-0xFFFF (U2-17)

- Add LED to U2-15 with 1.8K resistor

- Write to 0xF000 to toggle the line

- Running blink.asm code

Rev 2 PCB Changes from Rev 1

- Add U1-34 to U2-7 (VPB/E)

- Eliminate oscillator

- Add 8 MHz crystal/caps

- Cheaper and easier to find

- Add 4.7K pullup to U1-40 (ABORT*/HALT) line

- Change resistor values to lighten up Iol

- Beef up power plane connections to J1 and CPU/cap

- Move reset switch to the top of the board (where the oscillator used to be)

Rev 1 Checkout Notes

- Did not build

- Add wire U1-34 to U2-7 (VPB/E)

- Ground XTAL pin on CPU U1-39 (to U1-1 = GND)

- Use BOM for resistor values, not silkscreen

- Add 4.7K pullup to ABORT* line

Assembly Sheet

Rev 2

Rev 1