Difference between revisions of "SIMPLE-6502"

Jump to navigation

Jump to search

Blwikiadmin (talk | contribs) (→Clock) |

Blwikiadmin (talk | contribs) |

||

| (55 intermediate revisions by the same user not shown) | |||

| Line 1: | Line 1: | ||

| + | [[File:tindie-mediums.png|link=https://www.tindie.com/products/34959/]] | ||

| + | |||

[[FILE:SIMPLE-6502_P1090254-720pxV.jpg]] | [[FILE:SIMPLE-6502_P1090254-720pxV.jpg]] | ||

| Line 25: | Line 27: | ||

* 0x8000-0x9FFF Free Space (8KB) | * 0x8000-0x9FFF Free Space (8KB) | ||

* 0xA000-0xBFFF Serial (ACIA) | * 0xA000-0xBFFF Serial (ACIA) | ||

| − | * 0xC000- | + | * 0xC000-0xFFFF 16KB EPROM |

=== Chip Set === | === Chip Set === | ||

| Line 33: | Line 35: | ||

[[file:LB_65C02_PARTS.jpg]] | [[file:LB_65C02_PARTS.jpg]] | ||

| − | * | + | * Picture shows 3 MHz CPU |

| + | * Received 2 MHz CPU | ||

| + | * As received: | ||

[[file:SIMPLE-6502_P1090155-720px.jpg]] | [[file:SIMPLE-6502_P1090155-720px.jpg]] | ||

| Line 49: | Line 53: | ||

== Design == | == Design == | ||

| − | + | === CPU === | |

[[file:U5_CPU_6502.PNG]] | [[file:U5_CPU_6502.PNG]] | ||

| − | * EPROM/EPROM | + | ==== R6502 CPU Timing ==== |

| + | |||

| + | [[file:R6502_Timing-01.PNG]] | ||

| + | [[file:R6502_Timing-02.PNG]] | ||

| + | |||

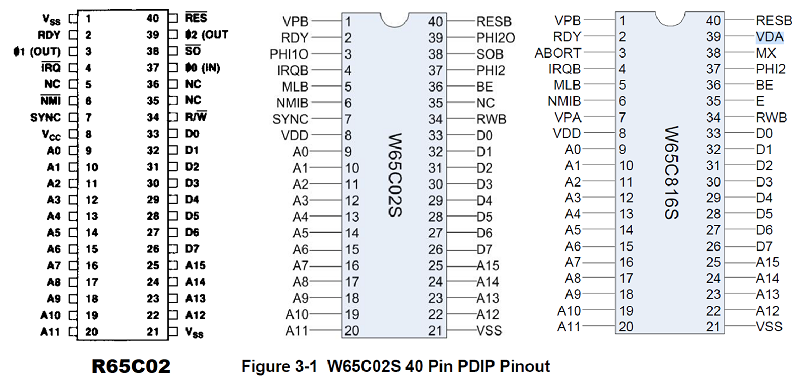

| + | ==== R65C02 vs W65C02 vs W65C816 CPUs ==== | ||

| + | |||

| + | {| class="wikitable" | ||

| + | ! U5 Pin | ||

| + | ! U5 Pin Name | ||

| + | ! Sig Name | ||

| + | ! Pullup | ||

| + | ! R65C02 sig | ||

| + | ! W65C02 sig | ||

| + | ! W65C816 sig | ||

| + | |- | ||

| + | | 1 | ||

| + | | VSS/VPB | ||

| + | | JP1 GNDs | ||

| + | | N | ||

| + | | VSS (IN) | ||

| + | | VPB (OUT) | ||

| + | | VPB (OUT) | ||

| + | |- | ||

| + | | 3 | ||

| + | | PH1OUT/ABORT | ||

| + | | NC | ||

| + | | N | ||

| + | | PH1OUT (OUT) | ||

| + | | PH1OUT (OUT) | ||

| + | | ABORT (IN) | ||

| + | |- | ||

| + | | 5 | ||

| + | | NC/MLB | ||

| + | | NC | ||

| + | | N | ||

| + | | NC | ||

| + | | MLB (OUT) | ||

| + | | MLB (OUT) | ||

| + | |- | ||

| + | | 7 | ||

| + | | SYNC/VPA | ||

| + | | NC | ||

| + | | N | ||

| + | | SYNC (OUT) | ||

| + | | SYNC (OUT) | ||

| + | | VPA (OUT) | ||

| + | |- | ||

| + | | 35 | ||

| + | | NC/E | ||

| + | | NC | ||

| + | | N | ||

| + | | NC | ||

| + | | NC | ||

| + | | EM/NAT (OUT) | ||

| + | |- | ||

| + | | 36 | ||

| + | | NC/BE | ||

| + | | Pull up | ||

| + | | Y | ||

| + | | NC | ||

| + | | BE (IN) | ||

| + | | BE (IN) | ||

| + | |- | ||

| + | | 37 | ||

| + | | PH0IN/PH2IN | ||

| + | | CPUCLK | ||

| + | | N | ||

| + | | PH0IN | ||

| + | | PH2IN | ||

| + | | PH2IN | ||

| + | |- | ||

| + | | 38 | ||

| + | | SO/MX | ||

| + | | VCC | ||

| + | | VCC | ||

| + | | SO* (IN) | ||

| + | | SOB (IN) | ||

| + | | MX (OUT) | ||

| + | |- | ||

| + | | 39 | ||

| + | | PH2OUT/VDA | ||

| + | | PH2_OUT | ||

| + | | N | ||

| + | | PH2OUT (OUT) | ||

| + | | PH2OUT (OUT) | ||

| + | | VDA(OUT) | ||

| + | |- | ||

| + | |} | ||

| + | |||

| + | * Need to lift U5-38 to use W65C816 CPU | ||

| + | |||

| + | [[file:R65C02_vs_W65C02_w65c816_Pinout_800PX.png]] | ||

| + | |||

| + | ===== VDA/VPA (65C816) ===== | ||

| + | |||

| + | * VDA/VPA | ||

| + | ** 00, Internal operation (invalid address bus) | ||

| + | ** 01, Valid Program Address | ||

| + | ** 10, Valid Data Address | ||

| + | ** 11, Opcode-fetch | ||

| + | |||

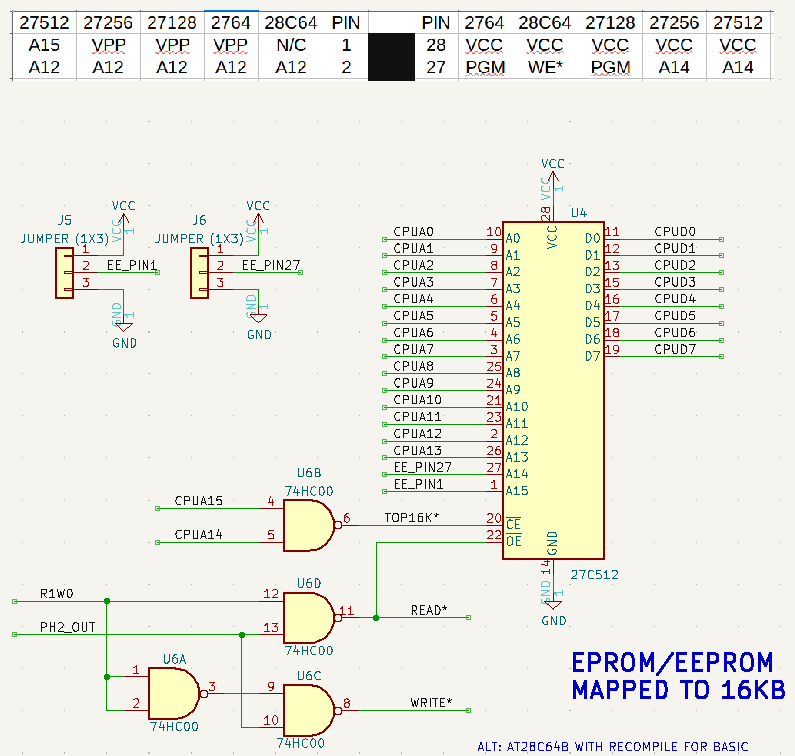

| + | === EPROM/EPROM === | ||

| + | |||

| + | * [[TL866ii Plus Programmer]] | ||

[[file:U4_EEPROM.PNG]] | [[file:U4_EEPROM.PNG]] | ||

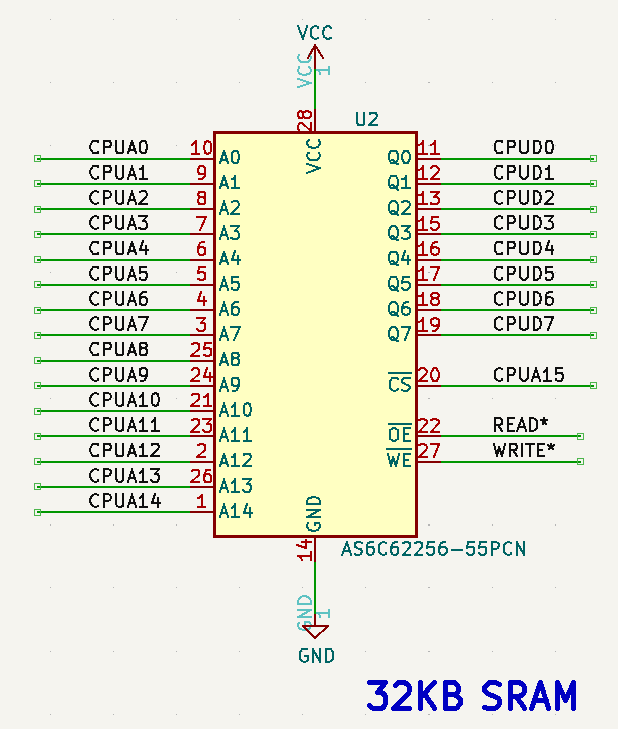

| − | + | === SRAM === | |

[[file:U2_SRAM.PNG]] | [[file:U2_SRAM.PNG]] | ||

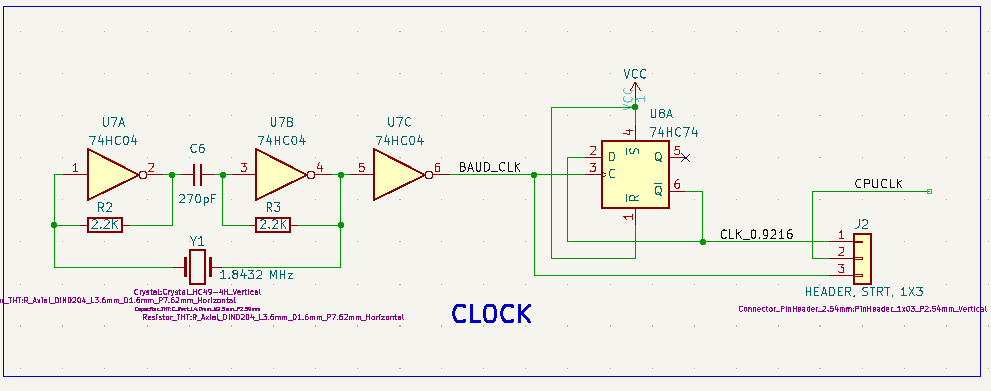

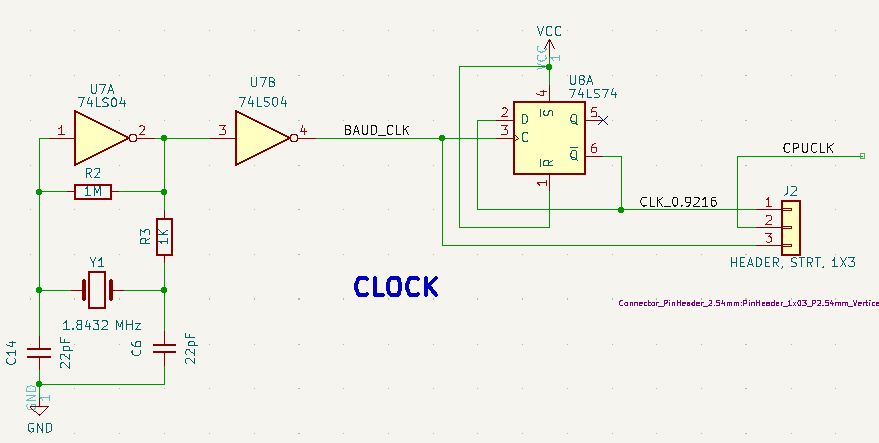

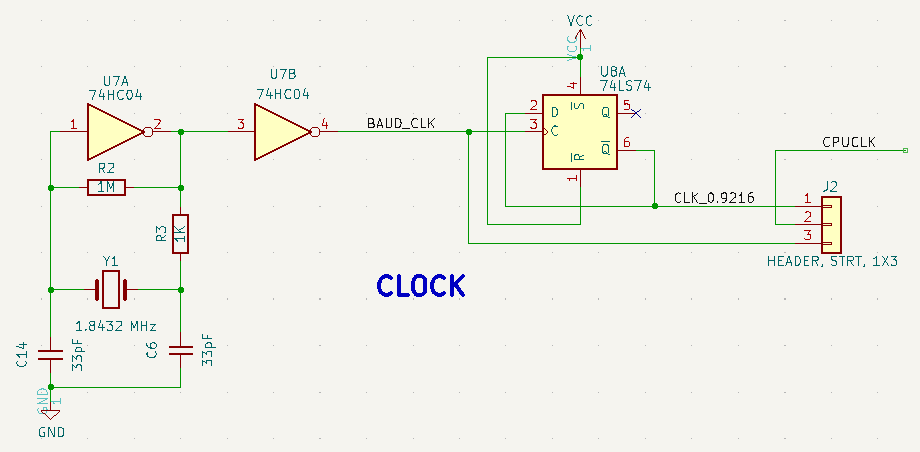

| − | + | === Clock (Rev 1) === | |

[[file:U7_U8_CLOCK.PNG]] | [[file:U7_U8_CLOCK.PNG]] | ||

| − | + | === Clock (Rev 2) === | |

[[file:U7_U8_CLOCK_v2.PNG]] | [[file:U7_U8_CLOCK_v2.PNG]] | ||

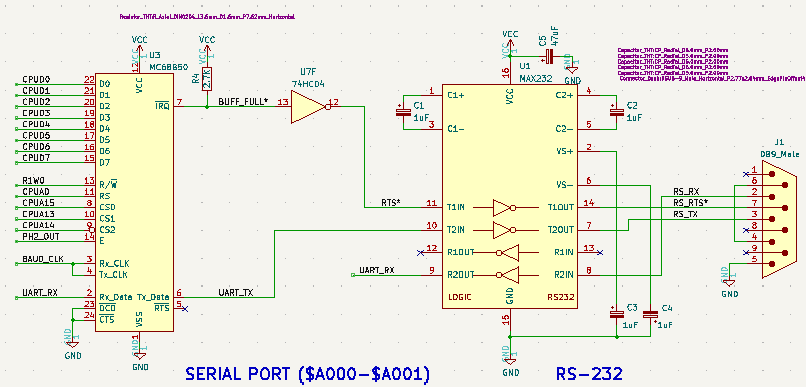

| − | * | + | === UART === |

| + | |||

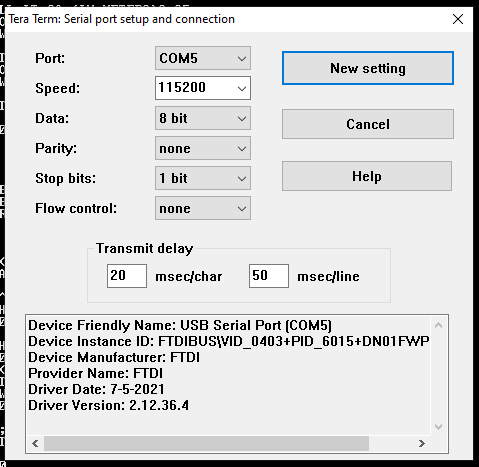

| + | * Can only use RS-232 or FTDI - one at a time | ||

| + | ** Put MAX232 in a socket if you want flexibility | ||

| + | ** Remove MAX232 if you want to use FTDI | ||

[[file:U1_U3_UART.PNG]] | [[file:U1_U3_UART.PNG]] | ||

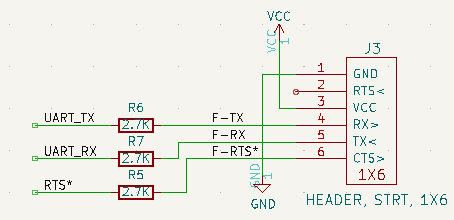

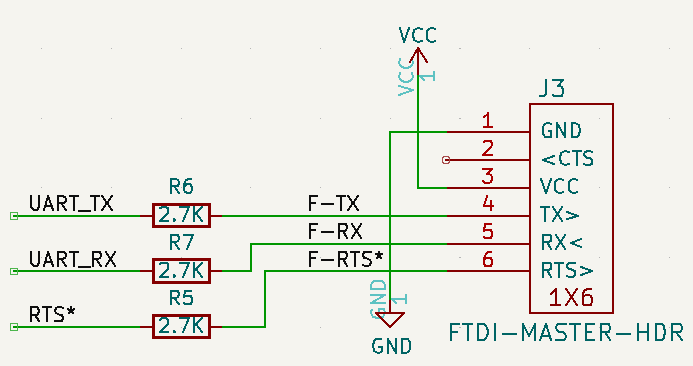

| − | + | === FTDI === | |

| − | + | ||

| + | * Does not match Grant's pinout | ||

| + | * Can only use RS-232 or FTDI - one at a time | ||

[[file:J3_FTDI.PNG]] | [[file:J3_FTDI.PNG]] | ||

| Line 432: | Line 546: | ||

** It is in standard INTEL-HEX format for uploading to a suitable programmer. | ** It is in standard INTEL-HEX format for uploading to a suitable programmer. | ||

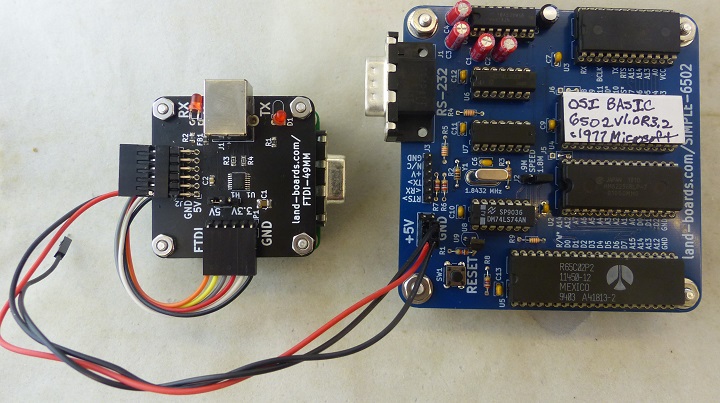

| − | == First Unit Checkout == | + | == First Unit Checkout (Rev 1 PCB) == |

[[FILE:SIMPLE-6502_P1090185-720PX.jpg]] | [[FILE:SIMPLE-6502_P1090185-720PX.jpg]] | ||

| Line 482: | Line 596: | ||

** Not sure if this is clock related | ** Not sure if this is clock related | ||

* Order new 74LS04 parts | * Order new 74LS04 parts | ||

| − | * Rev 2 updates | + | * See Rev 2 updates |

| − | |||

| − | |||

=== Reset === | === Reset === | ||

| Line 590: | Line 702: | ||

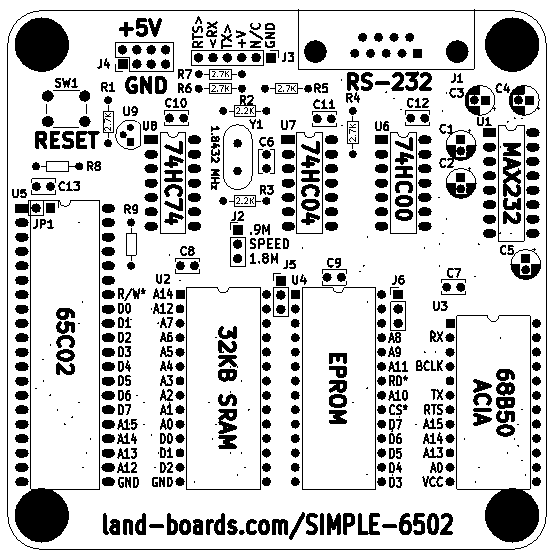

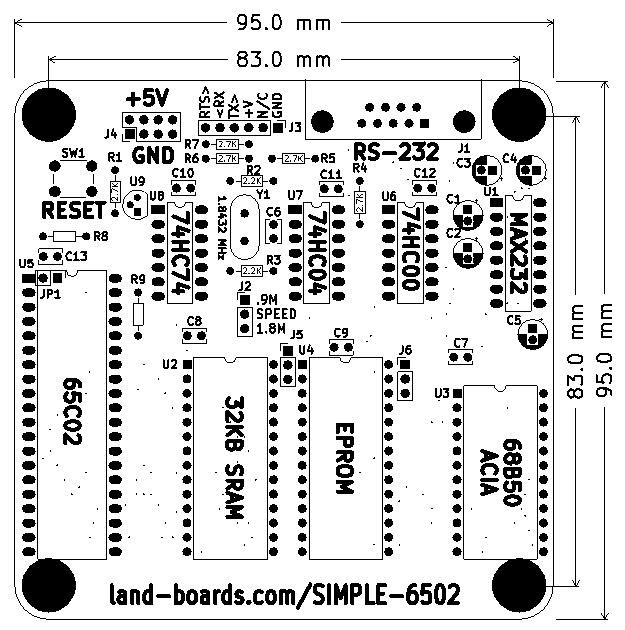

== Mechanicals == | == Mechanicals == | ||

| + | |||

| + | * Rev 1 board | ||

| + | ** Rev 2 board has the same mechanical dimensions, but some parts are different | ||

[[FILE:SIMPLE-6502_REV1_MECHS.PNG]] | [[FILE:SIMPLE-6502_REV1_MECHS.PNG]] | ||

| + | |||

| + | == PCB Issues == | ||

| + | |||

| + | === Rev 2 === | ||

| + | |||

| + | * See clock section above for issues found during Rev 1 board checkout | ||

| + | |||

| + | [[File:SIMPLE-6502_Rev2_ClockUpdates.PNG]] | ||

| + | |||

| + | * R8, R9 missing 2.7K marking on silkscreen | ||

| + | ** Updated on Rev 2 interactive BOM | ||

| + | * C6, C14 change value to 33 pF | ||

| + | ** Symptom with 22 pF caps was wrong oscillation frequency (approx 2.1 MHz) | ||

| + | ** Crystal is 18pF | ||

| + | *** Matching caps should be 2x (since the caps are essentially in series | ||

| + | *** 36pF would be right, but there's also pin and PCB capacitance so use 33 pF caps | ||

| + | **** [https://www.iqdfrequencyproducts.com/blog/2020/08/03/myths-around-load-capacitance-how-to-choose-the-right-capacitors/ How to pick the right cap for oscillator] | ||

| + | * U7 has to be 74HC04 with these other value parts | ||

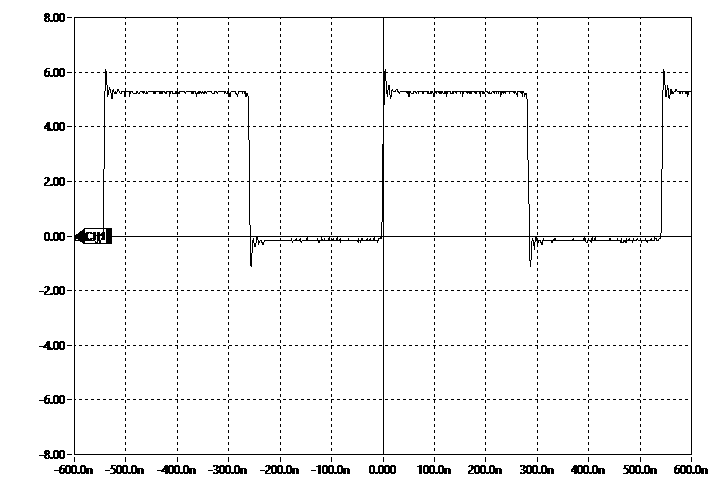

| + | * Measured oscillator circuit timing/voltages | ||

| + | [[file:SIMPLE-6502_Rev2_Oscillator.png]] | ||

| + | |||

| + | === Rev 1 === | ||

| + | |||

| + | * Clocking not optimal - see notes above in clock section for debug issues | ||

== Assembly Sheet == | == Assembly Sheet == | ||

| Line 598: | Line 737: | ||

* [http://land-boards.com/SIMPLE-6502/SIMPLE-6502_Rev2_ibom.html SIMPLE-6502 Rev 2 Interactive BOM] | * [http://land-boards.com/SIMPLE-6502/SIMPLE-6502_Rev2_ibom.html SIMPLE-6502 Rev 2 Interactive BOM] | ||

| + | * Install jumper JP1 on rear of board if CPU is not a WDC 65C02 or WDC 65C816 | ||

| + | * Install jumpers J5-2 to -3 and J6-2 to -3 | ||

| + | * Clock changes from Grant's design | ||

| + | * U7 is 74HC04 (silkscreen shows 74LS04) | ||

| + | ** 74LS04 might work if the Resistor values in the clock circuit are changed | ||

| + | * Jumper J2 clock to run the CPU at either 1.8432 MHz or half speed 0.9216 MHz | ||

=== Assembly Sheet Rev 1 === | === Assembly Sheet Rev 1 === | ||

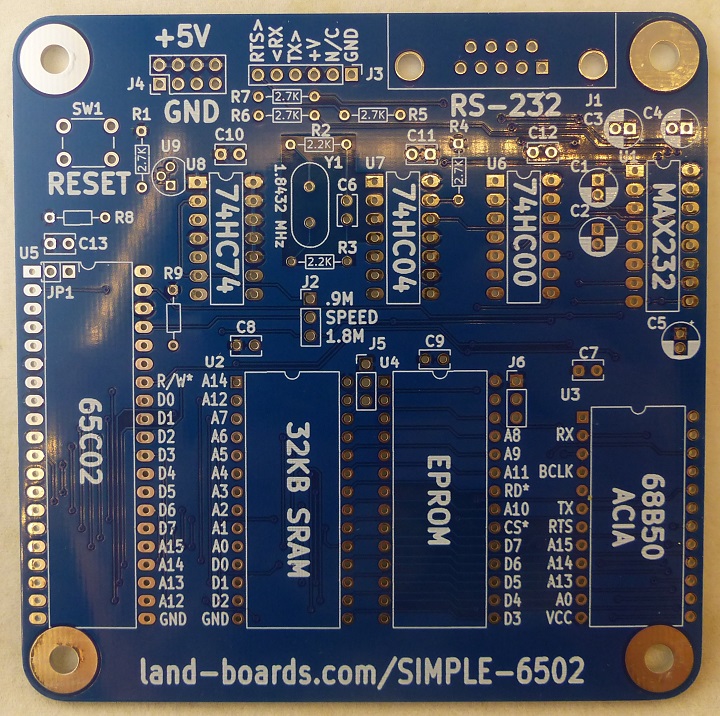

Latest revision as of 18:50, 28 August 2024

Contents

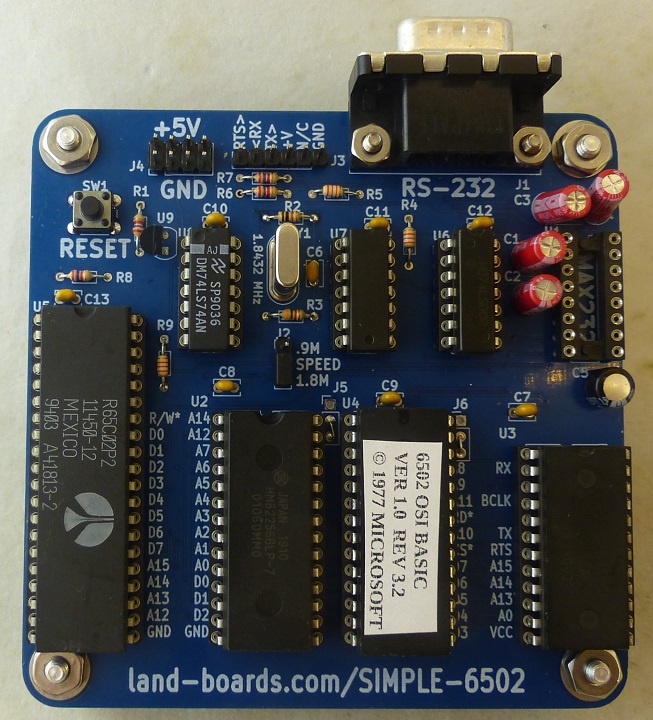

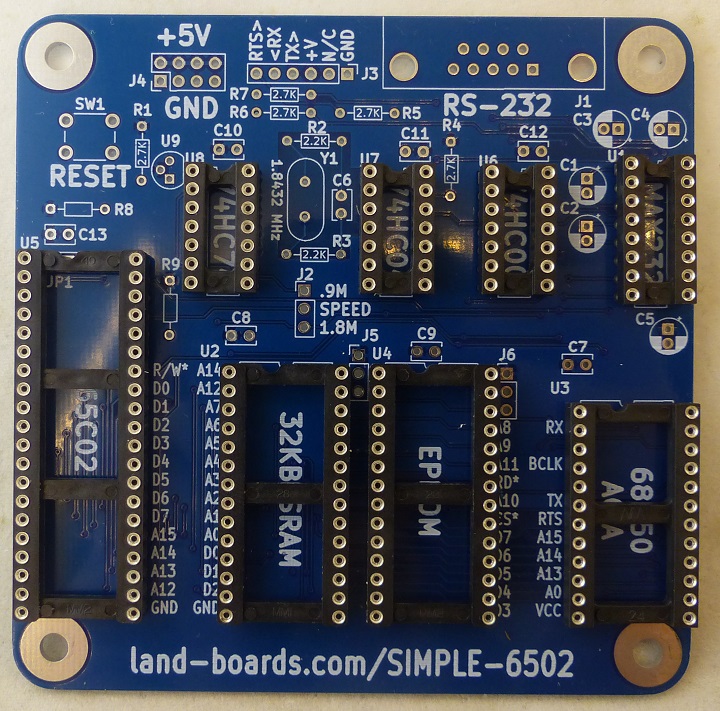

Features

- Build of Grant Searles's Simple 6502 CPU

- Runs Microsoft (OSI) BASIC

- 65C02 CPU

- 0.9216 or 1.8432 MHz clock - jumper selectable

- 32KB SRAM

- 16KB EPROM/EEPROM

- Using 1/2 of SST27SF256 - 32KB Flash Memory

- 68B50 Serial Port (ACIA)

- MAX232 RS-232 port or

- Header for FTDI

- 115,200 baud

- Reset switch with optional DS1813 5V Power Supervisor

- 95x95mm card

- (4) 6-32 mounting holes

Memory Map

- 0x0000-0x7FFF 32KB SRAM

- 0x8000-0x9FFF Free Space (8KB)

- 0xA000-0xBFFF Serial (ACIA)

- 0xC000-0xFFFF 16KB EPROM

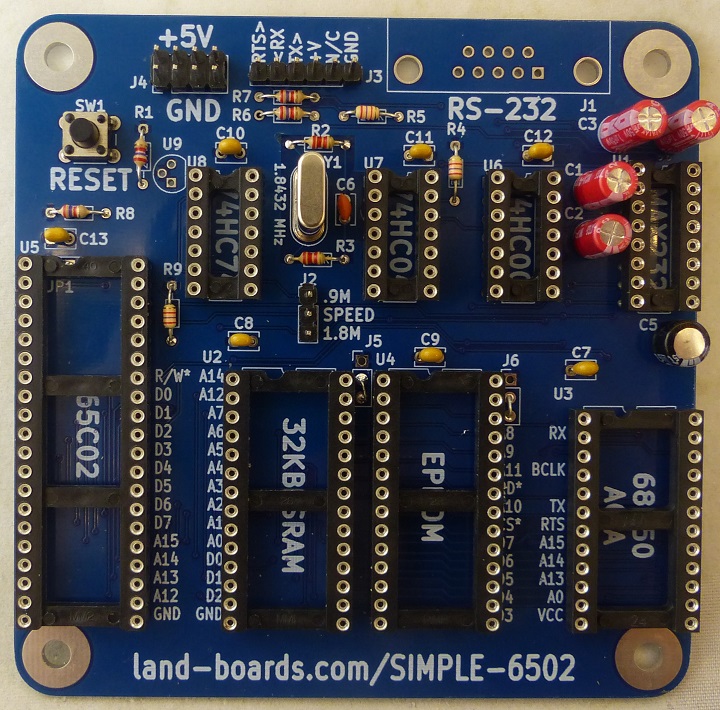

Chip Set

- Picture shows 3 MHz CPU

- Received 2 MHz CPU

- As received:

References

- Grant Searles's Simple 6502 CPU - This build

- 6502.org

- 6502 PRIMER: Building your own 6502 computer - Great resource with a lot of design information

- Build Your Own 6502 Computer

Design

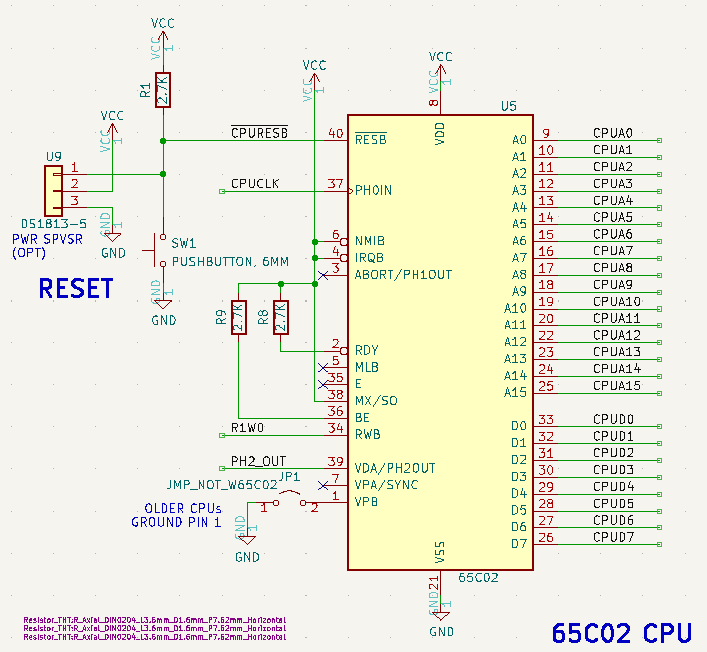

CPU

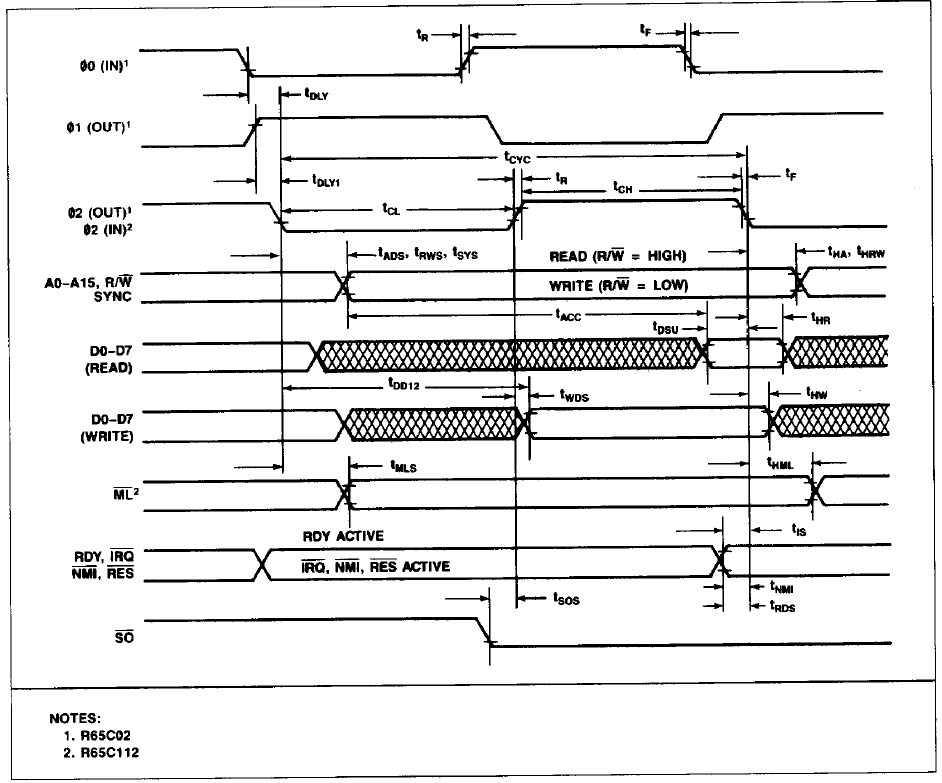

R6502 CPU Timing

R65C02 vs W65C02 vs W65C816 CPUs

| U5 Pin | U5 Pin Name | Sig Name | Pullup | R65C02 sig | W65C02 sig | W65C816 sig |

|---|---|---|---|---|---|---|

| 1 | VSS/VPB | JP1 GNDs | N | VSS (IN) | VPB (OUT) | VPB (OUT) |

| 3 | PH1OUT/ABORT | NC | N | PH1OUT (OUT) | PH1OUT (OUT) | ABORT (IN) |

| 5 | NC/MLB | NC | N | NC | MLB (OUT) | MLB (OUT) |

| 7 | SYNC/VPA | NC | N | SYNC (OUT) | SYNC (OUT) | VPA (OUT) |

| 35 | NC/E | NC | N | NC | NC | EM/NAT (OUT) |

| 36 | NC/BE | Pull up | Y | NC | BE (IN) | BE (IN) |

| 37 | PH0IN/PH2IN | CPUCLK | N | PH0IN | PH2IN | PH2IN |

| 38 | SO/MX | VCC | VCC | SO* (IN) | SOB (IN) | MX (OUT) |

| 39 | PH2OUT/VDA | PH2_OUT | N | PH2OUT (OUT) | PH2OUT (OUT) | VDA(OUT) |

- Need to lift U5-38 to use W65C816 CPU

VDA/VPA (65C816)

- VDA/VPA

- 00, Internal operation (invalid address bus)

- 01, Valid Program Address

- 10, Valid Data Address

- 11, Opcode-fetch

EPROM/EPROM

SRAM

Clock (Rev 1)

Clock (Rev 2)

UART

- Can only use RS-232 or FTDI - one at a time

- Put MAX232 in a socket if you want flexibility

- Remove MAX232 if you want to use FTDI

FTDI

- Does not match Grant's pinout

- Can only use RS-232 or FTDI - one at a time

Headers / Connectors

J1 - RS-232 Serial

- DB-9 Male

- Matches Grant's pinout

- Pinout

- N/C

- Receive

- Transmit

- Loop to pin 6

- GND

- Loop to pin 4

- RTS

- N/C

- N/C

J2 - Speed Select Jumper

- 1-2 - 0.92 MHz

- 2-3 = 1.8432 MHz

J3 - FTDI / TTL Serial

- Requires a FTDI cross-over cable

- GND

- RTS* (out)

- +5V

- Receive (in)

- Transmit (out)

- N/C

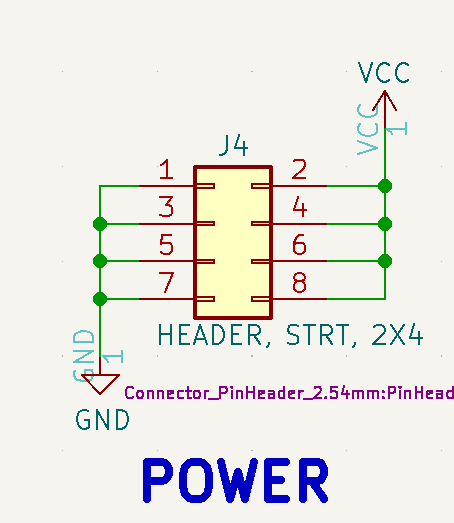

J4 - 5V Power

- 2x4 header

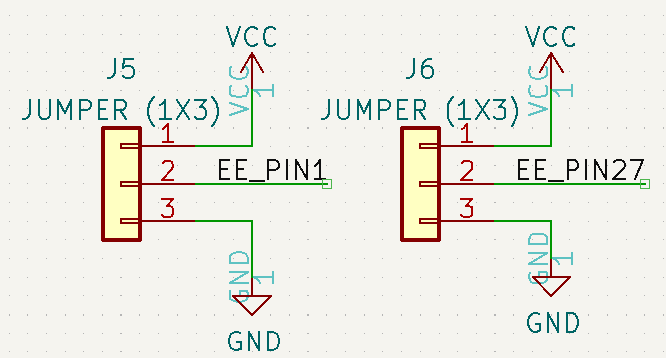

J5 / J6 - EPROM/EEPROM Select Jumpers

- J5 - EPROM Pin 1 jumper

- 1-2 for 28C64, 28C256 (Pull WE to VCC)

- 2-3 for 27256, 27SF256, 27512 (Pull A14 to GND)

- J6 - EPROM Pin 27 jumper

- GND (2-3)

EEPROM Pin Table

| 27512 | 27256 | 27SF256 | 28C256 | 27128 | 2764 | 28C64 | PIN | PIN | 2764 | 28C64 | 27128 | 28C256 | 27SF256 | 27256 | 27512 | |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| A15 | VPP | VPP | A14 | VPP | VPP | N/C | 1 | 28 | VCC | VCC | VCC | VCC | VCC | VCC | VCC | |

| A12 | A12 | A12 | A12 | A12 | A12 | A12 | 2 | 27 | PGM | WE* | PGM | WE* | A14 | A14 | A14 | |

| A7 | A7 | A7 | A7 | A7 | A7 | A7 | 3 | 26 | A13 | N/C | A13 | A13 | A13 | A13 | A13 | |

| A6 | A6 | A6 | A6 | A6 | A6 | A6 | 4 | 25 | A8 | A8 | A8 | A8 | A8 | A8 | A8 | |

| A5 | A5 | A5 | A5 | A5 | A5 | A5 | 5 | 24 | A9 | A9 | A9 | A9 | A9 | A9 | A9 | |

| A4 | A4 | A4 | A4 | A4 | A4 | A4 | 6 | 23 | A11 | A11 | A11 | A11 | A11 | A11 | A11 | |

| A3 | A3 | A3 | A3 | A3 | A3 | A3 | 7 | 22 | OE* | OE* | OE* | OE* | OE* | OE* | OE* | |

| A2 | A2 | A2 | A2 | A2 | A2 | A2 | 8 | 21 | A10 | A10 | A10 | A10 | A10 | A10 | A10 | |

| A1 | A1 | A1 | A1 | A1 | A1 | A1 | 9 | 20 | CE* | CE* | CE* | CE* | CE* | CE* | CE* | |

| A0 | A0 | A0 | A0 | A0 | A0 | A0 | 10 | 19 | D7 | D7 | D7 | D7 | D7 | D7 | D7 | |

| D0 | D0 | D0 | D0 | D0 | D0 | D0 | 11 | 18 | D6 | D6 | D6 | D6 | D6 | D6 | D6 | |

| D1 | D1 | D1 | D1 | D1 | D1 | D1 | 12 | 17 | D5 | D5 | D5 | D5 | D5 | D5 | D5 | |

| D2 | D2 | D2 | D2 | D2 | D2 | D2 | 13 | 16 | D4 | D4 | D4 | D4 | D4 | D4 | D4 | |

| GND | GND | GND | GND | GND | GND | GND | 14 | 15 | D3 | D3 | D3 | D3 | D3 | D3 | D3 |

JP1 - CPU Pin 1

- Install if CPU is not a WDC 65C02 or WDC 65C816

Software

- Link to Grant's files

- Source code

- osi_bas.s <== the Microsoft OSI BASIC and I/O routines SOURCE all in a single file

- Grant's I/O routines are at the end of it

- Files to allow the source to be assembled on a Windows based machine

- assemble.bat <== double click to assemble osi_bas.s and link to binary file "osi_bas.bin"

- This should be exactly 16K

- osi_bas.cfg <== configuration file for the linker (ensure ORG and entries in this file match if you change any)

- ca65.exe <== the assembler from the cc65 package. Use this. The new version on the cc65 site crashes!

- ld65.exe <== linker from the cc65 package

- Output files

- osi_bas.bin <== the ROM fine in pure binary

- osi_bas.lst <== Assembly listing file

- rom.hex <== the ROM fine in standard INTEL-HEX format

- To allow simple re-assembly, extract all files to the same folder

- Freeware utilities are available to convert the "bin" file to HEX or s19 (etc) - use your internet search tool to find

- All source code, assembler binaries and the HEX dump of the ROM is here

- It is in standard INTEL-HEX format for uploading to a suitable programmer.

First Unit Checkout (Rev 1 PCB)

Install Sockets

- Machined pin sockets

Install Passives

Power

- Install 2x4 at J4

- Power card via J4 with 5V

- Check power pins on parts

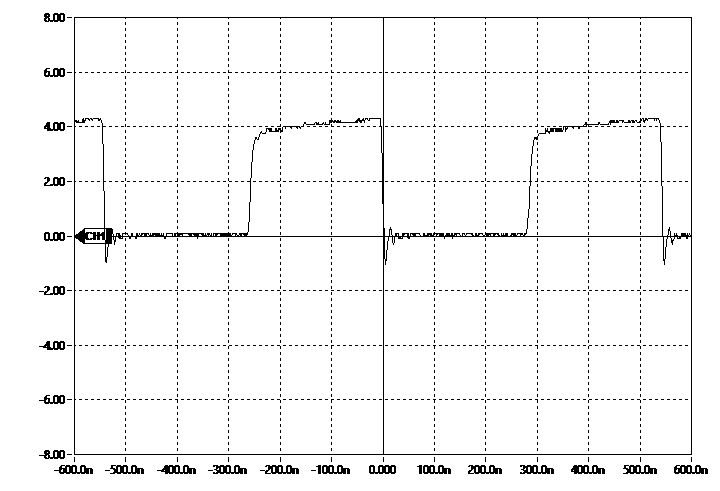

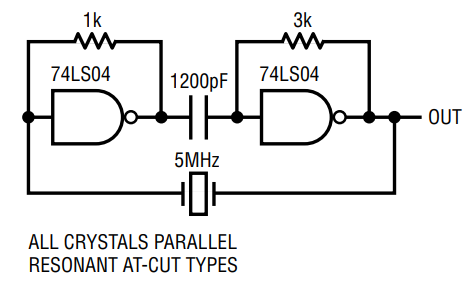

Clock

- Install Clock parts

- Did not have 270 pF cap, used 220 pF

- U7 (74HC04)

- Y1 1.8432 MHz crystal

- Clock "doubling" with 74HC04 part

- Worse with 74HC14

- Switched to 74LS04 - works well

- Install clock divider

- U8 (74HC74)

- Check clocks at J2

- Pin 1 s/b 0.9216 MHz

- Pin 3 s/b 1.8432 MHz

- Outputs are OK

- Need to change P/L and S/S to 74LS04

- Clock does not start up reliably

- Replaced part values with Fig 1d AN12 Circuit Techniques for Clock Sources

- Used 1nF cap instead of 1200pF

- Starts reliably but has a glitch

- Seems to run OK

- Reset is weird, sometimes does not boot and takes a couple of presses

- Not sure if this is clock related

- Order new 74LS04 parts

- See Rev 2 updates

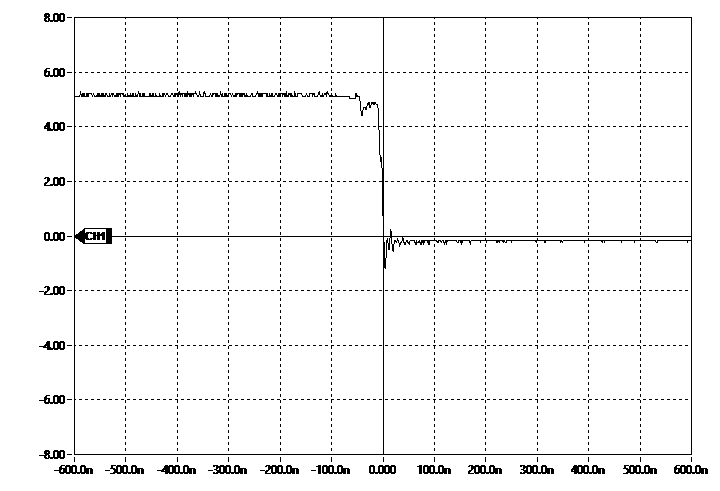

Reset

- Install U9

- Install pushbutton switch SW1

- Reset button gets stretched by Power Monitor U9

- Measure at 6502 U5 pin 40

- Falling edge scope cap

- Rising edge scope cap

- Switch failed, replaced - works

EPROM

- SST27C256 EEPROM

- 32 KB part

- Using first 16KB of EEPROM

- J5 EEPROM pin 1 = VPP = VCC or GND

- Jumper J5:2-3

- J6 EEPROM pin 27 = A14 = GND

- Jumper J6:2-3

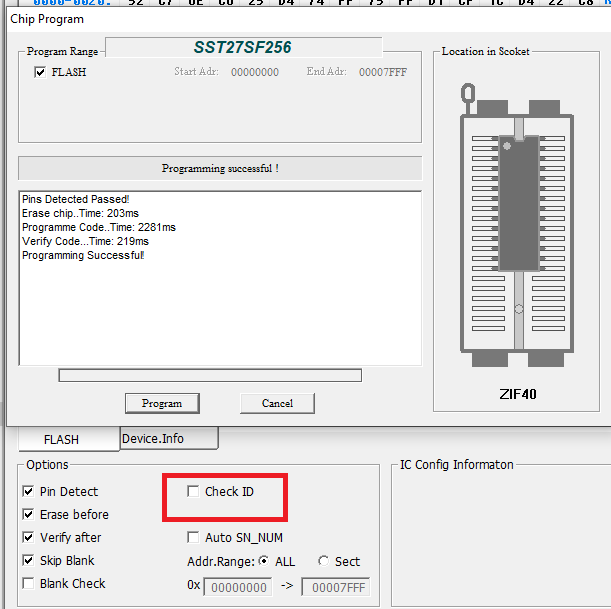

- U1 - Do not install MAX232

- Use FTDI connector with FTDI-49MM card

- R65C02 CPU

- Install JP1 on rear of card as wire

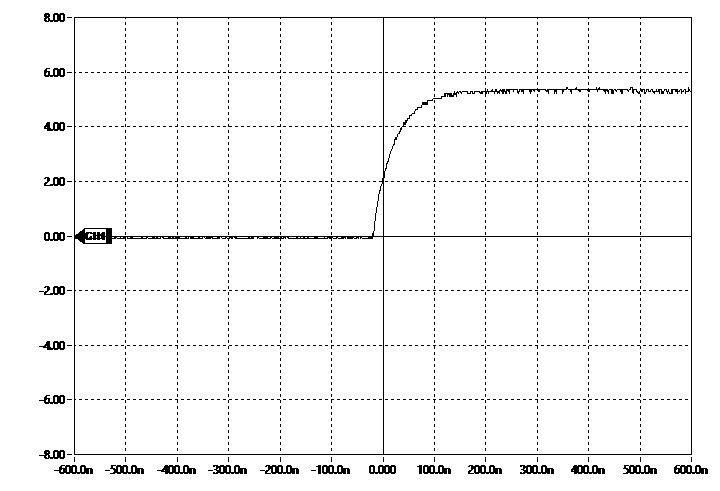

EEPROM Programming

- Program using TL-866ii plus programmer

- File = ROM.hex

- Got Device ID error

- Turn off ID check

- Device programmed/verified

Install CPU, ROM, RAM, ACIA

- Do not install MAX232 yet

- Use FTDI connector with FTDI-49MM card

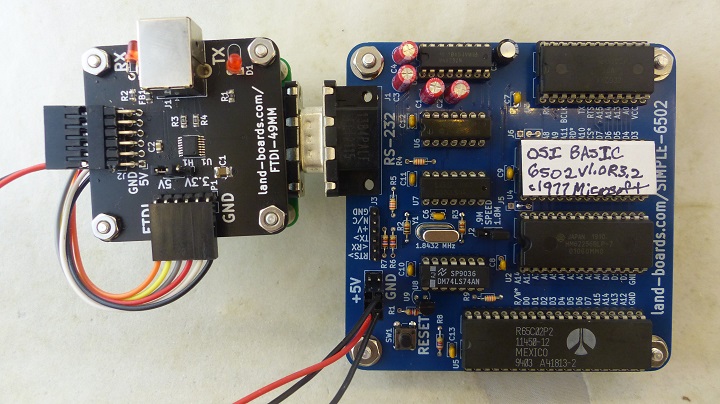

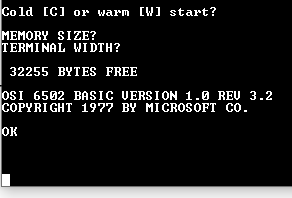

Test FTDI Serial

- Wiring is not 1:1 to FTDI-49MM

- Wire FTDI J3 to FTDI-49MM card

- Hardware handshake doesn't work with FTDI-49MM card

Card Without MAX232

- With DB-9 connector

- Install DB-9 Male

- Holes don't line up well, but 4-40 screws can fit

- Without MAX232

Built Card

- DB-9 connectors connected together

- Works

Performance

- TeraTerm settings

- Test software

10 FOR I =1 TO 10000 20 PRINT I 30 NEXT I

- Time ~38 secs

Mechanicals

- Rev 1 board

- Rev 2 board has the same mechanical dimensions, but some parts are different

PCB Issues

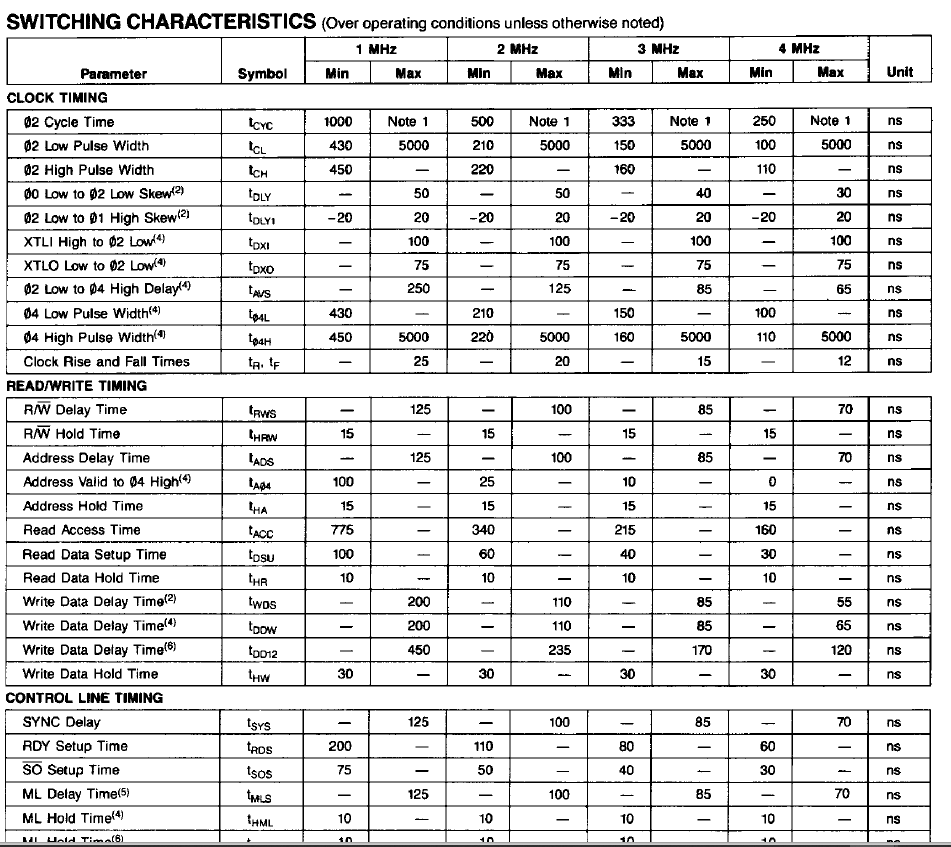

Rev 2

- See clock section above for issues found during Rev 1 board checkout

- R8, R9 missing 2.7K marking on silkscreen

- Updated on Rev 2 interactive BOM

- C6, C14 change value to 33 pF

- Symptom with 22 pF caps was wrong oscillation frequency (approx 2.1 MHz)

- Crystal is 18pF

- Matching caps should be 2x (since the caps are essentially in series

- 36pF would be right, but there's also pin and PCB capacitance so use 33 pF caps

- U7 has to be 74HC04 with these other value parts

- Measured oscillator circuit timing/voltages

Rev 1

- Clocking not optimal - see notes above in clock section for debug issues

Assembly Sheet

Assembly Sheet Rev 2

- SIMPLE-6502 Rev 2 Interactive BOM

- Install jumper JP1 on rear of board if CPU is not a WDC 65C02 or WDC 65C816

- Install jumpers J5-2 to -3 and J6-2 to -3

- Clock changes from Grant's design

- U7 is 74HC04 (silkscreen shows 74LS04)

- 74LS04 might work if the Resistor values in the clock circuit are changed

- Jumper J2 clock to run the CPU at either 1.8432 MHz or half speed 0.9216 MHz