Difference between revisions of "SIMPLE-68008"

Jump to navigation

Jump to search

Blwikiadmin (talk | contribs) |

Blwikiadmin (talk | contribs) |

||

| Line 183: | Line 183: | ||

===== PLD_002 Source Listing ===== | ===== PLD_002 Source Listing ===== | ||

| + | |||

| + | * [https://raw.githubusercontent.com/land-boards/lb-boards/master/RetroCPUs/SIMPLE-68008/LOGIC/SIMPLE-68008_PLD_2/SIMPLE-68008_PLD_2.PLD Source file] | ||

| + | * [https://raw.githubusercontent.com/land-boards/lb-boards/master/RetroCPUs/SIMPLE-68008/LOGIC/SIMPLE-68008_PLD_2/SIMPLE-68008_PLD_2.jed JEDEC Programming file] | ||

<pre> | <pre> | ||

Revision as of 14:18, 20 June 2024

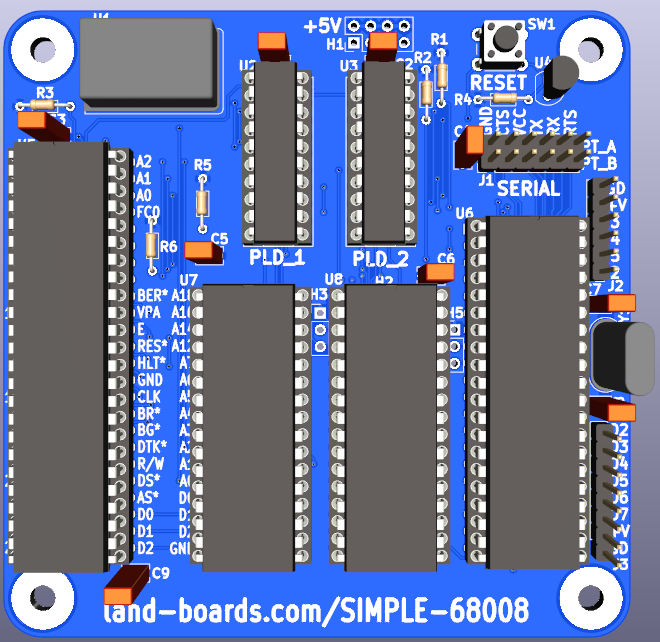

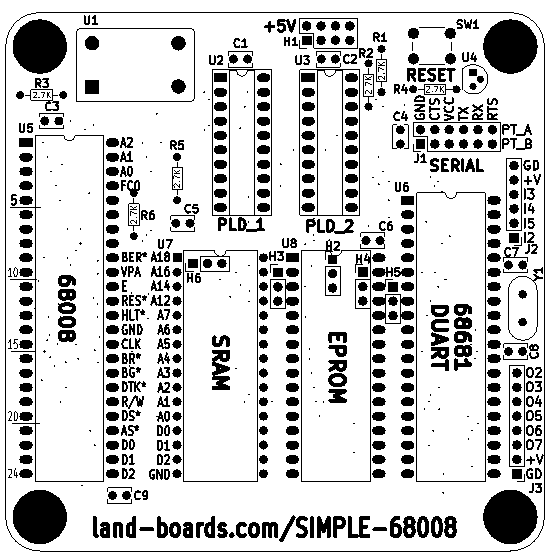

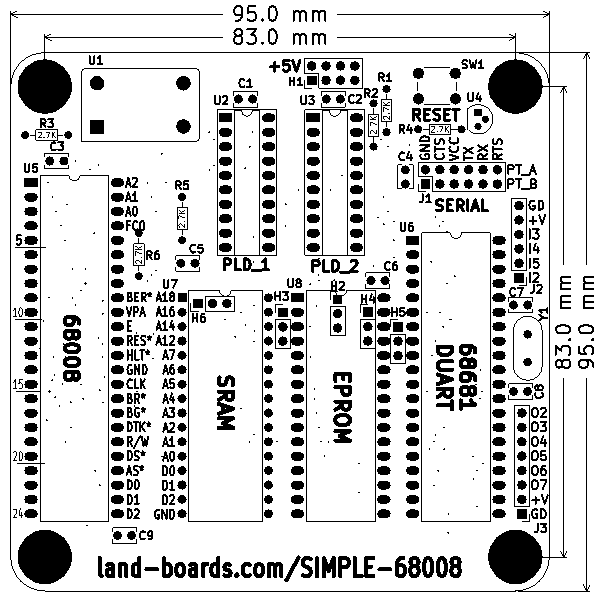

Features

- 68008 CPU

- 20 bit address space (1MB total)

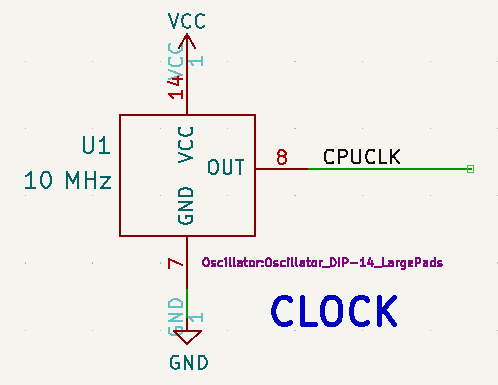

- 10 MHz clock

- Up to 512KB SRAM

- Up to 512KB EPROM/EEPROM

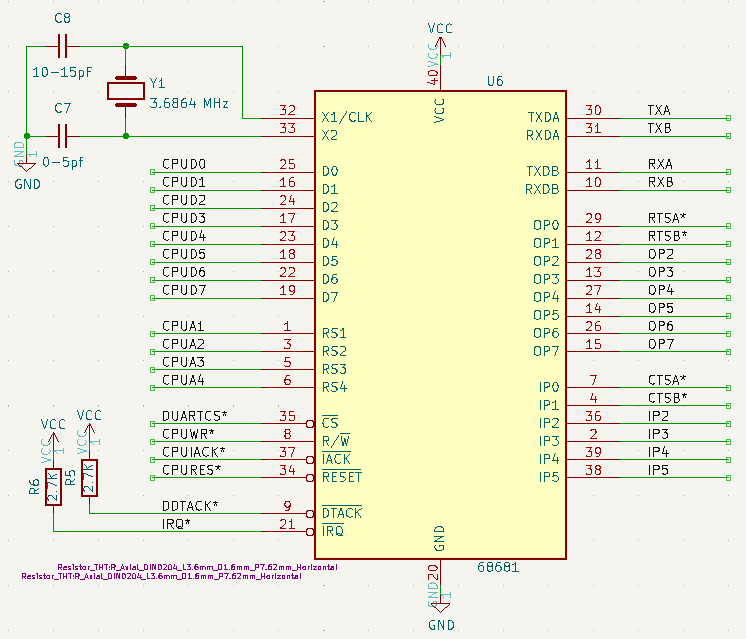

- 68681 Dual Serial Port (ACIA)

- Headers for FTDI

- 38,400 baud

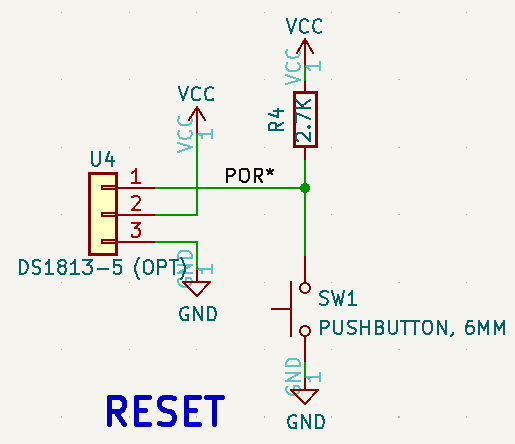

- Reset switch with optional Power Supervisor

- 95x95mm card

- (4) 6-32 mounting holes

Memory Map

- The memory map depends on two things

- Mapping in the PLDs

- The firmware that is being run on the card

Maximal Capacity Design

- 0x00000-0x7FFFF 512KB SRAM

- 0x80000-0xEFFFF Up to 448KB EPROM (minus DUART I/O space)

- 0xF0000-0xFFFFF Serial (ACIA)

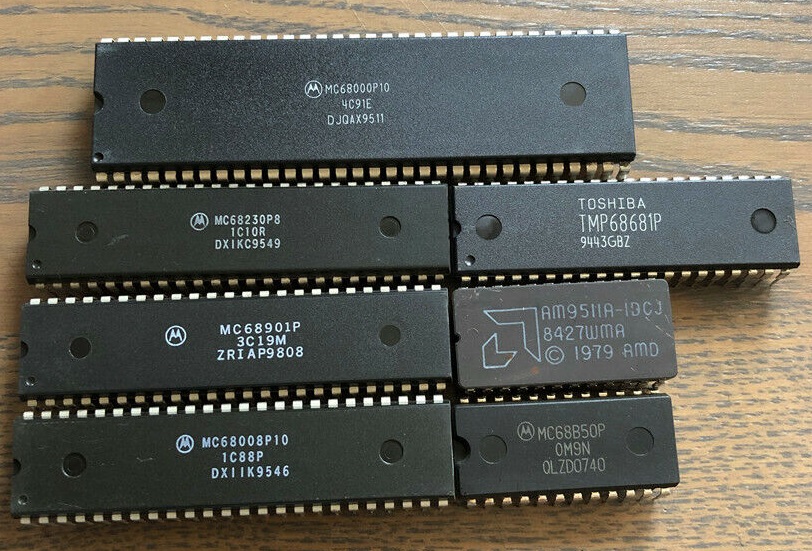

Chip Set

Parts in "Kit"

- MC68000P10 - 68K CPU with 16-bit data bus and 24-bit address bus

- MC68230P8 - Parallel I/O bits, timer

- TMP68681P - Dual UART, 8-bit I/O, 6-bit I/O

- MC68901P - Multifunction (8 I/O pins, interrupt controller, (4) timers, UART

- AM8511A - Floating Point Unit

- MC68008P10 - 68K CPU with 8-bit data bus and 20-bit address bus

- 65B50P - ACIA (Serial interface)

Design

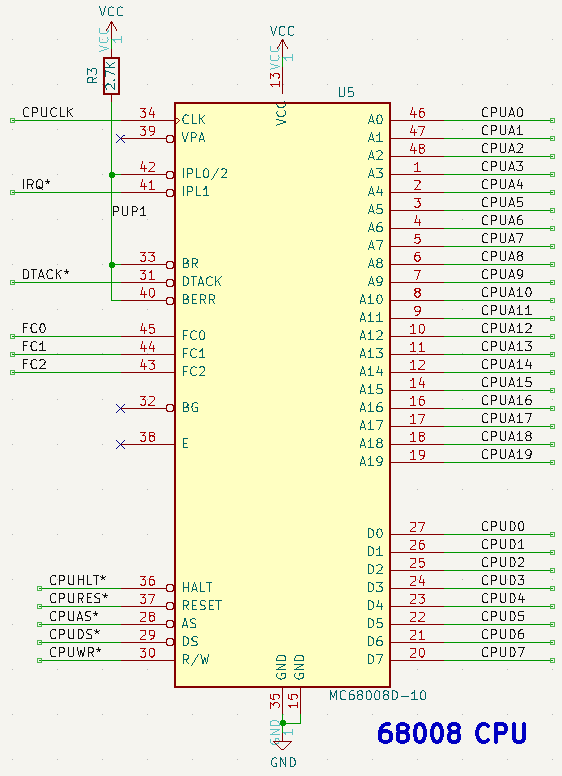

CPU

The Motorola 68008 is an 8/32-bit microprocessor introduced by Motorola in 1982. It is a version of 1979's Motorola 68000 with an 8-bit external data bus, as well as a smaller address bus. The 68008 was available with 20 address lines (48-pin package) which allowed 1 MB address space versus the 16 MB addressable on the 68000.

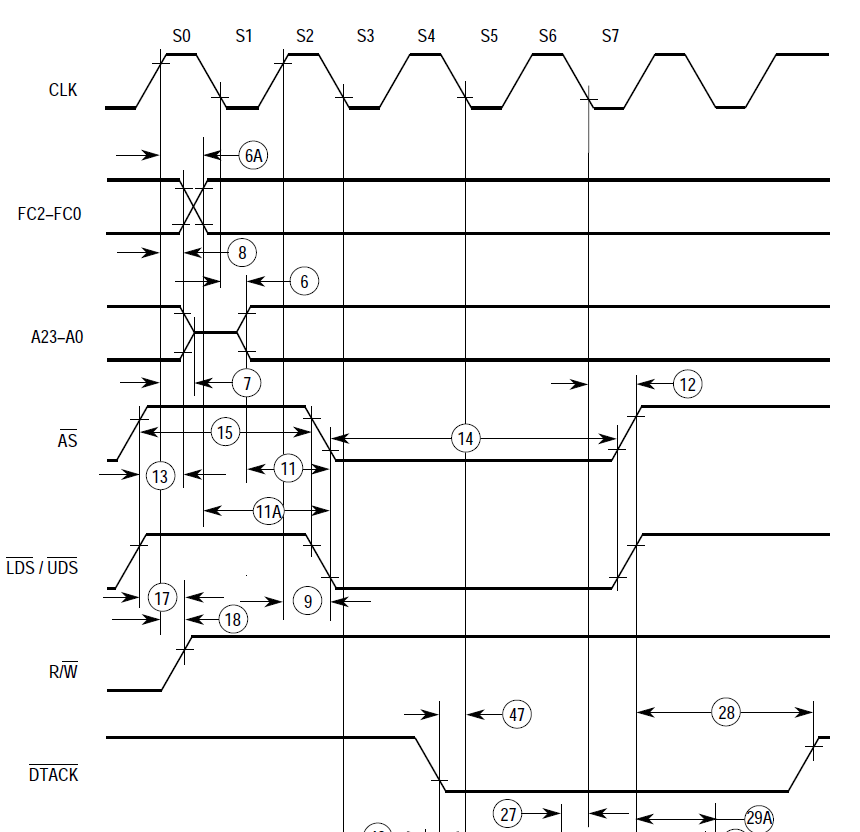

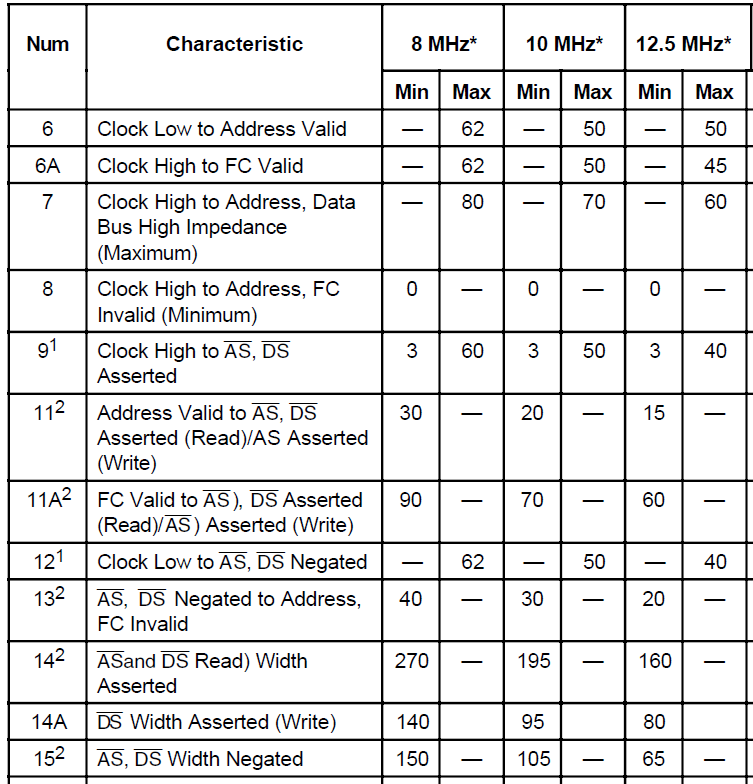

CPU Timing

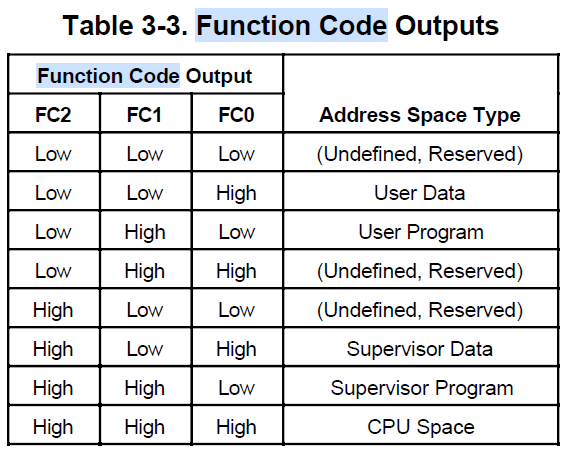

Function Code

EPROM

- SST27C256 EEPROM

- 32 KB part

- 28 pin part, 32 pin socket

EEPROM Programming

- Program using TL-866ii plus programmer

- File = TBD

- Set offsets for 27SF256 part

- Part is 32 KB

- hex files is 16 KB

- Set From File Start Addr(Hex) to 0C000

- To Buffer Start Addr(Hex) to 00000

TBD

- Memory Buffer should look like

TBD

- Got Device ID error

- Turn off ID check

TBD

- Device programmed/verified

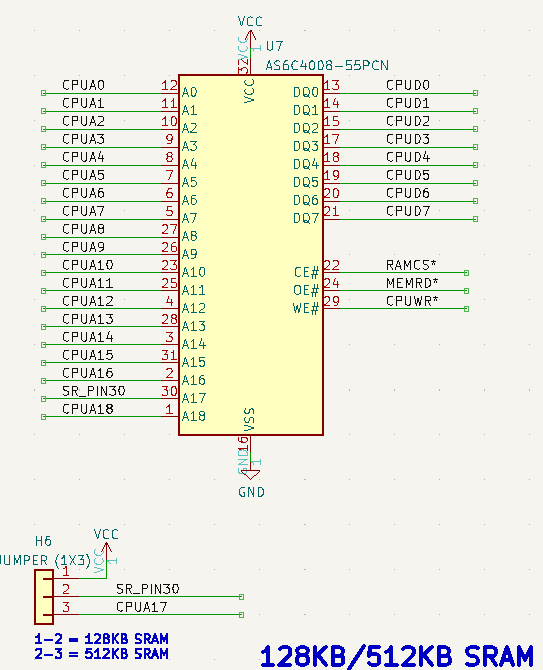

SRAM

- Using 512 KB SRAM

- Wire jumper H6-2 to H6-3 on rear of card

Dual UART

Reset

Clock

PLDs

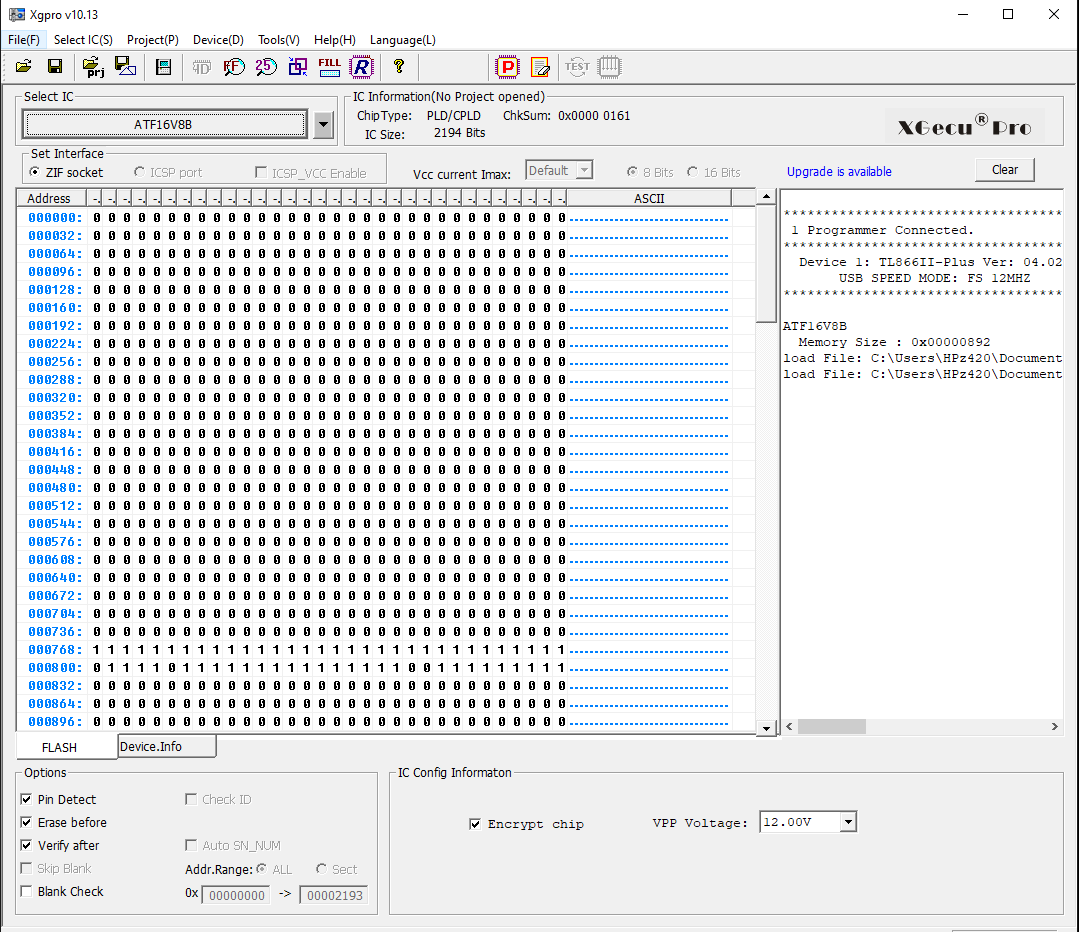

- Two ATF16V8B PLDs (Datasheet)

- WinCupl compiler

- Program using TL-866ii plus programmer

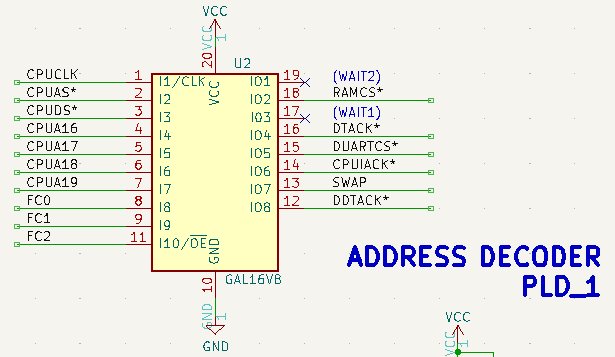

PLD_001

PLD_001 Source Listing

Name SIMPLE-68008_PLD_1; Partno ATF16V8B; Date 09/14/22; Revision 01; Designer DOUG G; Company LAND BOARDS LLC; Assembly U02; Location RUSTBELT, USA; Device G16V8; /* */ /* Inputs */ PIN 1 = CLK; PIN 2 = !CPUAS; PIN 3 = !CPUDS; PIN 4 = CPUA16; PIN 5 = CPUA17; PIN 6 = CPUA18; PIN 7 = CPUA19; PIN 8 = CPUFC0; PIN 9 = CPUFC1; PIN 11 = CPUFC2; PIN 12 = !DDTACK; PIN 13 = SWAP; /* Outputs */ PIN 14 = !CPUIACK; PIN 15 = !DUARTCS; PIN 16 = !CPUDTACK; PIN 17 = WAIT1; PIN 18 = !RAMSEL; PIN 19 = WAIT2; CPUIACK = CPUFC2 & CPUFC1 & CPUFC0 & CPUDS; DUARTCS = CPUA19 & CPUA18 & CPUA17 & CPUA16 & CPUDS & !CPUFC1 & CPUFC0; RAMSEL = !CPUA19 & SWAP & CPUDS & !CPUFC1 & CPUFC0 /* User/Super Data */ # !CPUA19 & SWAP & CPUDS & CPUFC1 & !CPUFC0; /* User/Super Program */ CPUDTACK = CPUA19 & CPUA18 & CPUA17 & CPUA16 & CPUDS & DDTACK /* DUART */ # CPUA19 & !CPUA18 & CPUDS /* EPROM */ # CPUA19 & !CPUA17 & CPUDS /* EPROM */ # CPUA19 & !CPUA16 & CPUDS /* EPROM */ # !CPUA19 & CPUDS; /* RAM */

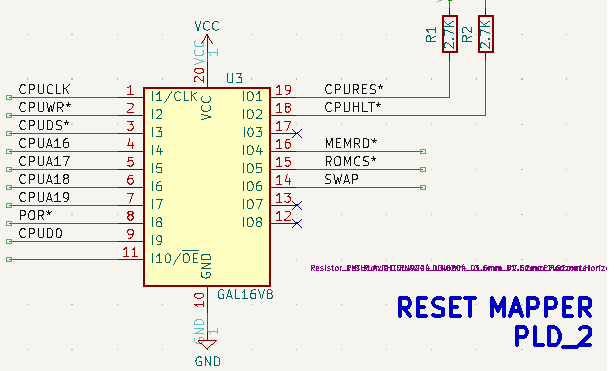

PLD_002

PLD_002 Source Listing

Name SIMPLE-68008_PLD_2; Partno ATF16V8B; Date 06/19/24; Revision 01; Designer DOUG G; Company LAND BOARDS LLC; Assembly U03; Location RUSTBELT, USA; Device G16V8; /* RESET CONTROLLER, ROM CHIP SELECT */ /* Inputs */ PIN 1 = CLK; PIN 2 = !CPUWR; PIN 3 = !CPUDS; PIN 4 = CPUA16; PIN 5 = CPUA17; PIN 6 = CPUA18; PIN 7 = CPUA19; PIN 8 = !POR; PIN 9 = CPUD0; /* Outputs */ PIN 14 = SWAP; PIN 15 = !ROMCS; PIN 16 = !MEMRD; PIN 18 = !CPUHLT; PIN 19 = !CPURES; /* CLEAR SWAP AT POWER UP, RESET */ /* SET SWAP BY FIRST WRITE TO START OF EPROM SPACE */ SWAP.D = CPUDS & CPUWR & CPUA19 & !CPUA18 & !CPUA17 & !CPUA16 & CPUD0 & !POR # SWAP & !POR; MEMRD = !CPUWR & CPUDS & !CPUA19 & SWAP; ROMCS = CPUDS & !CPUWR & CPUA19 & !CPUA18 # CPUDS & !CPUWR & CPUA19 & !CPUA17 # CPUDS & !CPUWR & CPUA19 & !CPUA16 # CPUDS & !CPUA19 & !CPUA18 & !CPUA17 & !CPUA16 & !SWAP; CPUHLT_N.OE = POR; CPUHLT_N = POR; CPURES_N.OE = POR; CPURES_N = POR;

Headers / Connectors

J1 - 2 port FTDI / TTL Serial

- 2x6 header

- Direct connect to DTE RS-232 card

- Flip order to connect to USB to TTL Serial (FTDI)

- TX<>RX

- RTS<>CTS

- Pinout

- GND

- CTS* (in)

- +5V

- Transmit (out)

- Receive (in)

- RTS* (out)

J2 - Input Port

- Input 2

- Input 5

- Input 4

- Input 3

- Vcc

- GND

J3 - Output Port

- GND

- Vcc

- Output 7

- Output 6

- Output 5

- Output 4

- Output 3

- Output 2

H1 - 5V Power

- 2x4 header

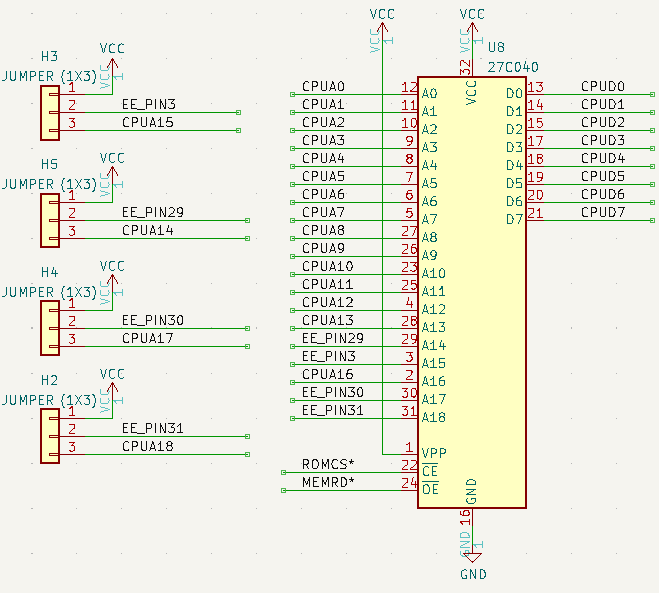

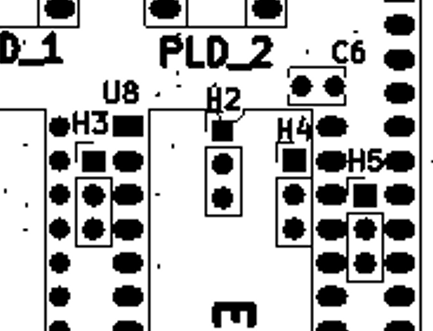

H2-H5 - EPROM/EEPROM Select Jumpers

- H2 = EE PIN 31

- H3 = EE PIN 3

- H4 = EE PIN 30

- H5 = EE PIN 29

27SF256

- 27SF256 is a 28 pin part, socket is 32 pins

- H2 = Not installed

- H3-1 to H3-2 = installed (Vpp = 5V)

- H4-1 to H4-2 = Vcc

- H5-2 to H5-3 = CPUA14

EEPROM Jumpers

| 27040 | 27020 | 27010 | 27512 | 27256 | 27128 | 2764 | PIN(32) | PIN(28) | PIN(28) | PIN(32) | 2764 | 27128 | 27256 | 27512 | 27010 | 27020 | 27040 | |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| VPP | VPP | VPP | N/A | N/A | N/A | N/A | 1 | N/A | N/A | 32 | N/A | N/A | N/A | N/A | VCC | VCC | VCC | |

| A16 | A16 | A16 | N/A | N/A | N/A | N/A | 2 | N/A | N/A | 31 (H2) | N/A | N/A | N/A | N/A | PGM | PGM | A18 | |

| A15 | A15 | A15 | A15 | VPP | VPP | VPP | 3 (H3) | 1 | 28 | 30 (H4) | VCC | VCC | VCC | VCC | N/C | A17 | A17 | |

| A12 | A12 | A12 | A12 | A12 | A12 | A12 | 4 | 2 | 27 | 29 (H5) | PGM | PGM | A14 | A14 | A14 | A14 | A14 | |

| A7 | A7 | A7 | A7 | A7 | A7 | A7 | 5 | 3 | 26 | 28 | A13 | A13 | A13 | A13 | A13 | A13 | A13 | |

| A6 | A6 | A6 | A6 | A6 | A6 | A6 | 6 | 4 | 25 | 27 | A8 | A8 | A8 | A8 | A8 | A8 | A8 | |

| A5 | A5 | A5 | A5 | A5 | A5 | A5 | 7 | 5 | 24 | 26 | A9 | A9 | A9 | A9 | A9 | A9 | A9 | |

| A4 | A4 | A4 | A4 | A4 | A4 | A4 | 8 | 6 | 23 | 25 | A11 | A11 | A11 | A11 | A11 | A11 | A11 | |

| A3 | A3 | A3 | A3 | A3 | A3 | A3 | 9 | 7 | 22 | 24 | OE* | OE* | OE* | OE* | OE* | OE* | OE* | |

| A2 | A2 | A2 | A2 | A2 | A2 | A2 | 10 | 8 | 21 | 23 | A10 | A10 | A10 | A10 | A10 | A10 | A10 | |

| A1 | A1 | A1 | A1 | A1 | A1 | A1 | 11 | 9 | 20 | 22 | CE* | CE* | CE* | CE* | CE* | CE* | CE* | |

| A0 | A0 | A0 | A0 | A0 | A0 | A0 | 12 | 10 | 19 | 21 | D7 | D7 | D7 | D7 | D7 | D7 | D7 | |

| D0 | D0 | D0 | D0 | D0 | D0 | D0 | 13 | 11 | 18 | 20 | D6 | D6 | D6 | D6 | D6 | D6 | D6 | |

| D1 | D1 | D1 | D1 | D1 | D1 | D1 | 14 | 12 | 17 | 19 | D5 | D5 | D5 | D5 | D5 | D5 | D5 | |

| D2 | D2 | D2 | D2 | D2 | D2 | D2 | 15 | 13 | 16 | 18 | D4 | D4 | D4 | D4 | D4 | D4 | D4 | |

| GND | GND | GND | GND | GND | GND | GND | 16 | 14 | 15 | 17 | D3 | D3 | D3 | D3 | D3 | D3 | D3 |

H6 - SRAM Configuration

Software

- TUTOR 1.2 Monitor

- Addressing issues due to code being designed for ROM at below 64K

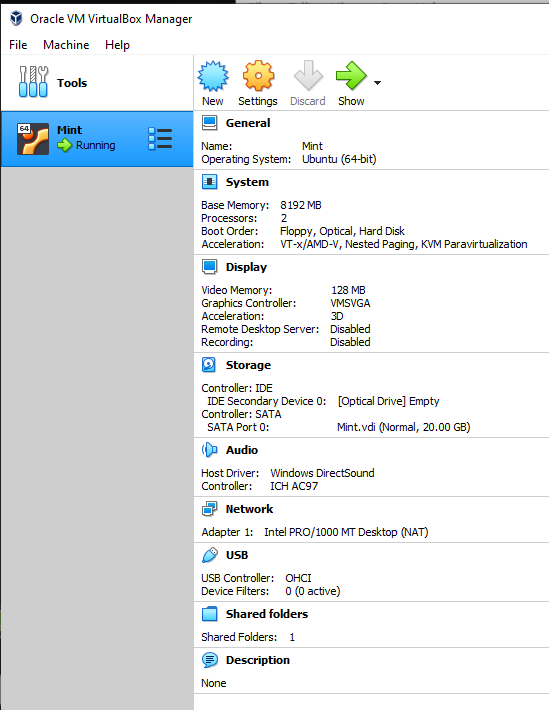

Linux Development Environment

- Using Oracle VM VirtualBox

- Running Linux Mint

- The GNU C-Compiler with Binutils and other useful tools for 68000 cross development

- This is a Makefile based approach to build the toolchain to reduce the build time.

- The original work was by Steve Moody Moody's page

- These tools are build:

- binutils

- gcc with libs for C/C++/ObjC

- vasm

- vbcc

- vlink

- newlib