Difference between revisions of "LB-6809-01"

Jump to navigation

Jump to search

Blwikiadmin (talk | contribs) |

Blwikiadmin (talk | contribs) |

||

| Line 317: | Line 317: | ||

* Missing D0 on PLD pin 11 | * Missing D0 on PLD pin 11 | ||

** Add wire U1-31 to U2-11 (CPUD0) | ** Add wire U1-31 to U2-11 (CPUD0) | ||

| + | ** Fixed without a wire | ||

| + | *** Write to 0xE000 clears LED (data = don't care) | ||

| + | *** Write to 0xC000 sets LED (data = don't care) | ||

| + | ** Example code | ||

| + | <pre> | ||

| + | 10 POKE 57344,0 | ||

| + | 20 GOSUB 1000 | ||

| + | 30 POKE 49152,0 | ||

| + | 40 GOSUB 1000 | ||

| + | 50 GOTO 10 | ||

| + | 1000 FOR I=0 TO 1000:NEXT I | ||

| + | 1010 RETURN | ||

| + | </pre> | ||

=== Rev 3 PCB Changes === | === Rev 3 PCB Changes === | ||

Revision as of 13:13, 18 October 2024

Contents

- 1 Features

- 2 Design

- 3 Software

- 3.1 Build 6809 Assembly Code (Windows 64-bit)

- 3.2 Other Tools

- 3.3 Programming using TL866

- 3.4 ROM access test code (loop.asm)

- 3.5 LED Blink code (blink.asm)

- 3.6 SRAM Test (ramLoop.asm)

- 3.7 SRAM Test (ramTest1.asm)

- 3.8 SRAM Test (ramTest.asm)

- 3.9 ACIATest.asm

- 3.10 Microsoft Extended BASIC

- 3.11 ASSIST-09 Debugger

- 3.12 ASSIST-09 Plus Microsoft Extended BASIC

- 3.13 Reference Designs

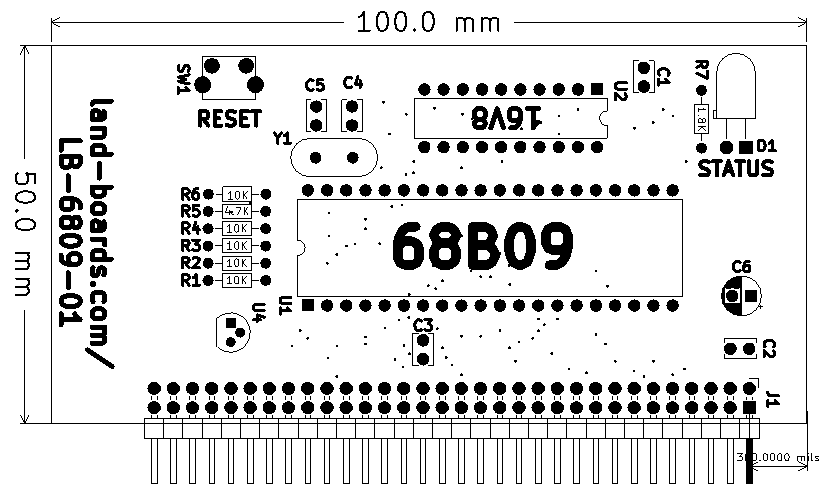

- 4 Mechanicals

- 5 Checkout

- 6 Assembly Sheet

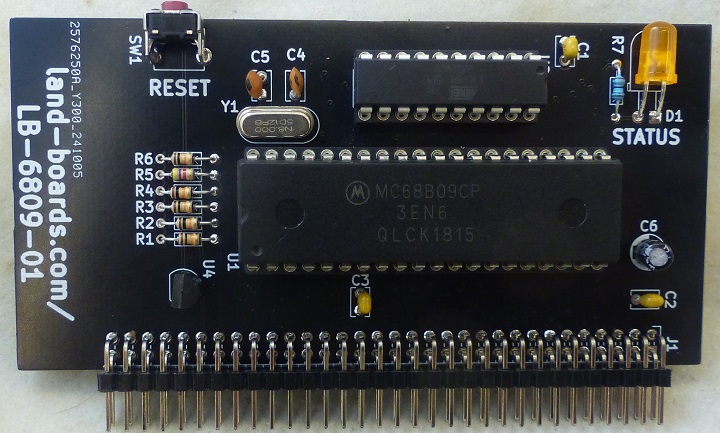

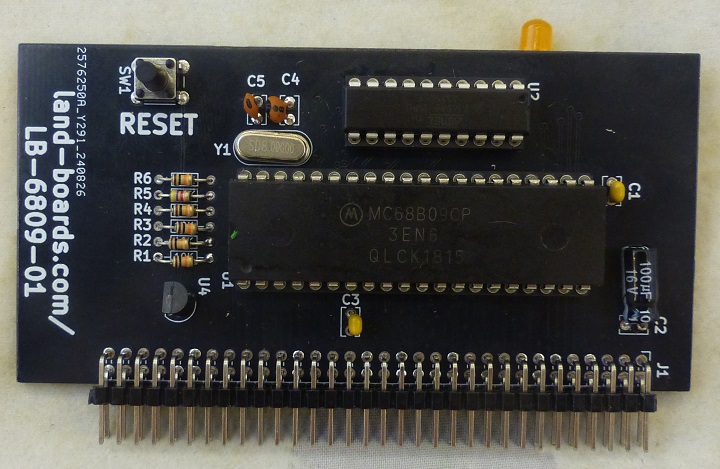

Features

- 68B09 CPU

- 8 MHZ crystal on card

- CPU runs at 2 MHz

- Reset switch/power monitor

- Address decoder PLD drives RAM/ROM/IO chip selects

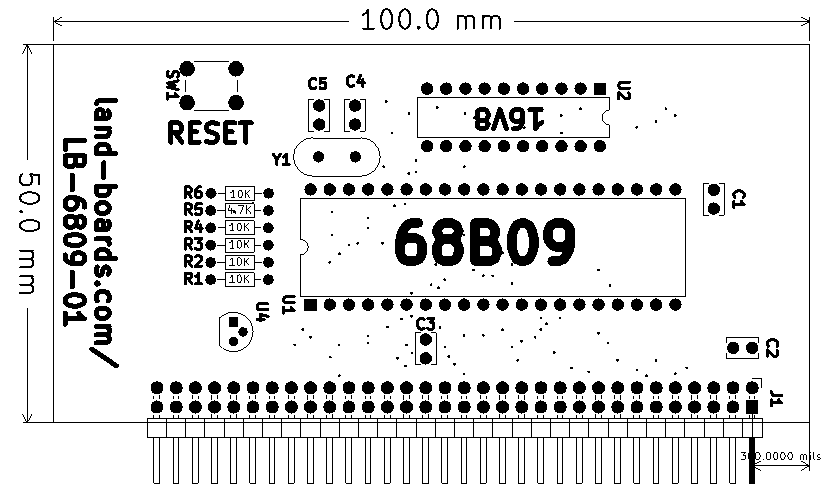

- 100x50mm card

Memory Map

- 0x0000-0x7FFF 32KB SRAM

- 0x8000-0x9FFF Free Space (8KB)

- Could be mapped in the PLD to EPROM or SRAM (with LB-MEM-04 card)

- 0xA000-0xBFFF Serial (ACIA)

- Could be reduced to 4K range in the PLD freeing up 4 KB for SRAM or EPROM

- 0xC000-0xFFFF 16KB EPROM

Design

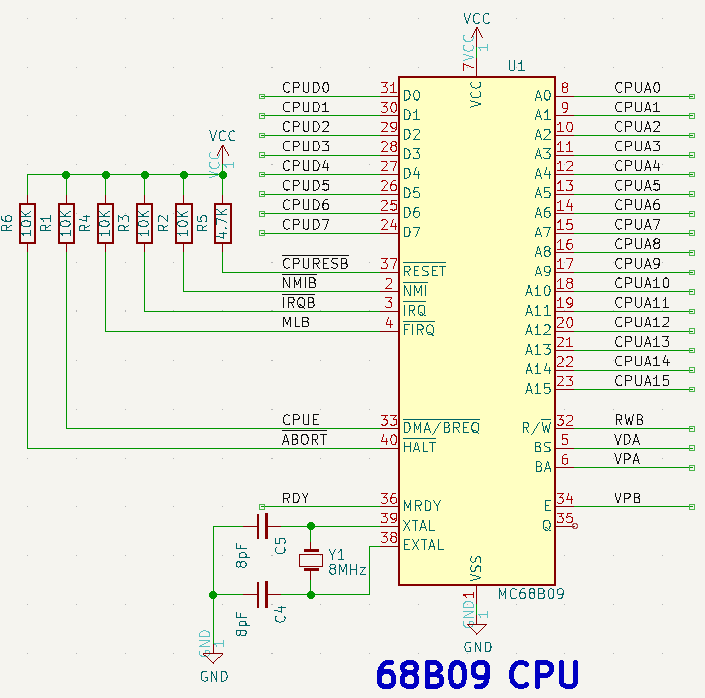

68B09 CPU

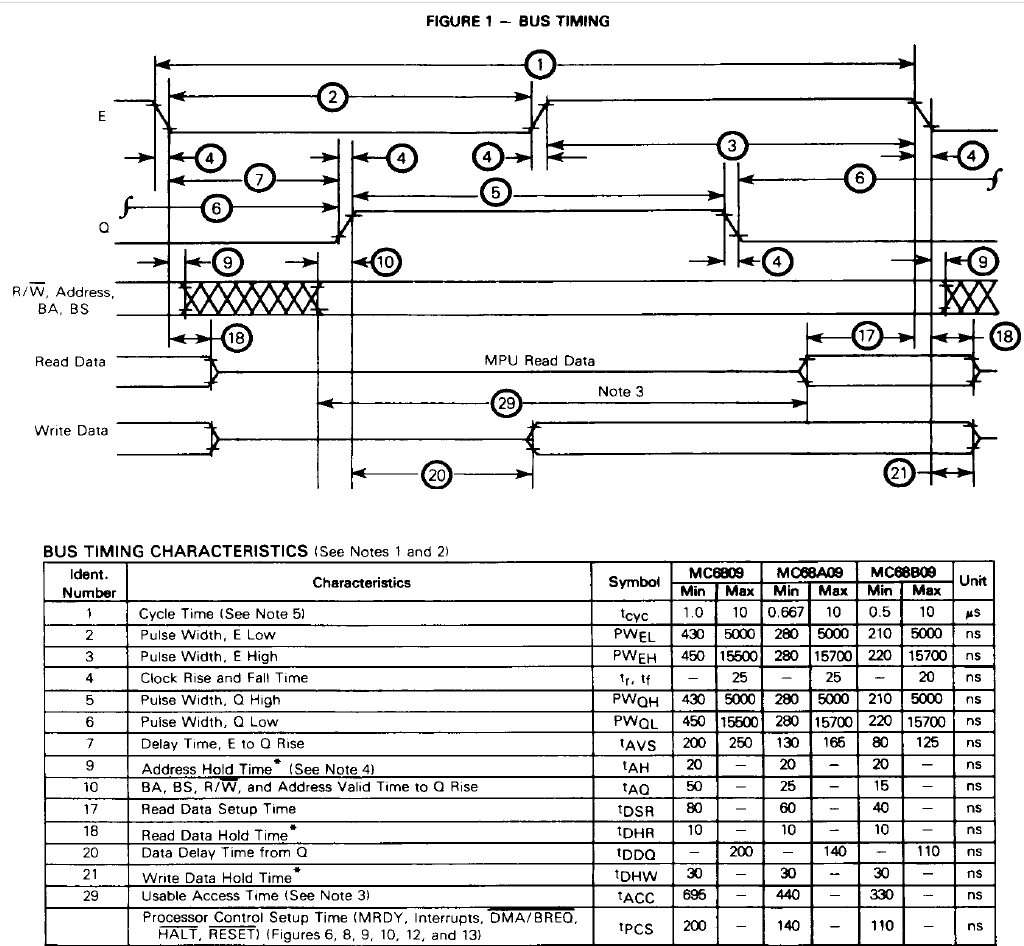

- 8 MHz clock using crystal and built-in oscillator

- Runs effectively at 2 MHz

CPU

CPU Timing

Clock

Crystal

- Uses CPU internal oscillator

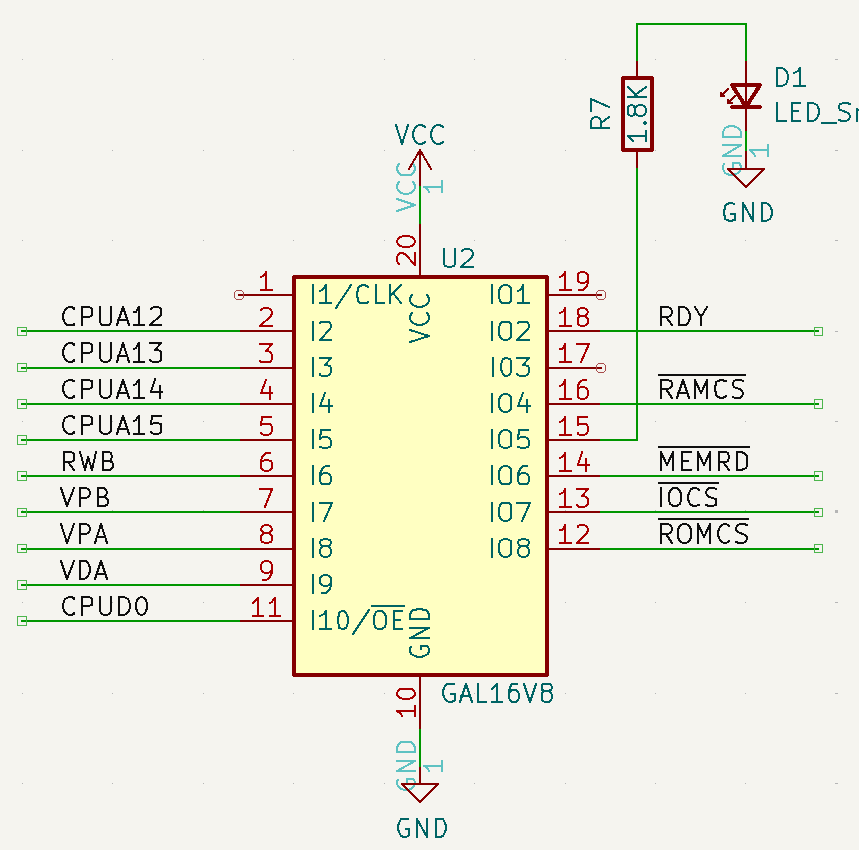

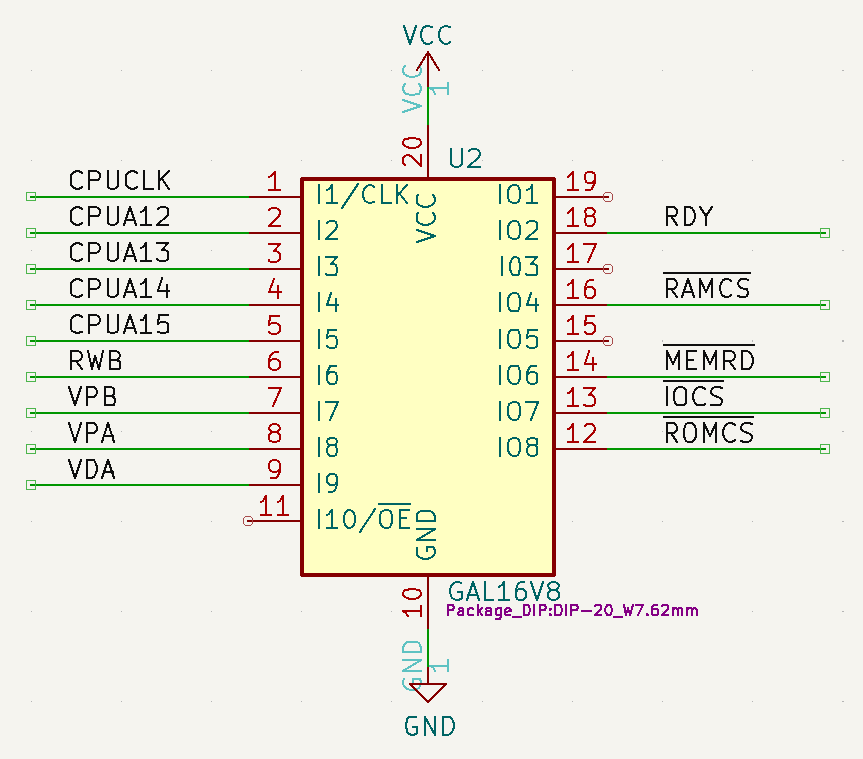

PLD

- ATF16V8B part

- TL866ii Plus Programmer

PLD Listing

- Latest PLD source code here

- Added code to blink LED

Name LB-6809-01_PLD; Partno ATF16V8B; Date 10/15/24; Revision 01; Designer DOUG G; Company LAND BOARDS LLC; Assembly LB680901_U2; Location Rustbelt, US; Device G16V8; /* */ /* Control inputs */ PIN 2 = CPUA12; PIN 3 = CPUA13; PIN 4 = CPUA14; PIN 5 = CPUA15; PIN 6 = CPUREAD; PIN 7 = VPB; /* Added as wire on Rev 1 PCB */ PIN 8 = VPA; PIN 9 = VDA; PIN 11 = D0; /* Address Decode and Chip Select outputs */ PIN 12 = !ROMCS; PIN 13 = !IOCS; PIN 14 = !MEMRD; PIN 15 = LED; PIN 16 = !RAMCS; PIN 18 = RDY; ROMCS = CPUA15 & CPUA14 & CPUREAD; /* 0xC000-0xFFFF */ RAMCS = !CPUA15 & CPUREAD /* 0x0000-0x7FFF 32KB SRAM */ # !CPUA15 & !CPUREAD & VPB; IOCS = CPUA15 & !CPUA14 & CPUA13 & CPUREAD /* 0xA000-0xBFFF Serial (ACIA) */ # CPUA15 & !CPUA14 & CPUA13 & !CPUREAD & VPB; RDY = VPB; MEMRD = CPUREAD; LED = CPUA15 & CPUA14 & !CPUREAD & VPB & D0 # LED & !(CPUA15 & CPUA14 & !CPUREAD & VPB);

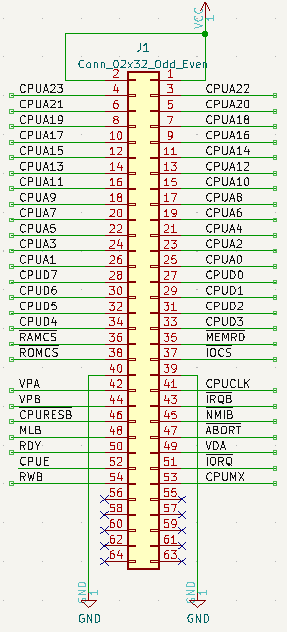

Backplane connector

Software

- LB-6809 code examples

- asm6809 - portable cross assembler targeting the Motorola 6809

- Features arbitrarily complex expressions (with most C-style operators available), forward references, macro expansion and conditional assembly

- Output formats are: Motorola SREC, Intel HEX (and others)

- asm6809 Manual

- Using asm6809 version 2.13

- asm6809-2.13-w64 Local copy

- MC6809-MC6809E 8-Bit Microprocessor Programming Manual (M6809PM/AD) © Motorola Inc., 1981

- MC6809 Reference Card

Build 6809 Assembly Code (Windows 64-bit)

- Run asm6809 in Windows CMD prompt window

[path_to_asm6809.exe_program\]asm6809 loop.asm -H -l -o loop.hex

- -H option creates hex record file to download to programmer

- -l fileName option creates listing file

- -o filename option followed by output file name

Other Tools

- Motorola 6809 Emulator

- LWTOOLS Assembler

- [AS9 Assembler http://home.hccnet.nl/a.w.m.van.der.horst/m6809.html]

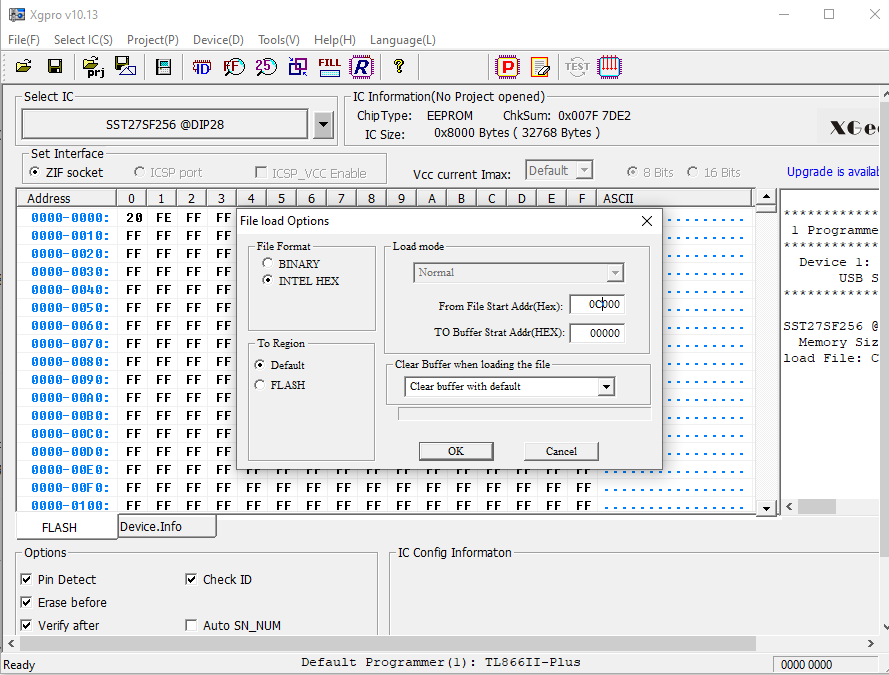

Programming using TL866

- Set From File Start(Hex) to 0x0C000 when loading hex record file into TL866i Plus programmer

ROM access test code (loop.asm)

- Assemble loop.asm

- my path below, YMMV

..\..\M6809_Assembler\asm6809-2.13-w64\asm6809 loop.asm -H -l loop.lst -o loop.hex

- Source code (loop.asm)

ORG $C000 RESVEC BRA RESVEC ORG $FFFE LBFFE FDB RESVEC ; RESET

- .hex file

:02C0000020FE20 :02FFFE00C00041 :00000001FF

LED Blink code (blink.asm)

- Added PLD code to make a trigger on pin 17 when EPROM address 0xC000-0xF000 is written

- Code doesn't use any RAM (CPU and EPROM only)

- LED is on U2-15 to GNS w/ 1.8K resistor

- Assemble blink.asm code

- See Rev 2 checkout notes for LED

- my path below, YMMV

..\..\M6809_Assembler\asm6809-2.13-w64\asm6809 blink.asm -H -l blink.lst -o blink.hex

- Works, blinks LED at about 2 Hz

- Can use this as a SRAM test outout

- Fast blink = Fail

- Slow blink = Pass

SRAM Test (ramLoop.asm)

- ramLoop.asm - GitHub

- Loops on SRAM write/read on LB-6809-01 card

- Turn on LED if the test passes

- Turn off LED if the test fails

- Passes

SRAM Test (ramTest1.asm)

- ramTest1.asm - GitHub

- Write/read SRAM write/read single location on LB-MEM-02 card

- Blink LED slowly if the test passes

- Blink LED quickly if the test fails

- Passes

SRAM Test (ramTest.asm)

- ramTest.asm - GitHub

- Write/read SRAM write/read on all SRAM on LB-MEM-02 card

- Test single location with 0x55/0xaa

- Test all RAM with ramp

- Tests all locations but repeats ever 256 bytes so addresses are not completely tested

- Ramp upper 7 address lines with a ramp

- Blink LED slowly if the test passes

- Blink LED quickly if the test fails

- Test takes 0.6 secs

- Passes

ACIATest.asm

- AciaTest.asm

- Wrote code with Microsoft Pilot with minor modifications

- Required etch cut and added wire on LB-68B50-02 Rev 1 card

- Test with FTDI-49MM card

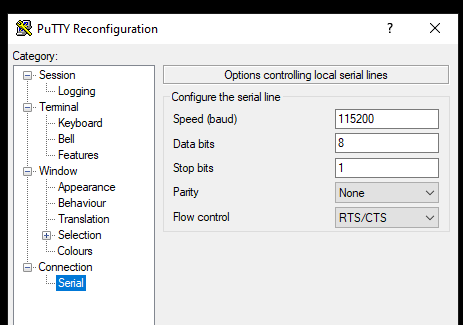

- 115,200 baud, No parity ,8 data bits, 1 stop bit

- Loops back data typed in

- Works

Microsoft Extended BASIC

- Based on Grant Searle's 6-chip 6809 computer

- Microsoft Extended BASIC, as used in the Tandy Coco 2 (modified for the SBC with all I/O via serial)

- MBasROM.hex

- Hex file for 27C512

- First three 16KB sections are filled with 0xFF

- Hex file for 27C512

- 115,200 BAUD

- Same build as SIMPLE-6809 from Grant Searle

- Grant wrote a serial handler to control the text I/O, along with suitable Control-C break handling

- Includes commands from the "Extended" BASIC ROM (from the "Extended BASIC Unraveled II" book)

- The ROM in the SBC is fully working with all the commands in the Standard and Extended ROMS that are applicable to the SBC

- BASIC from DB00 TO FFFF, so a large amount of free space suitable for a monitor etc (6912 bytes free)

- Works

6809 EXTENDED BASIC (C) 1982 BY MICROSOFT OK

- PuTTY settings

- Test software

10 FOR I=1 TO 10000 20 PRINT I 30 NEXT I

- Time ~49 secs

ASSIST-09 Debugger

- ASSIST-09 for the 6850 ACIA (source code)

- Debugger with small command set

- ASSIST-09 Commands

- Includes S record loader

- Altered source code to assemble using asm6809

- Period can't be first character on label (changed to X)

- Changed opcode CPX > CMPX

- assist09-6850.hex file

- Command line to assemble code

..\..\M6809_Assembler\asm6809-2.13-w64\asm6809 assist09-6850.asm -H -l assist09-6850.lst -o assist09-6850.hex

- Works

ASSIST09 >R PC-F842 A-00 B-00 X-20FE Y-F002 U-60C2 S-6051 CC-F4 DP-00 PC- >

ASSIST-09 Plus Microsoft Extended BASIC

- Jeff Tranter combined the ASSIST-09 and Ext BASIC source codes

- Assist_MBasic files on GitHub

- Debugger with small command set

- Adds U (Unassemble command)

- ASSIST-09 Commands

- Includes S record loader

- G C000 to run Extended BASIC

- Works

Reference Designs

- MP-09 MONITOR - SWTBUG SBUG monitor for the 6809

- SIMPLE-6809 Software - reference software that runs on SIMPLE-6809

Mechanicals

Rev 2

Checkout

Rev 3 Checkout

- Missing D0 on PLD pin 11

- Add wire U1-31 to U2-11 (CPUD0)

- Fixed without a wire

- Write to 0xE000 clears LED (data = don't care)

- Write to 0xC000 sets LED (data = don't care)

- Example code

10 POKE 57344,0 20 GOSUB 1000 30 POKE 49152,0 40 GOSUB 1000 50 GOTO 10 1000 FOR I=0 TO 1000:NEXT I 1010 RETURN

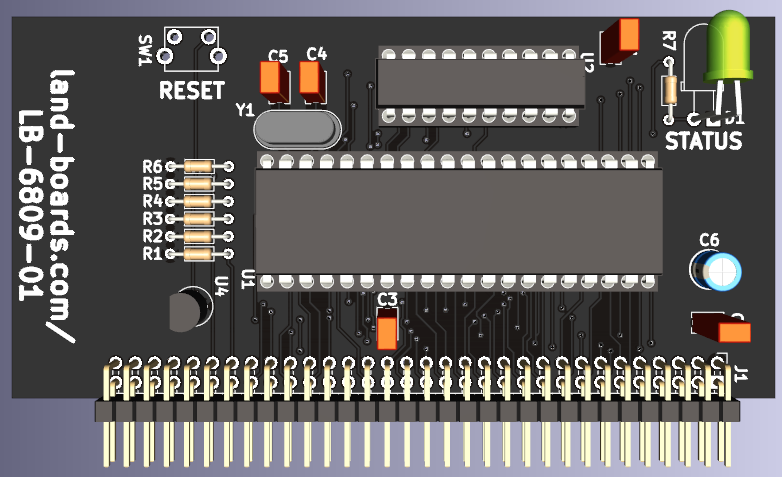

Rev 3 PCB Changes

- Added LED to U2-15

- Silkscreen = STATUS

- Changed reset switch to right angle pushbutton switch

- Can be pressed easier in the backplane

- Added bulk electrolytic capacitor

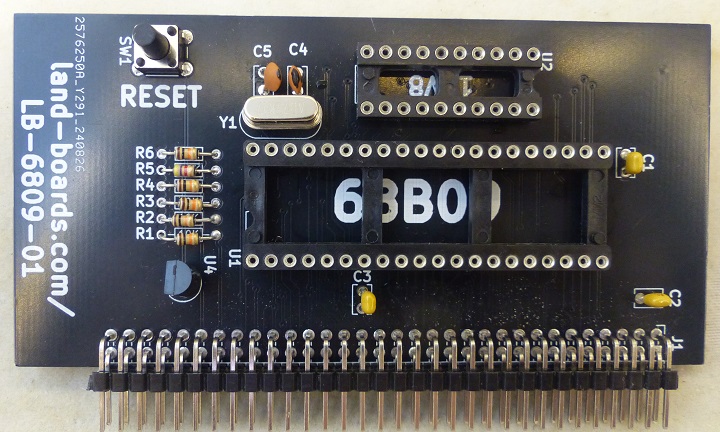

Rev 2 Checkout

- Board with sockets (machine pin)

- Built

- Worked with NOP Tester

- Got 8 MHz crystal

- E signal is 2 MHz- good

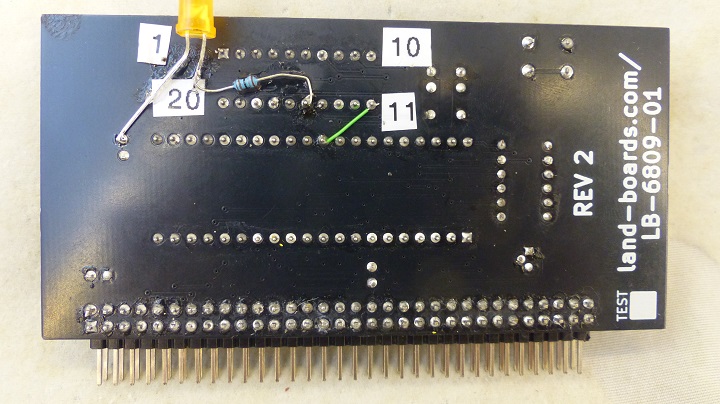

- Add LED that can be written under program control

- Add wire U1-31 to U2-11 (D0)

- Add LEDSTR when strobe write to 0xC000-0xFFFF (U2-17)

- Add LED to U2-15 with 1.8K resistor

- Write to 0xF000 to toggle the line

- Bit D0

- Running blink.asm code

- Replaced C2 cap with electrolytic bulk cap

Rev 2 PCB Changes from Rev 1

- Add U1-34 to U2-7 (VPB/E)

- Eliminate oscillator

- Add 8 MHz crystal/caps

- Cheaper and easier to find

- Add 4.7K pullup to U1-40 (ABORT*/HALT) line

- Change resistor values to lighten up Iol

- Beef up power plane connections to J1 and CPU/cap

- Move reset switch to the top of the board (where the oscillator used to be)

Rev 1 Checkout Notes

- Did not build

- Add wire U1-34 to U2-7 (VPB/E)

- Ground XTAL pin on CPU U1-39 (to U1-1 = GND)

- Use BOM for resistor values, not silkscreen

- Add 4.7K pullup to ABORT* line

Assembly Sheet

Rev 3

Rev 2

Rev 1

- Use BOM for resistor values, not silkscreen

- Interactive BOM