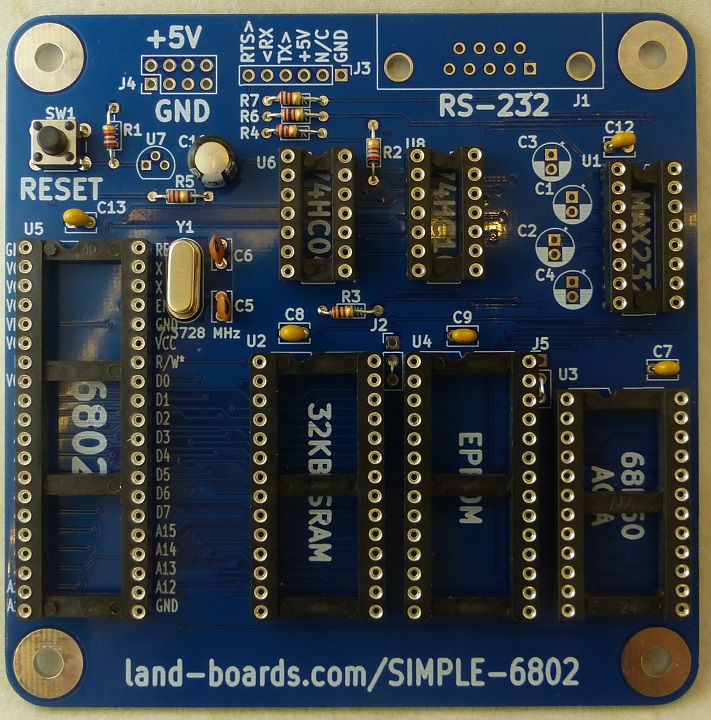

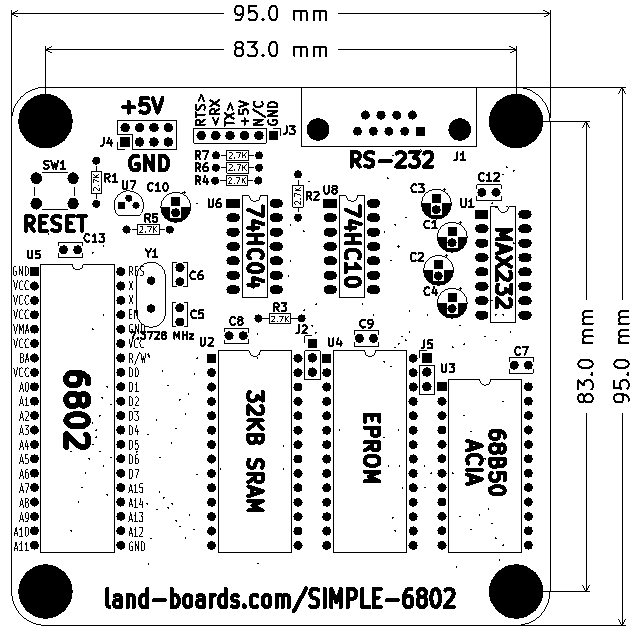

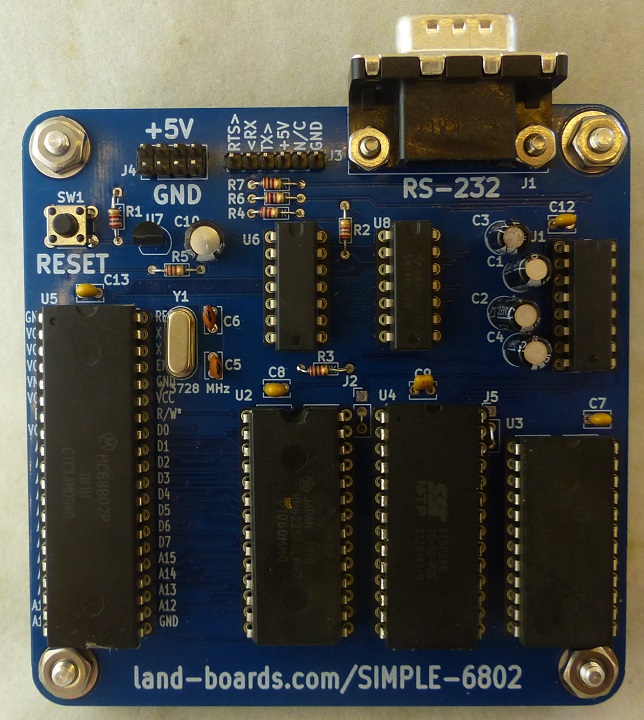

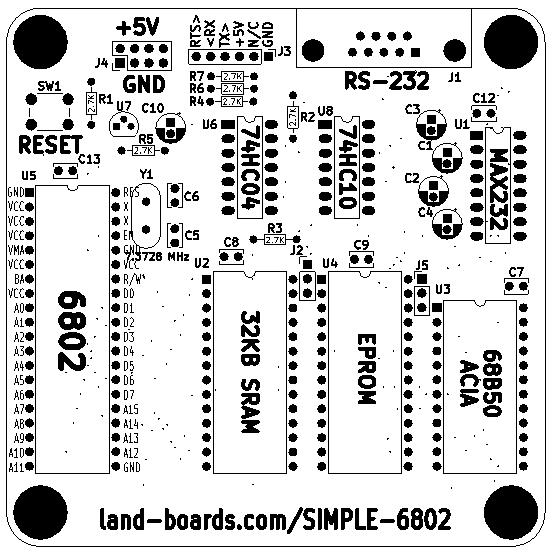

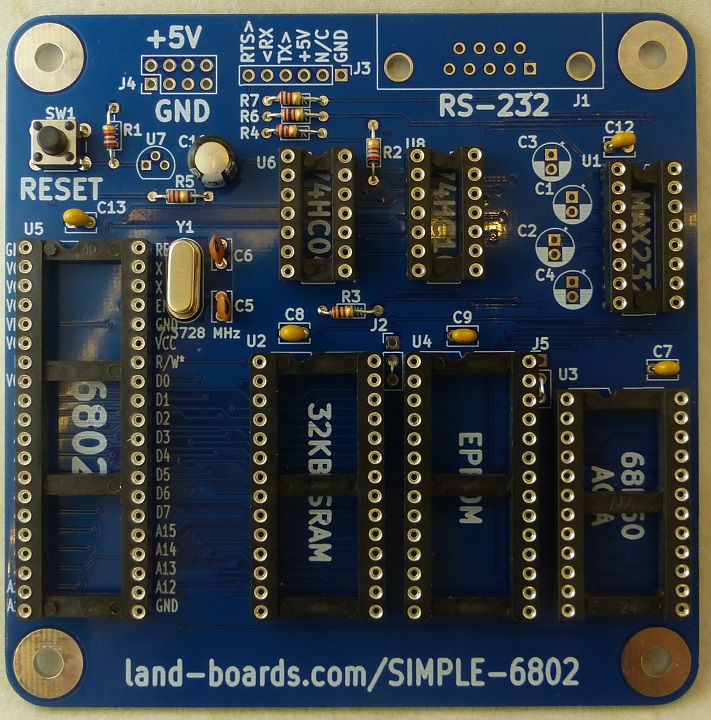

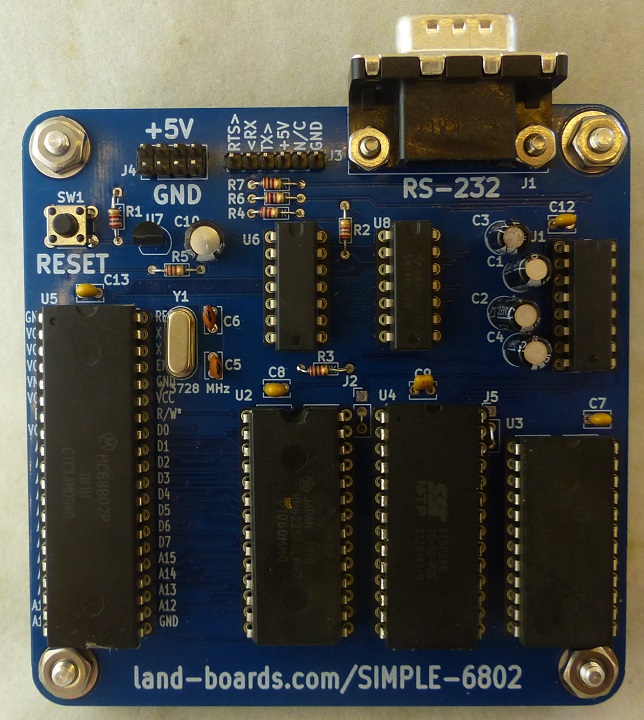

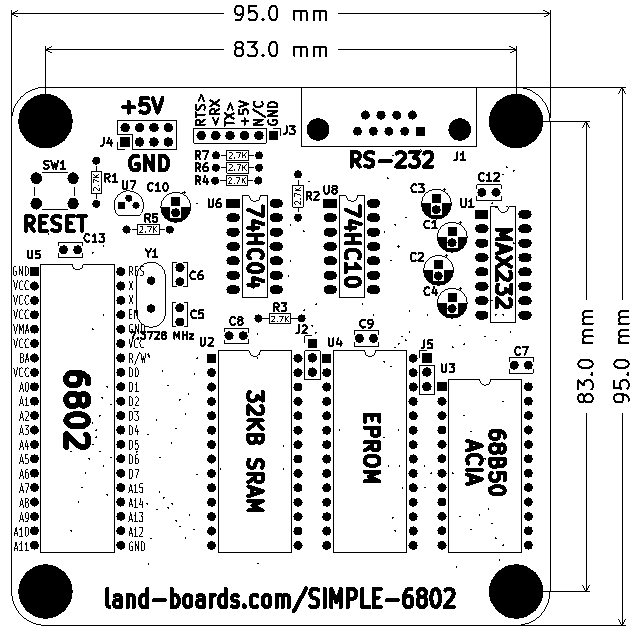

Features

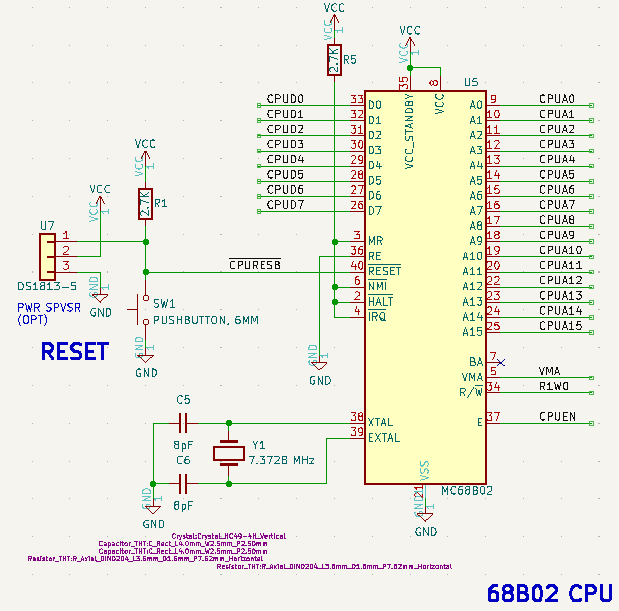

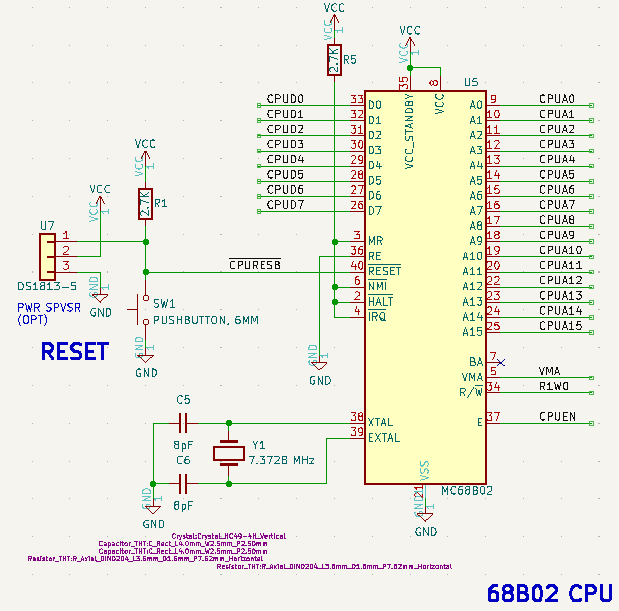

- 68B02 CPU

- 1.8432 MHz clock

- MC6802 is fully compatible with MC6800 but without messy two-phase clocking

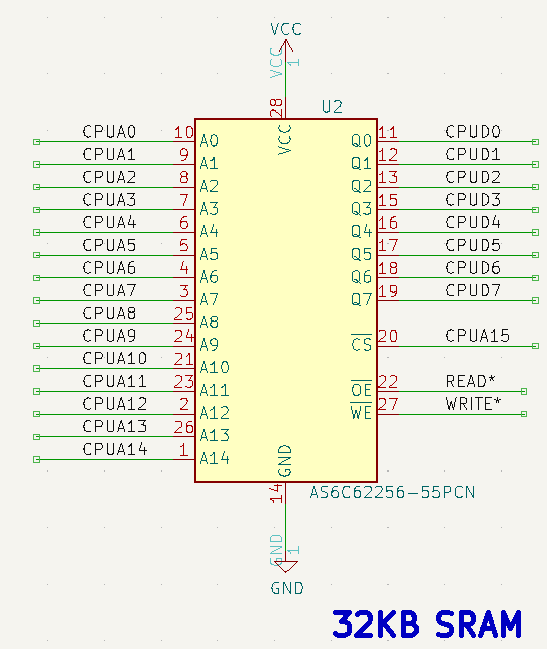

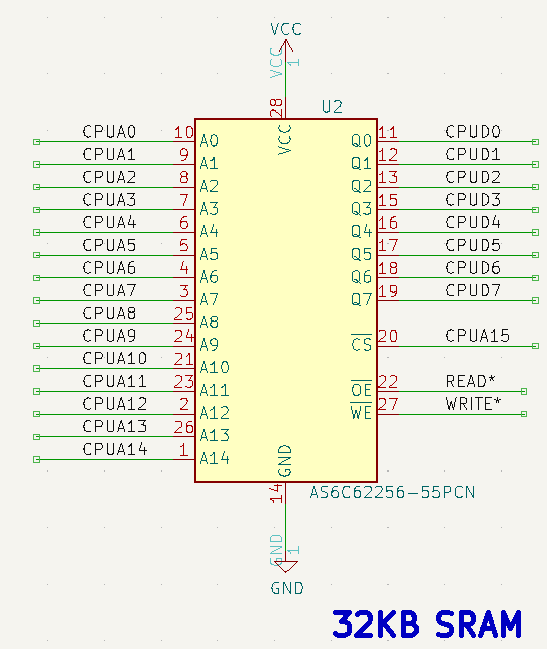

- 32KB SRAM

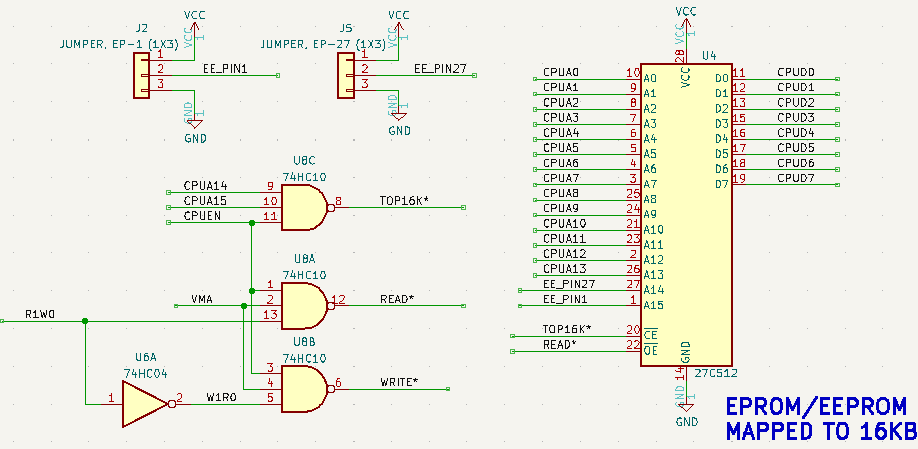

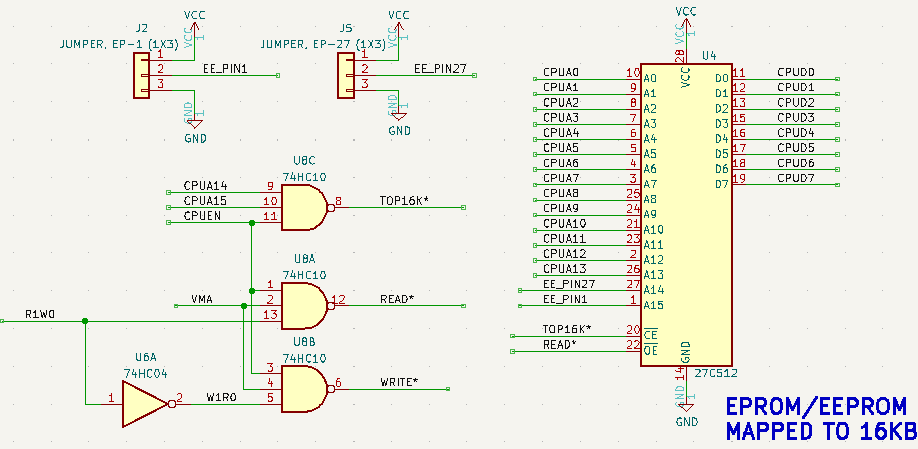

- 16KB EPROM/EEPROM

- 16KB reserved

- 8KB (28C64 parts can be used)

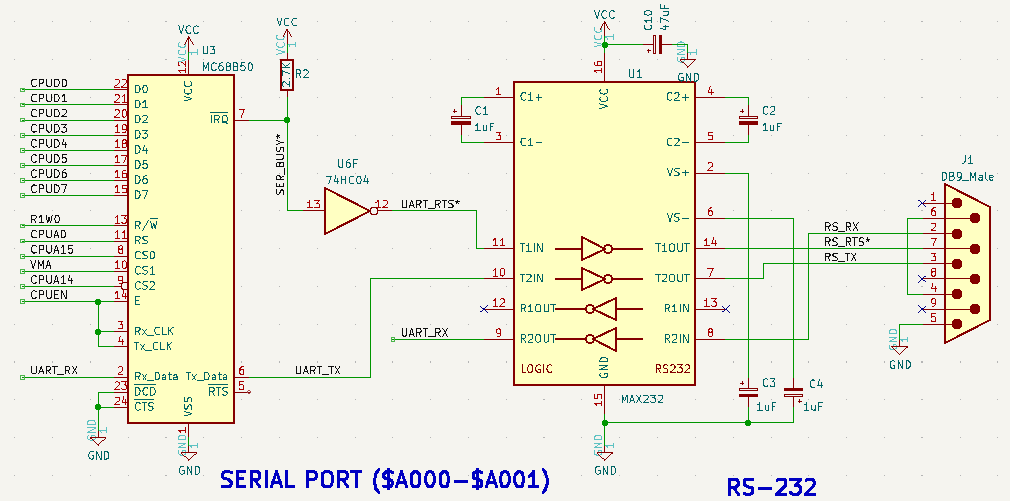

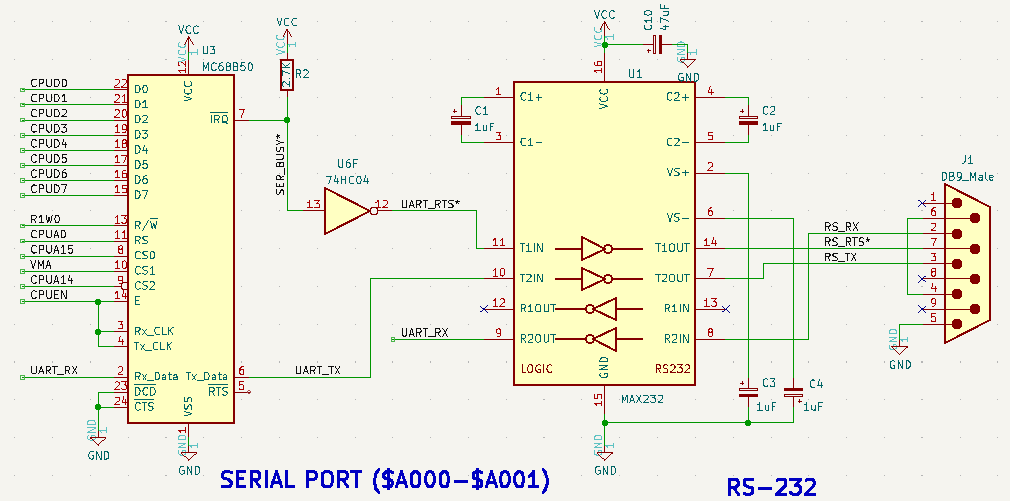

- 68B50 Serial Port (ACIA)

- RS-232 port

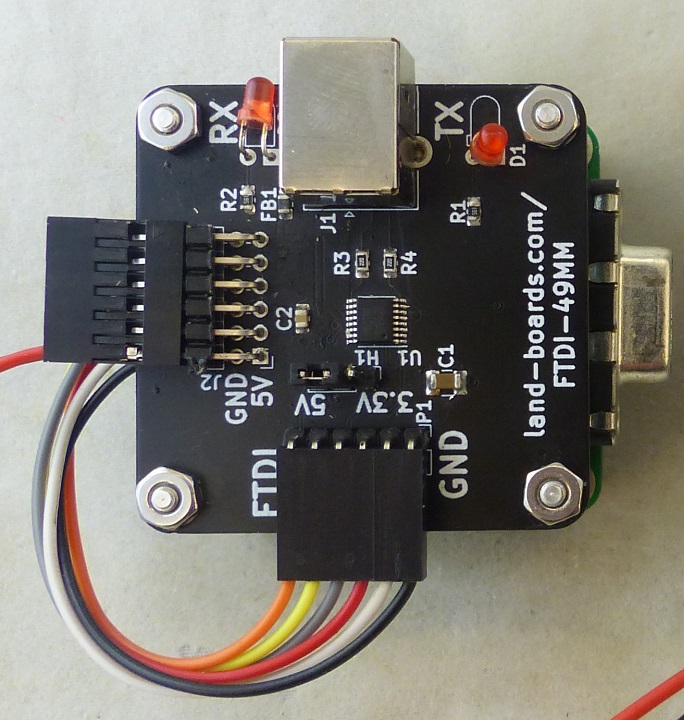

- Header for FTDI

- 115,200 baud

- Reset switch with optional Power Supervisor

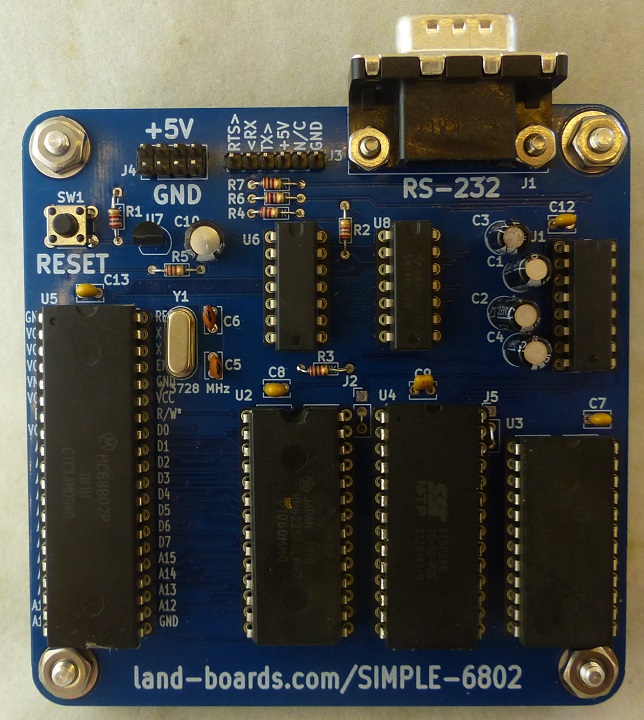

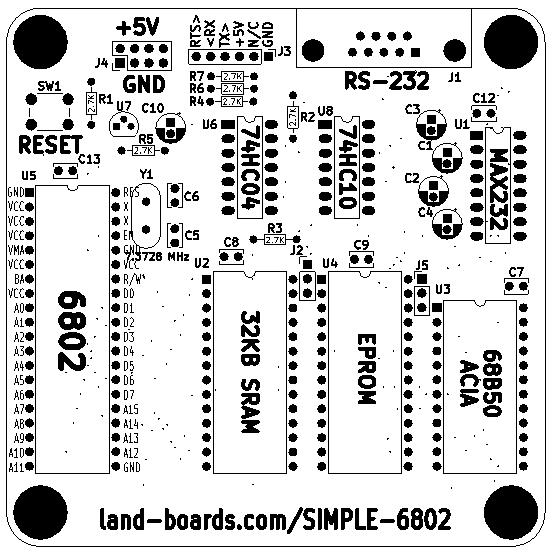

- 95x95mm card

- (4) 6-32 mounting holes

Memory Map

- 0x0000-0x7FFF 32KB SRAM

- 0x8000-0xBFFF Serial (68B50 ACIA)

- 0xC000-0xFFFF 16KB EPROM

Chipset

Design

J1 - RS-232 Serial

- N/C

- Receive

- Transmit

- Loop to pin 6

- GND

- Loop to pin 4

- RTS

- N/C

- N/C

J2 / J5 - EPROM/EEPROM Select Jumpers

- J2 - EPROM Pin 1 jumper

- 1-2 for 28C64, 28C256 (Pull WE to VCC)

- 2-3 for 27256, 27SF256, 27512 (Pull A14 to GND)

- J5 - EPROM Pin 27 jumper

EEPROM Pin Table

| 27512

|

27256

|

27SF256

|

28C256

|

27128

|

2764

|

28C64

|

PIN

|

|

PIN

|

2764

|

28C64

|

27128

|

28C256

|

27SF256

|

27256

|

27512

|

| A15

|

VPP

|

VPP

|

A14

|

VPP

|

VPP

|

N/C

|

1

|

|

28

|

VCC

|

VCC

|

VCC

|

VCC

|

VCC

|

VCC

|

VCC

|

| A12

|

A12

|

A12

|

A12

|

A12

|

A12

|

A12

|

2

|

|

27

|

PGM

|

WE*

|

PGM

|

WE*

|

A14

|

A14

|

A14

|

| A7

|

A7

|

A7

|

A7

|

A7

|

A7

|

A7

|

3

|

|

26

|

A13

|

N/C

|

A13

|

A13

|

A13

|

A13

|

A13

|

| A6

|

A6

|

A6

|

A6

|

A6

|

A6

|

A6

|

4

|

|

25

|

A8

|

A8

|

A8

|

A8

|

A8

|

A8

|

A8

|

| A5

|

A5

|

A5

|

A5

|

A5

|

A5

|

A5

|

5

|

|

24

|

A9

|

A9

|

A9

|

A9

|

A9

|

A9

|

A9

|

| A4

|

A4

|

A4

|

A4

|

A4

|

A4

|

A4

|

6

|

|

23

|

A11

|

A11

|

A11

|

A11

|

A11

|

A11

|

A11

|

| A3

|

A3

|

A3

|

A3

|

A3

|

A3

|

A3

|

7

|

|

22

|

OE*

|

OE*

|

OE*

|

OE*

|

OE*

|

OE*

|

OE*

|

| A2

|

A2

|

A2

|

A2

|

A2

|

A2

|

A2

|

8

|

|

21

|

A10

|

A10

|

A10

|

A10

|

A10

|

A10

|

A10

|

| A1

|

A1

|

A1

|

A1

|

A1

|

A1

|

A1

|

9

|

|

20

|

CE*

|

CE*

|

CE*

|

CE*

|

CE*

|

CE*

|

CE*

|

| A0

|

A0

|

A0

|

A0

|

A0

|

A0

|

A0

|

10

|

|

19

|

D7

|

D7

|

D7

|

D7

|

D7

|

D7

|

D7

|

| D0

|

D0

|

D0

|

D0

|

D0

|

D0

|

D0

|

11

|

|

18

|

D6

|

D6

|

D6

|

D6

|

D6

|

D6

|

D6

|

| D1

|

D1

|

D1

|

D1

|

D1

|

D1

|

D1

|

12

|

|

17

|

D5

|

D5

|

D5

|

D5

|

D5

|

D5

|

D5

|

| D2

|

D2

|

D2

|

D2

|

D2

|

D2

|

D2

|

13

|

|

16

|

D4

|

D4

|

D4

|

D4

|

D4

|

D4

|

D4

|

| GND

|

GND

|

GND

|

GND

|

GND

|

GND

|

GND

|

14

|

|

15

|

D3

|

D3

|

D3

|

D3

|

D3

|

D3

|

D3

|

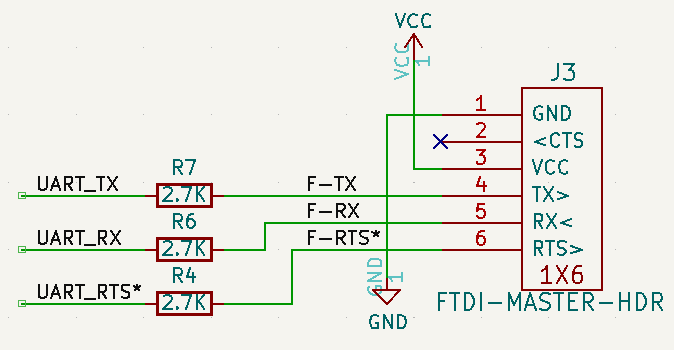

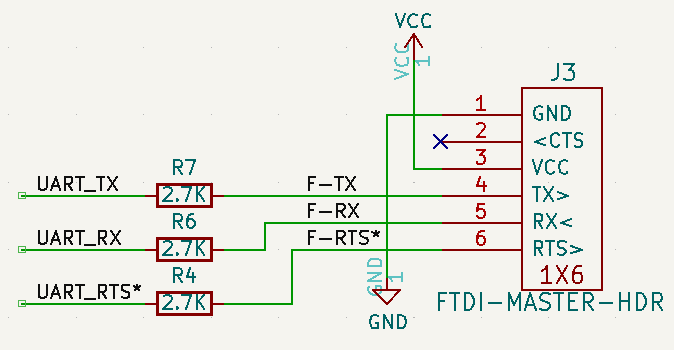

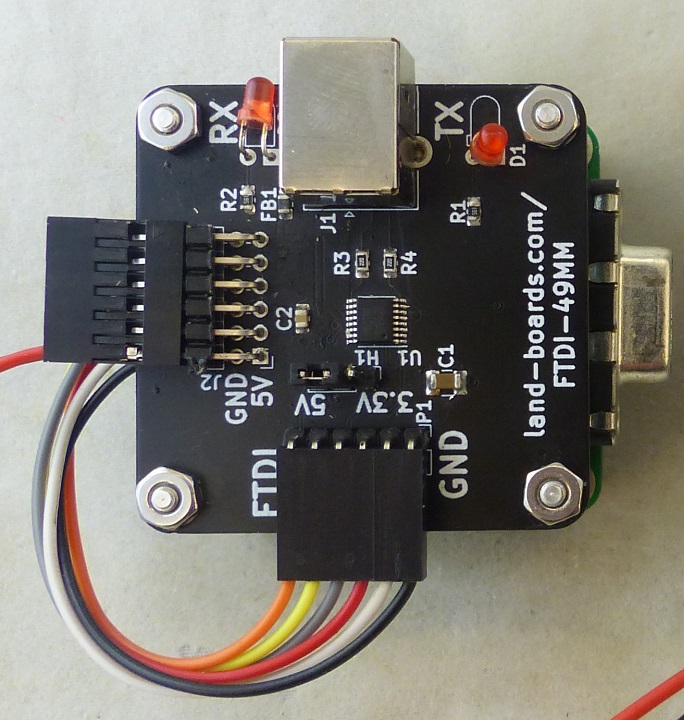

J3 - FTDI / TTL Serial

- Requires a FTDI cross-over cable

- GND

- RTS* (out)

- +5V

- Receive (in)

- Transmit (out)

- N/C

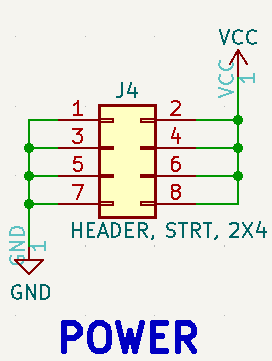

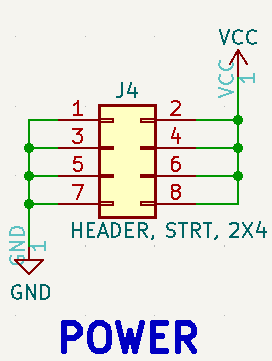

J4 - 5V Power

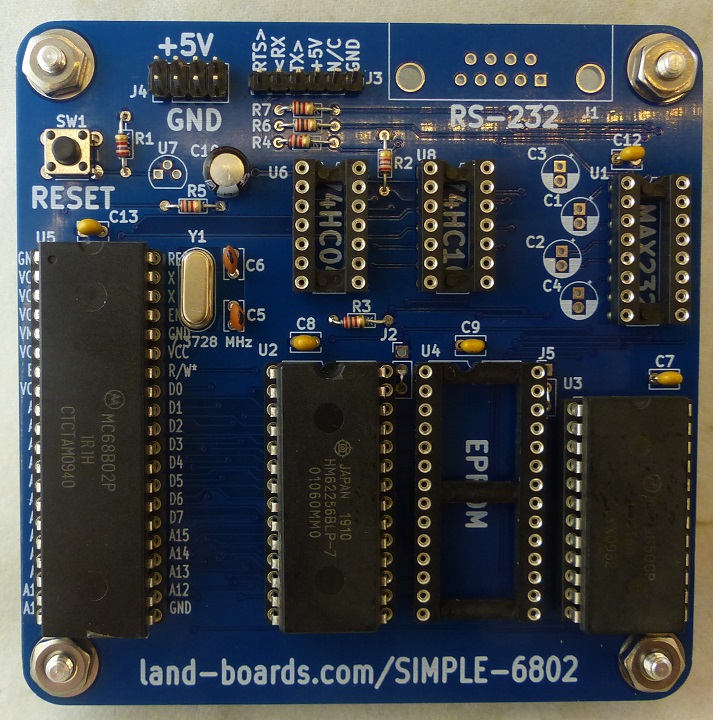

First Unit Checkout

Install Sockets

Install Passives

Power

- Install 2x4 at J4

- Power card via J4 with 5V

- Check power pins on parts

Reset

- Install U7 Power Monitor

- Install pushbutton switch SW1

- Reset button gets stretched by Power Monitor U9

- Measure reset at 68B02 U5 pin 40

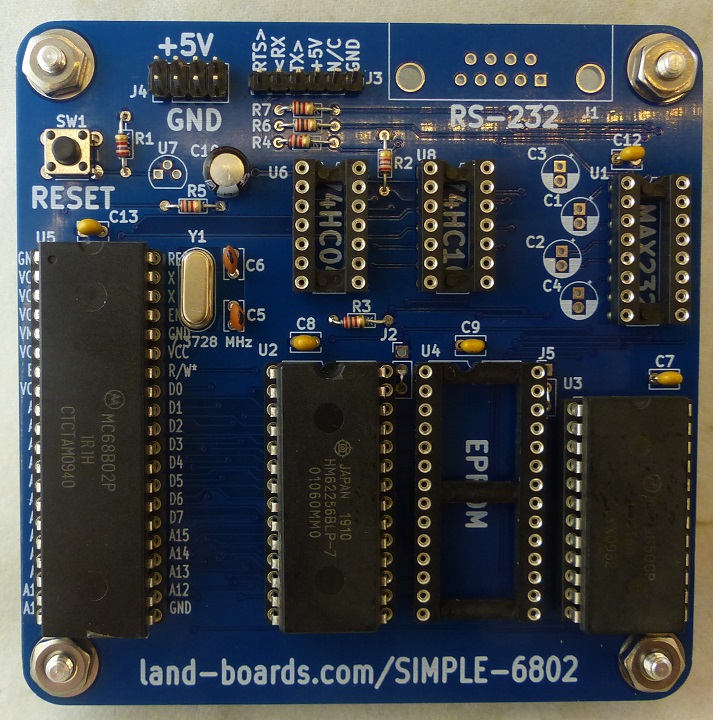

EPROM

- SST27C256 EEPROM

- 32 KB part

- Using first 16KB of EEPROM

- J2 EEPROM pin 1 = VPP = VCC or GND

- J5 EEPROM pin 27 = A14 = GND

- U1 - Do not install MAX232 yet

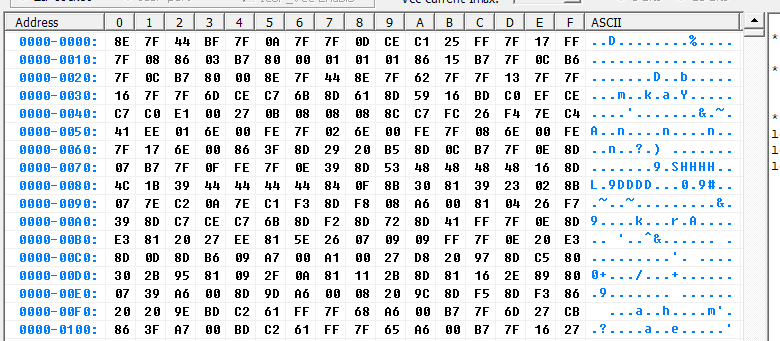

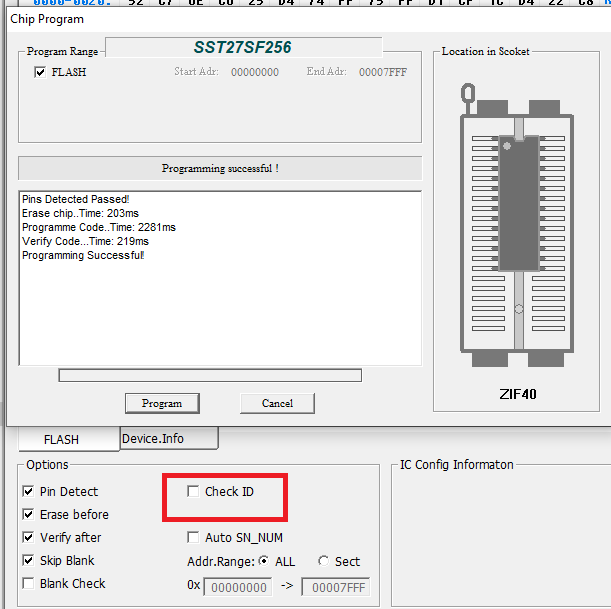

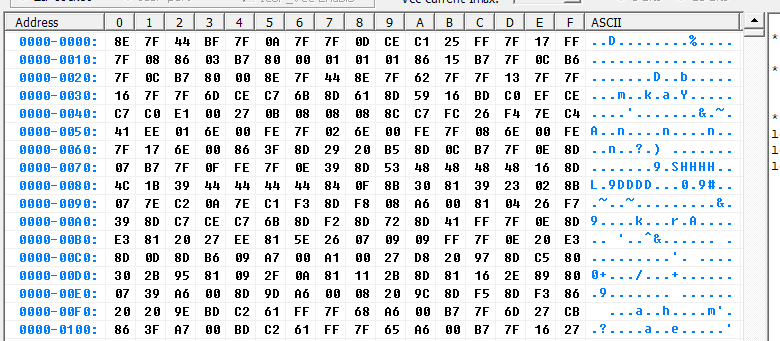

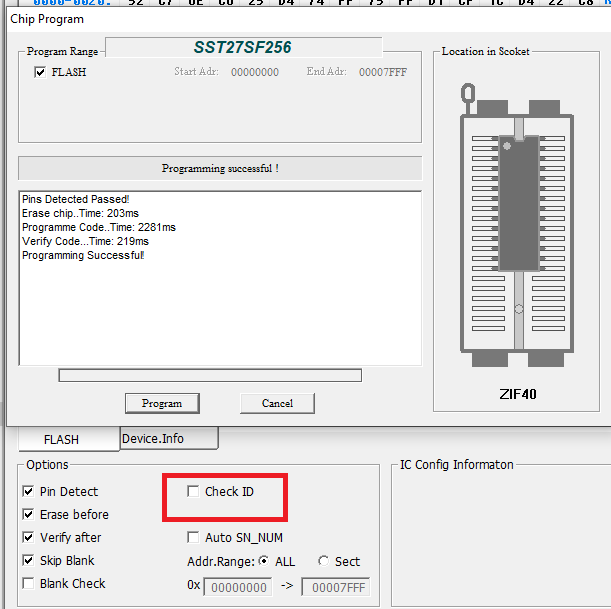

EEPROM Programming

- Memory Buffer should look like

- Got Device ID error

- Turn off ID check

- Device programmed/verified

Test FTDI Serial

>J TO ADDR D000

Forth-68

1 2 + . 3 OK

OK

Test RS-232 Serial

- With MAX232

- Install DB-9 Male

- Holes don't line up well, but 4-40 screws can fit

- Connected to FTDI-49MM and DCE cards

Software

- SMITHBUG is a debugger similar to MIKBUG

- Examine/Edit memory

- Disassembly code

- Download S record (V2)

- Run code

- FIG-Forth - Forth language

- Combined SMITHBUG and FIG-Forth build

SmithBUG Builds for SIMPLE-MC6802 CPU Card

Building Code

- Uses a68 assembler

- Command line makes S-Record output

- Use srec_cat to shift from EPROM absolute addresses to 0x0000 as HEX file

4KB Build

A68 SMITHBUG_SIMPLE-6802_F000.ASM -l SMITHBUG_SIMPLE-6802_F000.LST -s SMITHBUG_SIMPLE-6802_F000.S

srec_cat SMITHBUG_SIMPLE-6802_F000.s -offset - -minimum-addr SMITHBUG_SIMPLE-6802_F000.s -o smithbug_F000.hex -Intel

8KB Build

A68 SMITHBUG_SIMPLE-6802_E000.ASM -l SMITHBUG_SIMPLE-6802_E000.LST -s SMITHBUG_SIMPLE-6802_E000.S

srec_cat SMITHBUG_SIMPLE-6802_E000.s -offset - -minimum-addr SMITHBUG_SIMPLE-6802_E000.s -o smithbug_E000.hex -Intel

16KB Build

A68 SMITHBUG_SIMPLE-6802_C000.ASM -l SMITHBUG_SIMPLE-6802_C000.LST -s SMITHBUG_SIMPLE-6802_C000.S

srec_cat SMITHBUG_SIMPLE-6802_C000.s -offset - -minimum-addr SMITHBUG_SIMPLE-6802_C000.s -o smithbug_C000.hex -Intel

SmithBUG Commands

; V VIEW MEMORY

; E CHANGE MEMORY

; I FILL MEMORY

; M MOVE MEMORY

; D DISASSEMBLE CODE

; G GO TO PROGRAM

; R PRINT

; @ ASCII CONVERSION

; H PRINTER ON

; J JUMP TO TARGET PROGRAM

; F FIND

; Q HARDWARE LOCATION

; T TRACE PROGRAM

; 1 BREAKPOINT ONE

; 2 BREAKPOINT TWO

; K CONTINUE AFTER BREAK

; & S1 LOAD PROGRAM

; * HARDWARE LOCATION (TBA)

; O ECHO ON

; N ECHO OFF

FIGFORTH in RAM

&

- Using TermTerm, File, Send File

- Send fig-FORTH_6800.s19

- Type S9 to exit srecord loader

- Type J 1000 to jump to address 0x1000

- Responds with

Forth-68

1 1 + . 2 OK

TASK FORTH NOOP VLIST TRIAD INDEX LIST ? . D. D.R .R #S # SIGN #> <#

SPACES WHILE ELSE IF REPEAT AGAIN END UNTIL +LOOP LOOP DO THEN ENDIF BEGIN

BACK FORGET ' R/W HI LO BLOCK_READ BLOCK_WRITE ?DISC --> LOAD MESSAGE .LINE

(LINE) BLOCK BUFFER DR1 DR0 EMPTY-BUFFERS UPDATE +BUF PREV USE DABS ABS M/MOD

*/ */MOD MOD / /MOD * S->D COLD ABORT QUIT ( DEFINITIONS VOCABULARY IMMEDIATE

INTERPRET DLITERAL LITERAL [COMPILE] CREATE ID. ERROR (ABORT) -FIND NUMBER (NUMBER)

WORD PAD HOLD BLANKS ERASE FILL QUERY EXPECT ?STACK ." (.") -TRAILING TYPE

COUNT DOES> <BUILDS ;CODE (:CODE) DECIMAL HEX SMUDGE ] [ COMPILE ?LOADING ?CSP

?PAIRS ?EXEC ?COMP ?ERROR !CSP PFA NFA CFA LFA LATEST TRAVERSE -DUP MAX MIN

SPACE ROT > < = - C, , ALLOT HERE 2+ 1+ COLUMNS HLD R# CSP FLD DPL

BASE STATE CURRENT CONTEXT OFFSET SCR OUT IN BLK VOC-LINK DP FENCE WARNING

WIDTH TIB R0 S0 +ORIGIN B/SCR B/BUF LIMIT FIRST BL 3 2 1 0 USER VARIABLE

CONSTANT ; : C! ! C@ @ TOGGLE +! DUP SWAP DROP OVER DMINUS MINUS D+ +

0< 0= R R> >R LEAVE ;S RP! SP! SP@ XOR OR AND U/ U* CMOVE CR ?TERMINAL

KEY EMIT ENCLOSE (FIND) DIGIT I (DO) (+LOOP) (LOOP) 0BRANCH BRANCH EXECUTE LIT OK

SMITHBUG and FIGFORTH in ROM

- Combines SMITHBUG and FIGFORTH in ROM

- SMITHBUG in ROM from 0xC000-0xCFFF

- FIGFORTH in ROM from 0xD000-0xEFFF

- Vectors are at top of ROM from 0xFFF8-0xFFFF

- Fixes in FIG-Forth to get it to run from ROM

- The comments in the file indicated it could be run from ROM but the stack pointed to ORIG which is in ROM

- Fixed addresses of stack and I/O pointer to get it to work from ROM

- SMITHBUG and FIGFORTH in ROM GitHub

- Assemble

A68 SMITHBUG_FORTH_SIMPLE-6802_C000.ASM -l SMITHBUG_FORTH_SIMPLE-6802_C000.LST -s SMITHBUG_FORTH_SIMPLE-6802_C000.S

6800/6801 Cross-Assembler (Portable) Ver 3.5!

Copyright (c) 1985 William C. Colley, III

fixes for LCC/Windows and improvement by HRJ Aug 26 2019

A68 source_file | -l list_file | | -o/-s object_file |

No Errors

- Edit out RAM at top

- Make hex file

srec_cat SMITHBUG_FORTH_SIMPLE-6802_C000.s -offset - -minimum-addr SMITHBUG_FORTH_SIMPLE-6802_C000.s -o SMITHBUG_FORTH_SIMPLE-FC.hex -Intel

srec_cat: SMITHBUG_FORTH_SIMPLE-6802_C000.s: 1: warning: no header record

srec_cat: SMITHBUG_FORTH_SIMPLE-6802_C000.s: 1: warning: no header record

- Boots to SMITHBUG

- Type J D000 to run Fig-Forth or

- Type 4 to run Forth

TinyBASIC

References

Mechanicals

Assembly Sheet

Rev 1