Difference between revisions of "FPGA-ITX-01"

Jump to navigation

Jump to search

Blwikiadmin (talk | contribs) |

Blwikiadmin (talk | contribs) |

||

| Line 24: | Line 24: | ||

* [http://www.openmusiclabs.com/learning/digital/pwm-dac.1.html#:~:text=PWM%20can%20be%20thought%20of%20as%20amplitude%20modulation,signals%20at%2030kHz%20%2B%2F-%205kHz%2C%2010kHz%2C%2015kHz%2C%20etc. Using PWM to generate sound] | * [http://www.openmusiclabs.com/learning/digital/pwm-dac.1.html#:~:text=PWM%20can%20be%20thought%20of%20as%20amplitude%20modulation,signals%20at%2030kHz%20%2B%2F-%205kHz%2C%2010kHz%2C%2015kHz%2C%20etc. Using PWM to generate sound] | ||

* [https://www.engineersgarage.com/how-to-generate-sound-using-pwm-with-pic-microcontroller-part-22-25/ How to Generate Sound using PWM] | * [https://www.engineersgarage.com/how-to-generate-sound-using-pwm-with-pic-microcontroller-part-22-25/ How to Generate Sound using PWM] | ||

| − | * Run at frequency well above audio, say 48 KHz | + | * Run at frequency well above audio, say 44.1 or 48 KHz |

* Output of filter with 50% duty cycle will produce smoothed average voltage at the mid-point | * Output of filter with 50% duty cycle will produce smoothed average voltage at the mid-point | ||

* Values > 50% duty cycle will produce a voltage higher than the average | * Values > 50% duty cycle will produce a voltage higher than the average | ||

Revision as of 16:34, 28 August 2022

Contents

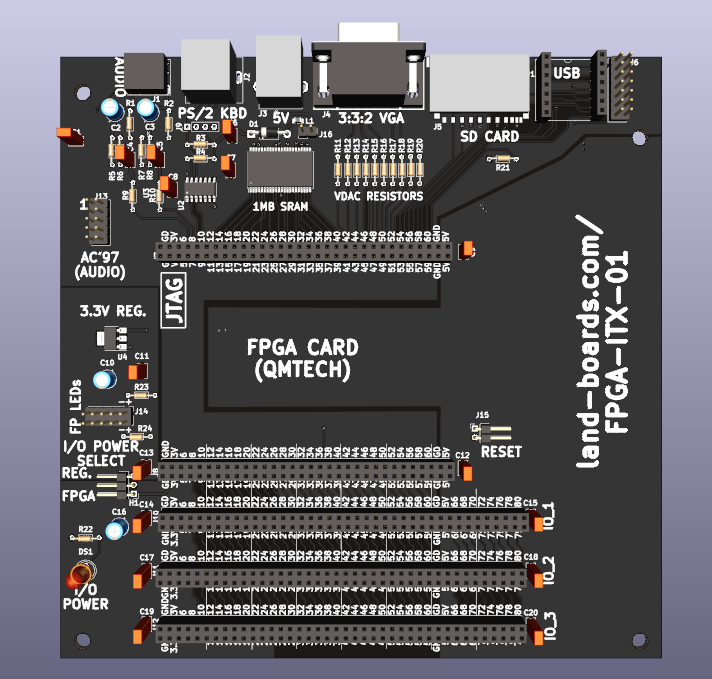

- 1 Features

- 1.1 Stereo Audio Jack (J1, J13)

- 1.2 5V PS/2 keyboard connector (J4, J9)

- 1.3 5V USB B (power only) (J3)

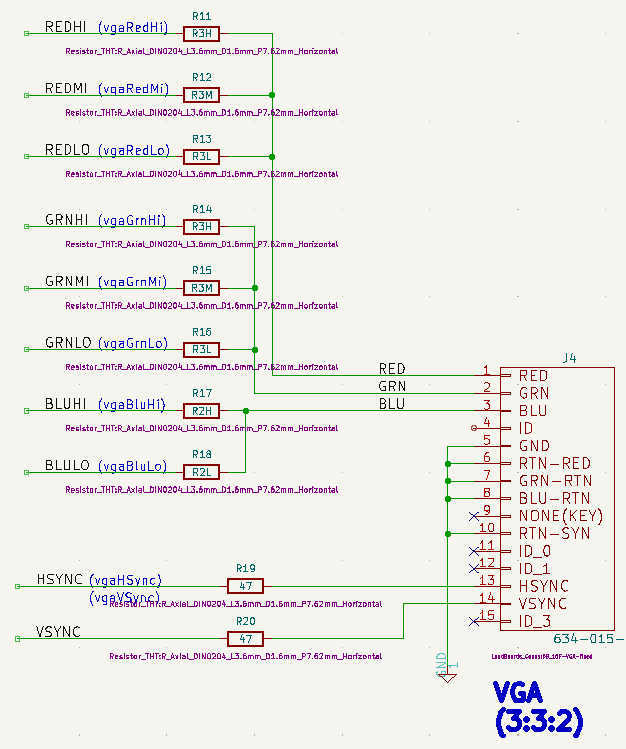

- 1.4 3:3:2 VGA (256 colors (J4)

- 1.5 SD Card socket (J5)

- 1.6 FPGA Adapter Card (J7, J8)

- 1.7 3 I/O slots IO_1-IO_3 (J10-J12)

- 1.8 XIAO RP2040 (U1, J6)

- 1.9 I/O Slots Power Select Jumper (H1)

- 1.10 1 MB SRAM

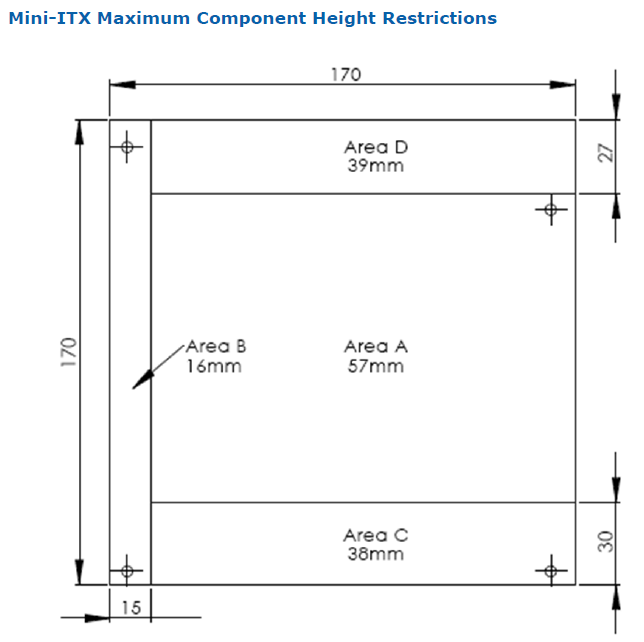

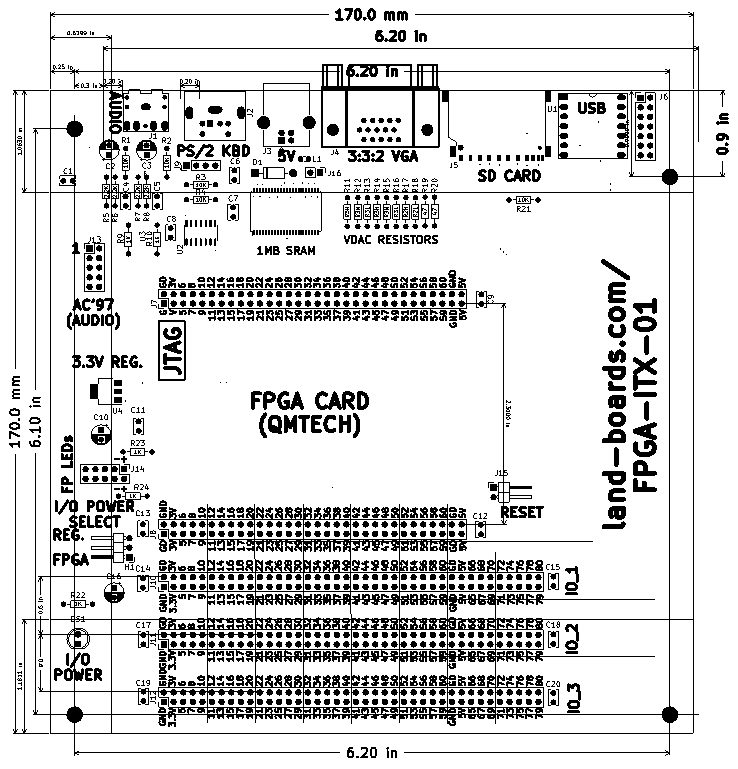

- 1.11 170x170mm, Mini-ITX card

- 1.12 Card Mechanicals

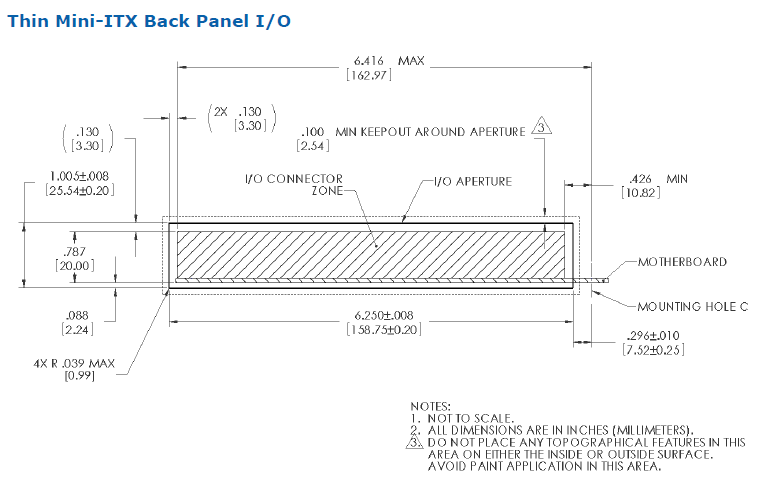

- 1.13 Back Panel

- 2 Expansion Cards

- 3 Mechanicals

- 4 Assembly Sheet

Features

- FPGA Adapter Card

- 170x170mm, Mini-ITX card

- 1 MB SRAM

- 5V PS/2 keyboard connector

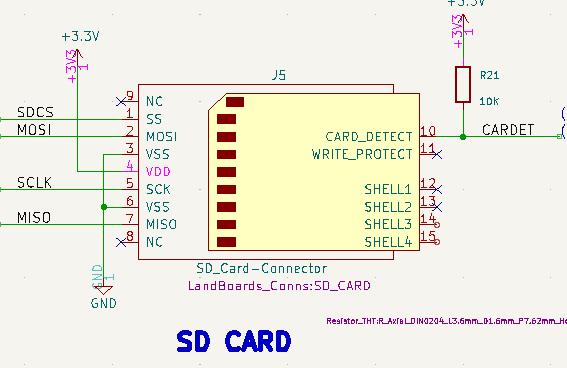

- SD Card socket

- 3:3:2 VGA (256 colors

- 5V USB B (power only)

- XIAO RP2040

- Stereo Audio Jack

- 3 I/O slots

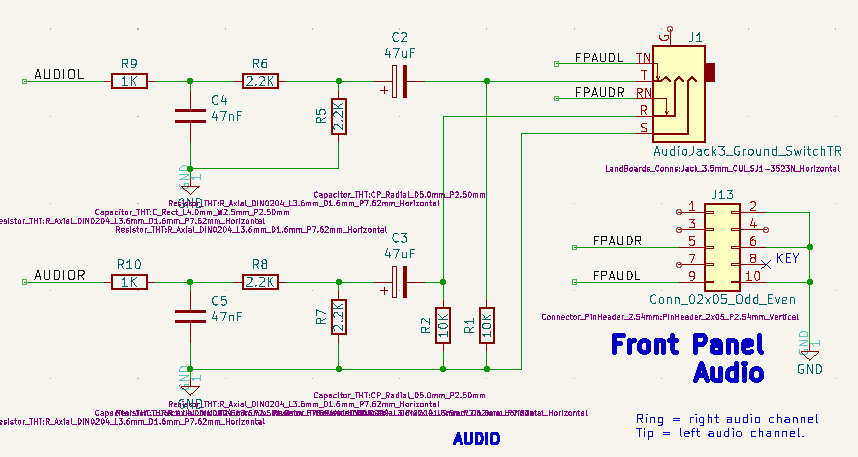

Stereo Audio Jack (J1, J13)

- 3.5mm stereo socket

- Jack on card has priority over connection to chassis jack

- Front panel gets disconnected when jack is plugged into the card

- J13 is header to case jack

- Minimal LP filter

- FPGA Sound on our GitHub

- Using PWM to generate sound

- How to Generate Sound using PWM

- Run at frequency well above audio, say 44.1 or 48 KHz

- Output of filter with 50% duty cycle will produce smoothed average voltage at the mid-point

- Values > 50% duty cycle will produce a voltage higher than the average

- Values < 50% duty cycle will produce a voltage lower than the average

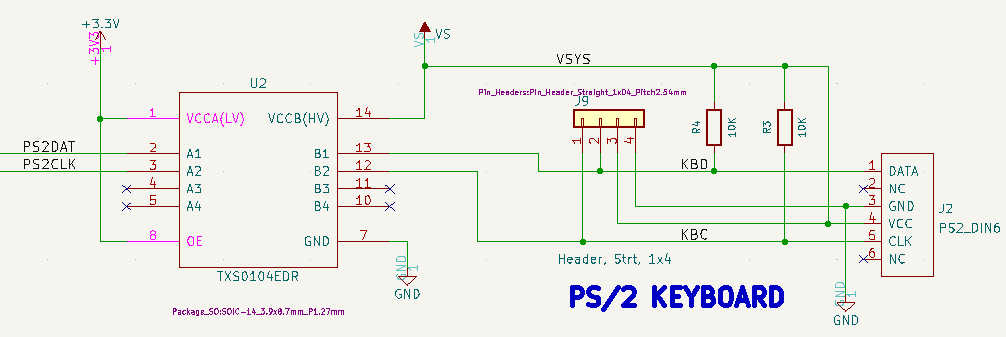

5V PS/2 keyboard connector (J4, J9)

- PS/2 connector

- 5V to 3.3V level shifter

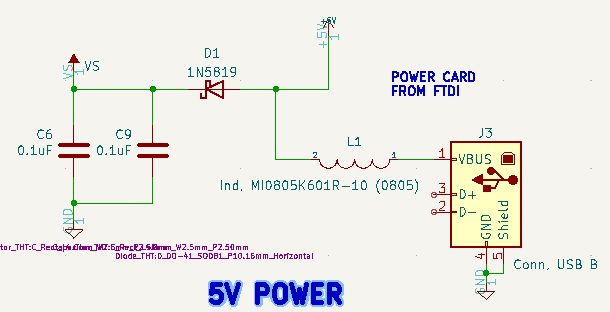

5V USB B (power only) (J3)

3:3:2 VGA (256 colors (J4)

- VGA connector

- 8-bit video (3:3:2)

SD Card socket (J5)

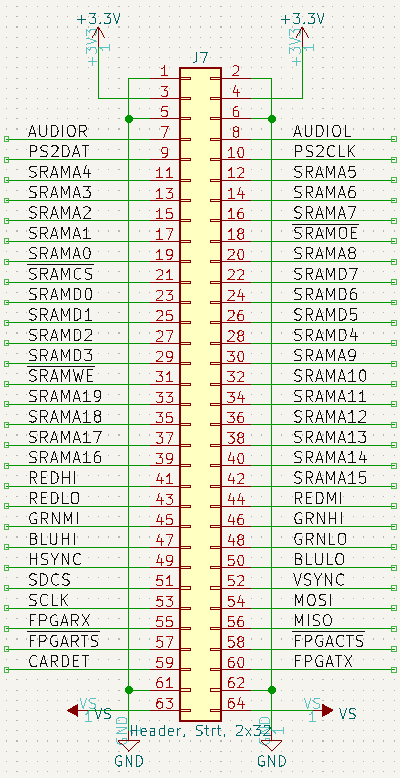

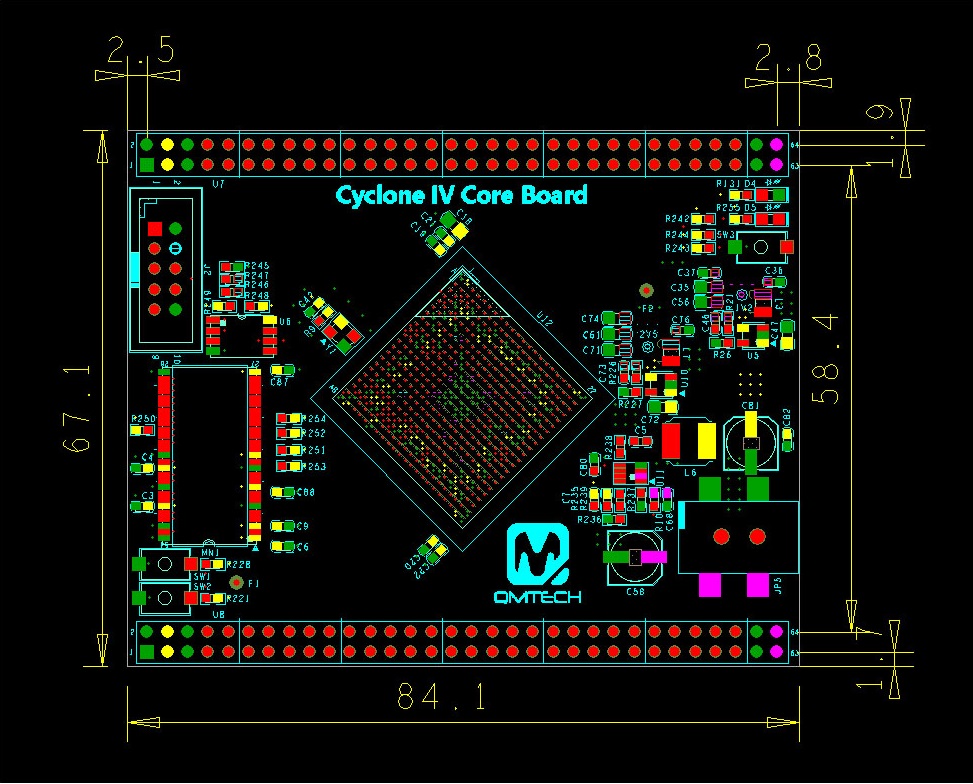

FPGA Adapter Card (J7, J8)

- QMTECH FPGA cards

- EP4CE15 Cyclone IV FPGA Card (tested)

- EP4CE55 Cyclone IV FPGA Card (untested)

- Cyclone V FPGA Card] (tested)

- Cyclone V FPGA Card (untested)

- QMTECH Cyclone 10CL006 FPGA Card (tested)

CPU I/O pins (J7)

- Connects to SRAM, PS/2, VGA, SD card

J7 Pins list

| U7 PIN | EP4CE15 | EP4CE55 | 5CEFA2 | CYC 10 | FUNCTION | U7 PIN | EP4CE15 | EP4CE55 | 5CEFA2 | CYC 10 | FUNCTION | |

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 1 | GND | GND | GND | GND | GND | 2 | GND | GND | GND | GND | GND | |

| 3 | 3.3V | 3.3V | 3.3V | 3.3V | 3.3V | 4 | 3.3V | 3.3V | 3.3V | 3.3V | 3.3V | |

| 5 | GND | GND | GND | GND | GND | 6 | GND | GND | GND | GND | GND | |

| 7 | PIN_R1 | PIN_R1 | PIN_AA2 | PIN_G1 | AUDIOR | 8 | PIN_R2 | PIN_R2 | PIN_AA1 | PIN_G2 | AUDIOL | |

| 9 | PIN_P1 | PIN_P1 | PIN_Y3 | PIN_D1 | PS2DAT | 10 | PIN_P2 | PIN_P2 | PIN_W2 | PIN_C2 | PS2CLK | |

| 11 | PIN_N1 | PIN_N1 | PIN_U1 | PIN_B1 | SRAMA4 | 12 | PIN_N2 | PIN_N2 | PIN_U2 | PIN_F5 | SRAMA5 | |

| 13 | PIN_M1 | PIN_M1 | PIN_N1 | PIN_D3 | SRAMA3 | 14 | PIN_M2 | PIN_M2 | PIN_N2 | PIN_C3 | SRAMA6 | |

| 15 | PIN_J1 | PIN_J1 | PIN_L1 | PIN_B3 | SRAMA2 | 16 | PIN_J2 | PIN_J2 | PIN_L2 | PIN_A3 | SRAMA7 | |

| 17 | PIN_H1 | PIN_H1 | PIN_G1 | PIN_B4 | SRAMA1 | 18 | PIN_H2 | PIN_H2 | PIN_G2 | PIN_A4 | SRAM0E_N | |

| 19 | PIN_F1 | PIN_F1 | PIN_E2 | PIN_E5 | SRAMA0 | 20 | PIN_F2 | PIN_F2 | PIN_D3 | PIN_A2 | SRAMA8 | |

| 21 | PIN_E1 | PIN_E1 | PIN_C1 | PIN_D4 | SRAMCS_N | 22 | PIN_D2 | PIN_D2 | PIN_C2 | PIN_E6 | SRAMD7 | |

| 23 | PIN_C1 | PIN_C1 | PIN_G6 | PIN_C6 | SRAMD0 | 24 | PIN_C2 | PIN_C2 | PIN_H6 | PIN_D6 | SRAMD6 | |

| 25 | PIN_B1 | PIN_B1 | PIN_G8 | PIN_B5 | SRAMD1 | 26 | PIN_B2 | PIN_B2 | PIN_H8 | PIN_A5 | SRAMD5 | |

| 27 | PIN_B3 | PIN_B3 | PIN_F7 | PIN_B6 | SRAMD2 | 28 | PIN_A3 | PIN_A3 | PIN_E7 | PIN_A6 | SRAMD4 | |

| 29 | PIN_B4 | PIN_B4 | PIN_D6 | PIN_B7 | SRAMD3 | 30 | PIN_A4 | PIN_A4 | PIN_C6 | PIN_A7 | SRAMA9 | |

| 31 | PIN_C4 | PIN_C4 | PIN_E9 | PIN_D8 | SRAMWE_N | 32 | PIN_C3 | PIN_C3 | PIN_D9 | PIN_C8 | SRAMA10 | |

| 33 | PIN_B5 | PIN_B5 | PIN_B5 | PIN_D9 | SRAMA19 | 34 | PIN_A5 | PIN_A5 | PIN_A5 | PIN_C9 | SRAMA11 | |

| 35 | PIN_B6 | PIN_B6 | PIN_B6 | PIN_B8 | SRAMA18 | 36 | PIN_A6 | PIN_A6 | PIN_B7 | PIN_A8 | SRAMA12 | |

| 37 | PIN_B7 | PIN_B7 | PIN_A7 | PIN_B9 | SRAMA17 | 38 | PIN_A7 | PIN_A7 | PIN_A8 | PIN_A9 | SRAMA13 | |

| 39 | PIN_B8 | PIN_B8 | PIN_A9 | PIN_E9 | SRAMA16 | 40 | PIN_A8 | PIN_A8 | PIN_A10 | PIN_E8 | SRAMA14 | |

| 41 | PIN_B9 | PIN_B9 | PIN_B10 | PIN_E11 | REDHI | 42 | PIN_A9 | PIN_A9 | PIN_C9 | PIN_E10 | SRAMA15 | |

| 43 | PIN_B10 | PIN_B10 | PIN_G10 | PIN_A10 | REDLO | 44 | PIN_A10 | PIN_A10 | PIN_F10 | PIN_B10 | REDMID | |

| 45 | PIN_B13 | PIN_B13 | PIN_C11 | PIN_D12 | GRNMID | 46 | PIN_A13 | PIN_A13 | PIN_B11 | PIN_D11 | GRNHI | |

| 47 | PIN_B14 | PIN_B14 | PIN_B12 | PIN_B11 | BLUHI | 48 | PIN_A14 | PIN_A14 | PIN_A12 | PIN_A11 | GRNLO | |

| 49 | PIN_B15 | PIN_B15 | PIN_E12 | PIN_B12 | HSYNC | 50 | PIN_A15 | PIN_A15 | PIN_D12 | PIN_A12 | BLULO | |

| 51 | PIN_B16 | PIN_B16 | PIN_D13 | PIN_B13 | SDCS_N | 52 | PIN_A16 | PIN_A16 | PIN_C13 | PIN_A13 | VSYNC | |

| 53 | PIN_B17 | PIN_B17 | PIN_B13 | PIN_B14 | SD_SCK | 54 | PIN_A17 | PIN_A17 | PIN_A13 | PIN_A14 | SD_MOSI | |

| 55 | PIN_B18 | PIN_B18 | PIN_A15 | PIN_D14 | USBTX/FPGARX | 56 | PIN_A18 | PIN_A18 | PIN_A14 | PIN_C14 | SD_MISO | |

| 57 | PIN_B19 | PIN_B19 | PIN_B15 | PIN_B16 | USBCTS/FPGARTS | 58 | PIN_A19 | PIN_A19 | PIN_C15 | PIN_A15 | UBSRTS/FPGACTS | |

| 59 | PIN_B20 | PIN_B20 | PIN_C16 | PIN_C16 | CD_DET | 60 | PIN_A20 | PIN_A20 | PIN_B16 | PIN_C15 | USBRX/FPGATX | |

| 61 | GND | GND | GND | GND | GND | 62 | GND | GND | GND | GND | GND | |

| 63 | 5V | 5V | 5V | 5V | 5V | 64 | 5V | 5V | 5V | 5V | 5V |

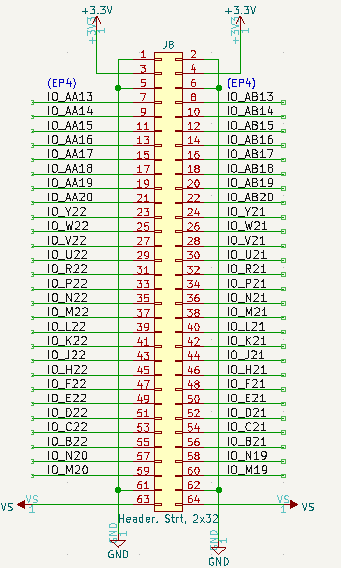

J8 - I/O pins (J8)

- All pins are usable and are daisy-chained to 3 expansion connectors

- Cyclone 10 notes

- Cannot place output or bidirectional pin J8IO[35] in input pin location M16

- Cannot place output or bidirectional pin J8IO[36] in input pin location M15

- Cannot place output or bidirectional pin J8IO[57] in input pin location E16

- Cannot place output or bidirectional pin J8IO[58] in input pin location E15

| U8 PIN | EP4CE15 | EP4CE55 | 5CEFA2 | 10C1006 | U8 PIN | EP4CE15 | EP4CE55 | 5CEFA2 | 10C1006 | |

|---|---|---|---|---|---|---|---|---|---|---|

| 1 | GND | GND | GND | GND | 2 | GND | GND | GND | GND | |

| 3 | 3.3V | 3.3V | 3.3V | 3.3V | 4 | 3.3V | 3.3V | 3.3V | 3.3V | |

| 5 | GND | GND | GND | GND | 6 | GND | GND | GND | GND | |

| 7 | PIN_AA13 | PIN_AA13 | PIN_AA14 | PIN_R9 | 8 | PIN_AB13 | PIN_AB13 | PIN_AA13 | PIN_T9 | |

| 9 | PIN_AA14 | PIN_AA14 | PIN_AA15 | PIN_R10 | 10 | PIN_AB14 | PIN_AB14 | PIN_AB15 | PIN_T10 | |

| 11 | PIN_AA15 | PIN_AA15 | PIN_Y15 | PIN_R11 | 12 | PIN_AB15 | PIN_AB15 | PIN_Y14 | PIN_T11 | |

| 13 | PIN_AA16 | PIN_AA16 | PIN_AB18 | PIN_R12 | 14 | PIN_AB16 | PIN_AB16 | PIN_AB17 | PIN_T12 | |

| 15 | PIN_AA17 | PIN_AA17 | PIN_Y17 | PIN_N9 | 16 | PIN_AB17 | PIN_AB17 | PIN_Y16 | PIN_M9 | |

| 17 | PIN_AA18 | PIN_AA18 | PIN_AA18 | PIN_M10 | 18 | PIN_AB18 | PIN_AB18 | PIN_AA17 | PIN_P9 | |

| 19 | PIN_AA19 | PIN_AA19 | PIN_AA20 | PIN_P11 | 20 | PIN_AB19 | PIN_AB19 | PIN_AA19 | PIN_N11 | |

| 21 | PIN_AA20 | PIN_AA20 | PIN_Y20 | PIN_R13 | 22 | PIN_AB20 | PIN_AB20 | PIN_Y19 | PIN_T13 | |

| 23 | PIN_Y22 | PIN_Y22 | PIN_AB21 | PIN_T15 | 24 | PIN_Y21 | PIN_Y21 | PIN_AB20 | PIN_T14 | |

| 25 | PIN_W22 | PIN_W22 | PIN_AA22 | PIN_N12 | 26 | PIN_W21 | PIN_W21 | PIN_AB22 | PIN_M11 | |

| 27 | PIN_V22 | PIN_V22 | PIN_W22 | PIN_R14 | 28 | PIN_V21 | PIN_V21 | PIN_Y22 | PIN_N13 | |

| 29 | PIN_U22 | PIN_U22 | PIN_Y21 | PIN_N14 | 30 | PIN_U21 | PIN_U21 | PIN_W21 | PIN_P14 | |

| 31 | PIN_R22 | PIN_R22 | PIN_U22 | PIN_P16 | 32 | PIN_R21 | PIN_R21 | PIN_V21 | PIN_R16 | |

| 33 | PIN_P22 | PIN_P22 | PIN_V20 | PIN_N16 | 34 | PIN_P21 | PIN_P21 | PIN_W19 | PIN_N15 | |

| 35 | PIN_N22 | PIN_N22 | PIN_U21 | PIN_M16 * | 36 | PIN_N21 | PIN_N21 | PIN_U20 | PIN_M15 * | |

| 37 | PIN_M22 | PIN_M22 | PIN_R22 | PIN_L16 | 38 | PIN_M21 | PIN_M21 | PIN_T22 | PIN_L15 | |

| 39 | PIN_L22 | PIN_L22 | PIN_P22 | PIN_P15 | 40 | PIN_L21 | PIN_L21 | PIN_R21 | PIN_M12 | |

| 41 | PIN_K22 | PIN_K22 | PIN_T20 | PIN_L14 | 42 | PIN_K21 | PIN_K21 | PIN_T19 | PIN_L13 | |

| 43 | PIN_J22 | PIN_J22 | PIN_P16 | PIN_K16 | 44 | PIN_J21 | PIN_J21 | PIN_P17 | PIN_K15 | |

| 45 | PIN_H22 | PIN_H22 | PIN_N20 | PIN_K12 | 46 | PIN_H21 | PIN_H21 | PIN_N21 | PIN_J12 | |

| 47 | PIN_F22 | PIN_F22 | PIN_M21 | PIN_J14 | 48 | PIN_F21 | PIN_F21 | PIN_M20 | PIN_J13 | |

| 49 | PIN_E22 | PIN_E22 | PIN_M18 | PIN_K11 | 50 | PIN_E21 | PIN_E21 | PIN_N19 | PIN_J11 | |

| 51 | PIN_D22 | PIN_D22 | PIN_L18 | PIN_G11 | 52 | PIN_D21 | PIN_D21 | PIN_L19 | PIN_F11 | |

| 53 | PIN_C22 | PIN_C22 | PIN_M22 | PIN_F13 | 54 | PIN_C21 | PIN_C21 | PIN_L22 | PIN_F14 | |

| 55 | PIN_B22 | PIN_B22 | PIN_L17 | PIN_F10 | 56 | PIN_B21 | PIN_B21 | PIN_K17 | PIN_F9 | |

| 57 | PIN_N20 | PIN_N20 | PIN_K22 | PIN_E16 * | 58 | PIN_N19 | PIN_N19 | PIN_K21 | PIN_E15 * | |

| 59 | PIN_M20 | PIN_M20 | PIN_M16 | PIN_D16 | 60 | PIN_M19 | PIN_M19 | PIN_N16 | PIN_D15 | |

| 61 | GND | GND | GND | GND | 62 | GND | GND | GND | GND | |

| 63 | 5V | 5V | 5V | 5V | 64 | 5V | 5V | 5V | 5V |

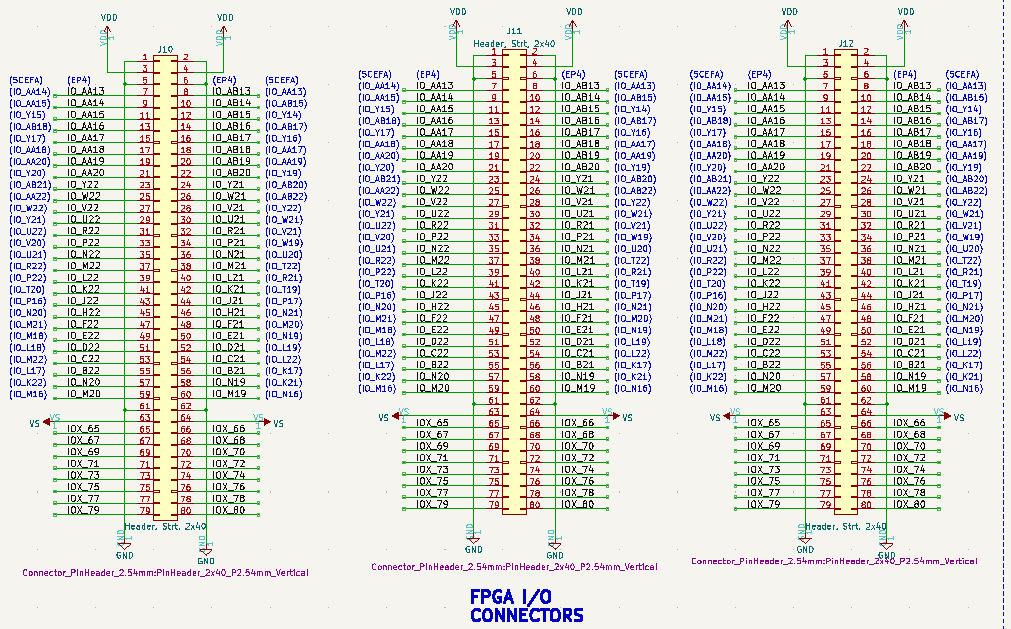

3 I/O slots IO_1-IO_3 (J10-J12)

- 3 I/O connectors

- 2x40 headers

- First 64-pins match pinout of J8

- Last 16 pins are chained together and do not connect to the FPGA (IOX65-80)

- Cyclone 10 notes

- Cannot place output or bidirectional pin J8IO[35] in input pin location M16

- Cannot place output or bidirectional pin J8IO[36] in input pin location M15

- Cannot place output or bidirectional pin J8IO[57] in input pin location E16

- Cannot place output or bidirectional pin J8IO[58] in input pin location E15

| U8 PIN | EP4CE15 | EP4CE55 | 5CEFA2 | 10C1006 | U8 PIN | EP4CE15 | EP4CE55 | 5CEFA2 | 10C1006 | |

|---|---|---|---|---|---|---|---|---|---|---|

| 1 | GND | GND | GND | GND | 2 | GND | GND | GND | GND | |

| 3 | 3.3V | 3.3V | 3.3V | 3.3V | 4 | 3.3V | 3.3V | 3.3V | 3.3V | |

| 5 | GND | GND | GND | GND | 6 | GND | GND | GND | GND | |

| 7 | PIN_AA13 | PIN_AA13 | PIN_AA14 | PIN_R9 | 8 | PIN_AB13 | PIN_AB13 | PIN_AA13 | PIN_T9 | |

| 9 | PIN_AA14 | PIN_AA14 | PIN_AA15 | PIN_R10 | 10 | PIN_AB14 | PIN_AB14 | PIN_AB15 | PIN_T10 | |

| 11 | PIN_AA15 | PIN_AA15 | PIN_Y15 | PIN_R11 | 12 | PIN_AB15 | PIN_AB15 | PIN_Y14 | PIN_T11 | |

| 13 | PIN_AA16 | PIN_AA16 | PIN_AB18 | PIN_R12 | 14 | PIN_AB16 | PIN_AB16 | PIN_AB17 | PIN_T12 | |

| 15 | PIN_AA17 | PIN_AA17 | PIN_Y17 | PIN_N9 | 16 | PIN_AB17 | PIN_AB17 | PIN_Y16 | PIN_M9 | |

| 17 | PIN_AA18 | PIN_AA18 | PIN_AA18 | PIN_M10 | 18 | PIN_AB18 | PIN_AB18 | PIN_AA17 | PIN_P9 | |

| 19 | PIN_AA19 | PIN_AA19 | PIN_AA20 | PIN_P11 | 20 | PIN_AB19 | PIN_AB19 | PIN_AA19 | PIN_N11 | |

| 21 | PIN_AA20 | PIN_AA20 | PIN_Y20 | PIN_R13 | 22 | PIN_AB20 | PIN_AB20 | PIN_Y19 | PIN_T13 | |

| 23 | PIN_Y22 | PIN_Y22 | PIN_AB21 | PIN_T15 | 24 | PIN_Y21 | PIN_Y21 | PIN_AB20 | PIN_T14 | |

| 25 | PIN_W22 | PIN_W22 | PIN_AA22 | PIN_N12 | 26 | PIN_W21 | PIN_W21 | PIN_AB22 | PIN_M11 | |

| 27 | PIN_V22 | PIN_V22 | PIN_W22 | PIN_R14 | 28 | PIN_V21 | PIN_V21 | PIN_Y22 | PIN_N13 | |

| 29 | PIN_U22 | PIN_U22 | PIN_Y21 | PIN_N14 | 30 | PIN_U21 | PIN_U21 | PIN_W21 | PIN_P14 | |

| 31 | PIN_R22 | PIN_R22 | PIN_U22 | PIN_P16 | 32 | PIN_R21 | PIN_R21 | PIN_V21 | PIN_R16 | |

| 33 | PIN_P22 | PIN_P22 | PIN_V20 | PIN_N16 | 34 | PIN_P21 | PIN_P21 | PIN_W19 | PIN_N15 | |

| 35 | PIN_N22 | PIN_N22 | PIN_U21 | PIN_M16 | 36 | PIN_N21 | PIN_N21 | PIN_U20 | PIN_M15 | |

| 37 | PIN_M22 | PIN_M22 | PIN_R22 | PIN_L16 | 38 | PIN_M21 | PIN_M21 | PIN_T22 | PIN_L15 | |

| 39 | PIN_L22 | PIN_L22 | PIN_P22 | PIN_P15 | 40 | PIN_L21 | PIN_L21 | PIN_R21 | PIN_M12 | |

| 41 | PIN_K22 | PIN_K22 | PIN_T20 | PIN_L14 | 42 | PIN_K21 | PIN_K21 | PIN_T19 | PIN_L13 | |

| 43 | PIN_J22 | PIN_J22 | PIN_P16 | PIN_K16 | 44 | PIN_J21 | PIN_J21 | PIN_P17 | PIN_K15 | |

| 45 | PIN_H22 | PIN_H22 | PIN_N20 | PIN_K12 | 46 | PIN_H21 | PIN_H21 | PIN_N21 | PIN_J12 | |

| 47 | PIN_F22 | PIN_F22 | PIN_M21 | PIN_J14 | 48 | PIN_F21 | PIN_F21 | PIN_M20 | PIN_J13 | |

| 49 | PIN_E22 | PIN_E22 | PIN_M18 | PIN_K11 | 50 | PIN_E21 | PIN_E21 | PIN_N19 | PIN_J11 | |

| 51 | PIN_D22 | PIN_D22 | PIN_L18 | PIN_G11 | 52 | PIN_D21 | PIN_D21 | PIN_L19 | PIN_F11 | |

| 53 | PIN_C22 | PIN_C22 | PIN_M22 | PIN_F13 | 54 | PIN_C21 | PIN_C21 | PIN_L22 | PIN_F14 | |

| 55 | PIN_B22 | PIN_B22 | PIN_L17 | PIN_F10 | 56 | PIN_B21 | PIN_B21 | PIN_K17 | PIN_F9 | |

| 57 | PIN_N20 | PIN_N20 | PIN_K22 | PIN_E16 | 58 | PIN_N19 | PIN_N19 | PIN_K21 | PIN_E15 | |

| 59 | PIN_M20 | PIN_M20 | PIN_M16 | PIN_D16 | 60 | PIN_M19 | PIN_M19 | PIN_N16 | PIN_D15 | |

| 61 | GND | GND | GND | GND | 62 | GND | GND | GND | GND | |

| 63 | 5V | 5V | 5V | 5V | 64 | 5V | 5V | 5V | 5V | |

| 65 | IOX_65 | IOX_65 | IOX_65 | IOX_65 | 66 | IOX_66 | IOX_66 | IOX_66 | IOX_66 | |

| 67 | IOX_67 | IOX_67 | IOX_67 | IOX_67 | 68 | IOX_68 | IOX_68 | IOX_68 | IOX_68 | |

| 69 | IOX_69 | IOX_69 | IOX_69 | IOX_69 | 70 | IOX_70 | IOX_70 | IOX_70 | IOX_70 | |

| 71 | IOX_71 | IOX_71 | IOX_71 | IOX_71 | 72 | IOX_72 | IOX_72 | IOX_72 | IOX_72 | |

| 73 | IOX_73 | IOX_73 | IOX_73 | IOX_73 | 74 | IOX_74 | IOX_74 | IOX_74 | IOX_74 | |

| 75 | IOX_75 | IOX_75 | IOX_75 | IOX_75 | 76 | IOX_76 | IOX_76 | IOX_76 | IOX_76 | |

| 77 | IOX_77 | IOX_77 | IOX_77 | IOX_77 | 78 | IOX_78 | IOX_78 | IOX_78 | IOX_78 | |

| 79 | IOX_79 | IOX_79 | IOX_79 | IOX_79 | 80 | IOX_80 | IOX_80 | IOX_80 | IOX_80 |

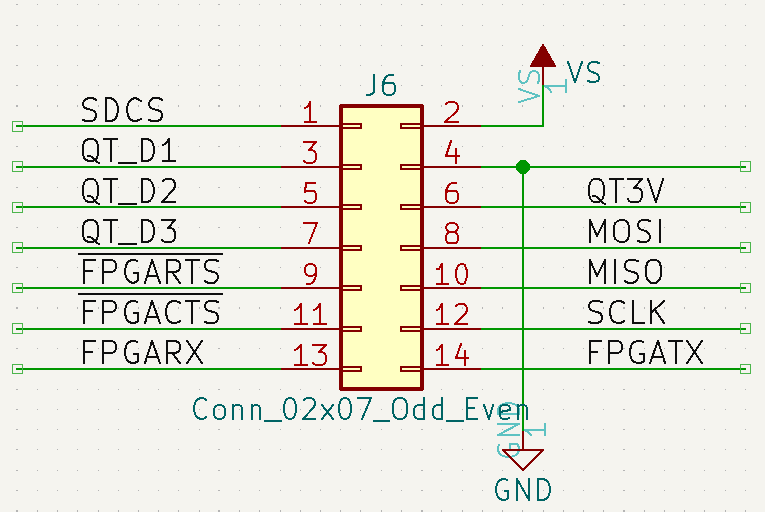

XIAO RP2040 (U1, J6)

- All pins are bought out to J1, J2 headers

- Used as an FTDI card replacement

- Tx/Rx/RTS/CTS brought to FPGA card

- Connected to SD Card

- SD Card is shared with FPGA

- Can be used as replacement disk drive for BASIC Load/Save commands

I/O Slots Power Select Jumper (H1)

- Can use 3.3V from FPGA card or on-noard 3.3V regulator

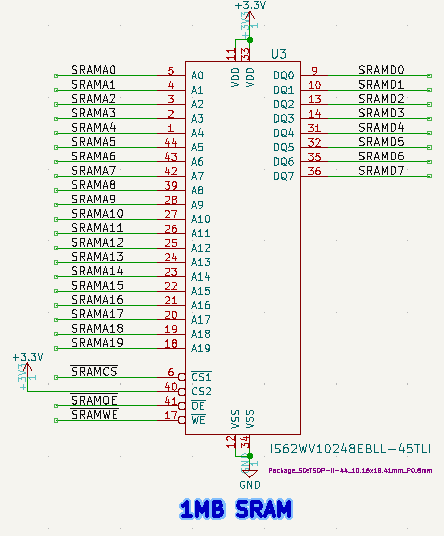

1 MB SRAM

- 1MB SRAM

- IS62WV10248EBLL-45TLI, SRAM. Async, 1Mbx8, 45ns

- For banked use in CP/M and as RAM Disk in other 8-bit micro designs

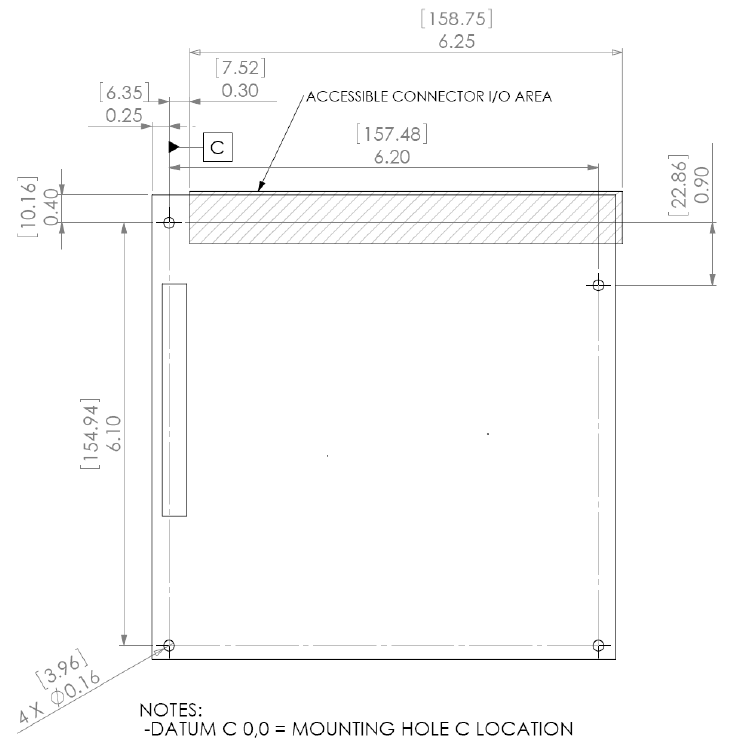

170x170mm, Mini-ITX card

- Mounting holes for Mini ITX case

- Ebay example

Card Mechanicals

Card Height