Difference between revisions of "QMTECH EP4CE15 FPGA Card"

Jump to navigation

Jump to search

Blwikiadmin (talk | contribs) |

Blwikiadmin (talk | contribs) |

||

| (19 intermediate revisions by the same user not shown) | |||

| Line 3: | Line 3: | ||

== Features == | == Features == | ||

| − | * Purchased FPGA | + | * Mounts to [[RETRO-EP4CE15]] FPGA Adapter card |

| − | * QMTECH EP4CE15 Board | + | * Altera Cyclone IV [https://www.digikey.com/product-detail/en/intel/EP4CE15F23C8N/544-2809-ND/2288329 EP4CE15F23C8N FPGA] |

| + | * Purchased [https://www.aliexpress.com/item/32949281189.html?spm=a2g0o.productlist.0.0.4210662fzJm4eF&algo_pvid=7e463362-226a-4171-8651-394df9cf19a6&algo_expid=7e463362-226a-4171-8651-394df9cf19a6-1&btsid=0ab6f82c15818053109856583ece19&ws_ab_test=searchweb0_0,searchweb201602_,searchweb201603_ QMTECH EP4CE15 FPGA Board] | ||

| + | ** [https://github.com/ChinaQMTECH/CYCLONE_IV_EP4CE15 QMTECH EP4CE15 FPGA Board] - QMTECH GitHib page | ||

* Crystal frequency: 50MHz | * Crystal frequency: 50MHz | ||

| − | * | + | * 32MB Winbond [https://www.winbond.com/resource-files/da00-w9825g6khc1.pdf W9825C6KH-6 4M X 4 Banks x 16 bits SDRAM] |

| − | |||

* W25Q64 SPI Flash | * W25Q64 SPI Flash | ||

| + | ** Select EPCQ64 | ||

* 3 Switches | * 3 Switches | ||

| + | * 2 LEDs | ||

* DC power jack | * DC power jack | ||

** 5V 1A | ** 5V 1A | ||

| Line 15: | Line 18: | ||

** Power supply | ** Power supply | ||

* 6.7cm x 8.4cm | * 6.7cm x 8.4cm | ||

| + | |||

| + | [[File:EP4CExx_Resources.PNG]] | ||

== Switches/Indications == | == Switches/Indications == | ||

| − | * LED - D4 | + | * Power LED - D4 |

| − | * LED - D5 | + | * User LED - D5 - FPGA Pin E4 |

| − | * SW1 | + | * KEY0 - SW1 - FPGA Pin W13 |

| − | * SW2 | + | * KEY1 - SW2 - FPGA Pin Y13 |

| − | * SW3 | + | * nCONFIG - SW3 |

* JP5 - 5V | * JP5 - 5V | ||

| Line 28: | Line 33: | ||

* J2 - JTAG | * J2 - JTAG | ||

| + | |||

| + | == Connectors == | ||

| + | |||

| + | === U7 === | ||

| + | |||

| + | [[File:U7_io_CONN.PNG]] | ||

| + | |||

| + | === U8 === | ||

| + | |||

| + | [[File:u8_io_CONN.PNG]] | ||

| + | |||

| + | == Programming the FPGA EEPROM == | ||

| + | |||

| + | * File | ||

| + | * Convert Programming File | ||

| + | * Configuration Device = EPCQ64 | ||

| + | * Mode = Active Serial | ||

| + | * Programming File Type: *.jic | ||

| + | * Advanced = Check both Disables... | ||

| + | * Select Flash Loader | ||

| + | * Add Device = Cyclone IV E and EP4CE15 | ||

| + | * Select SOF Data | ||

| + | * Select Add File and select the .sof file | ||

| + | * Generate | ||

| + | * In Tools, Programmer | ||

| + | * Add file and select the .jic file | ||

| + | * Select Program/Configure | ||

| + | * Takes a while to program | ||

| + | * Press button near VGA | ||

== Pages == | == Pages == | ||

| − | * [https://github.com/ChinaQMTECH/CYCLONE_IV_EP4CE15 QMTECH EP4CE15] | + | * [https://github.com/ChinaQMTECH/CYCLONE_IV_EP4CE15 QMTECH EP4CE15 Github] |

== Mechanicals == | == Mechanicals == | ||

[[File:QMTECH_FPGA_EP4CE15.jpg]] | [[File:QMTECH_FPGA_EP4CE15.jpg]] | ||

| + | == Pin List == | ||

| + | |||

| + | <pre> | ||

| + | set_location_assignment PIN_T2 -to i_CLOCK_50 | ||

| + | set_location_assignment PIN_W13 -to n_reset | ||

| + | set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to n_reset | ||

| + | set_location_assignment PIN_R1 -to ps2Clk | ||

| + | set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to ps2Clk | ||

| + | set_location_assignment PIN_R2 -to ps2Data | ||

| + | set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to ps2Data | ||

| + | set_location_assignment PIN_C22 -to serSelect | ||

| + | set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to serSelect | ||

| + | set_location_assignment PIN_A10 -to cts1 | ||

| + | set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to cts1 | ||

| + | set_location_assignment PIN_A13 -to rts1 | ||

| + | set_location_assignment PIN_B10 -to rxd1 | ||

| + | set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to rxd1 | ||

| + | set_location_assignment PIN_B13 -to txd1 | ||

| + | set_location_assignment PIN_B17 -to videoB0 | ||

| + | set_location_assignment PIN_A17 -to videoB1 | ||

| + | set_location_assignment PIN_B16 -to videoG0 | ||

| + | set_location_assignment PIN_A16 -to videoG1 | ||

| + | set_location_assignment PIN_B20 -to videoR0 | ||

| + | set_location_assignment PIN_A15 -to videoR1 | ||

| + | set_location_assignment PIN_B18 -to hSync | ||

| + | set_location_assignment PIN_A18 -to vSync | ||

| + | set_location_assignment PIN_F1 -to n_sRamCS | ||

| + | set_location_assignment PIN_B4 -to n_sRamWE | ||

| + | set_location_assignment PIN_J2 -to n_sRamOE | ||

| + | set_location_assignment PIN_E1 -to sramData[0] | ||

| + | set_location_assignment PIN_C1 -to sramData[1] | ||

| + | set_location_assignment PIN_B1 -to sramData[2] | ||

| + | set_location_assignment PIN_B3 -to sramData[3] | ||

| + | set_location_assignment PIN_B2 -to sramData[4] | ||

| + | set_location_assignment PIN_C2 -to sramData[5] | ||

| + | set_location_assignment PIN_D2 -to sramData[6] | ||

| + | set_location_assignment PIN_F2 -to sramData[7] | ||

| + | set_location_assignment PIN_H1 -to sramAddress[0] | ||

| + | set_location_assignment PIN_J1 -to sramAddress[1] | ||

| + | set_location_assignment PIN_M1 -to sramAddress[2] | ||

| + | set_location_assignment PIN_N1 -to sramAddress[3] | ||

| + | set_location_assignment PIN_A8 -to sramAddress[15] | ||

| + | set_location_assignment PIN_A7 -to sramAddress[14] | ||

| + | set_location_assignment PIN_A6 -to sramAddress[13] | ||

| + | set_location_assignment PIN_A5 -to sramAddress[12] | ||

| + | set_location_assignment PIN_C3 -to sramAddress[11] | ||

| + | set_location_assignment PIN_A4 -to sramAddress[10] | ||

| + | set_location_assignment PIN_A3 -to sramAddress[9] | ||

| + | set_location_assignment PIN_H2 -to sramAddress[8] | ||

| + | set_location_assignment PIN_M2 -to sramAddress[7] | ||

| + | set_location_assignment PIN_N2 -to sramAddress[6] | ||

| + | set_location_assignment PIN_P2 -to sramAddress[5] | ||

| + | set_location_assignment PIN_P1 -to sramAddress[4] | ||

| + | set_location_assignment PIN_B5 -to sramAddress[18] | ||

| + | set_location_assignment PIN_B6 -to sramAddress[17] | ||

| + | set_location_assignment PIN_B7 -to sramAddress[16] | ||

| + | # SDRAM | ||

| + | set_location_assignment PIN_Y6 -to sdRamClk | ||

| + | set_location_assignment PIN_W6 -to sdRamClkEn | ||

| + | set_location_assignment PIN_AA4 -to n_sdRamCas | ||

| + | set_location_assignment PIN_AA3 -to n_sdRamCe | ||

| + | set_location_assignment PIN_AB3 -to n_sdRamRas | ||

| + | set_location_assignment PIN_AB4 -to n_sdRamWe | ||

| + | set_location_assignment PIN_V2 -to sdRamAddr[0] | ||

| + | set_location_assignment PIN_V1 -to sdRamAddr[1] | ||

| + | set_location_assignment PIN_U2 -to sdRamAddr[2] | ||

| + | set_location_assignment PIN_U1 -to sdRamAddr[3] | ||

| + | set_location_assignment PIN_V3 -to sdRamAddr[4] | ||

| + | set_location_assignment PIN_V4 -to sdRamAddr[5] | ||

| + | set_location_assignment PIN_Y2 -to sdRamAddr[6] | ||

| + | set_location_assignment PIN_AA1 -to sdRamAddr[7] | ||

| + | set_location_assignment PIN_Y3 -to sdRamAddr[8] | ||

| + | set_location_assignment PIN_V5 -to sdRamAddr[9] | ||

| + | set_location_assignment PIN_W1 -to sdRamAddr[10] | ||

| + | set_location_assignment PIN_Y4 -to sdRamAddr[11] | ||

| + | set_location_assignment PIN_V6 -to sdRamAddr[12] | ||

| + | set_location_assignment PIN_Y1 -to sdRamAddr[13] | ||

| + | set_location_assignment PIN_W2 -to sdRamAddr[14] | ||

| + | set_location_assignment PIN_AA10 -to sdRamData[0] | ||

| + | set_location_assignment PIN_AB9 -to sdRamData[1] | ||

| + | set_location_assignment PIN_AA9 -to sdRamData[2] | ||

| + | set_location_assignment PIN_AB8 -to sdRamData[3] | ||

| + | set_location_assignment PIN_AA8 -to sdRamData[4] | ||

| + | set_location_assignment PIN_AB7 -to sdRamData[5] | ||

| + | set_location_assignment PIN_AA7 -to sdRamData[6] | ||

| + | set_location_assignment PIN_AB5 -to sdRamData[7] | ||

| + | set_location_assignment PIN_Y7 -to sdRamData[8] | ||

| + | set_location_assignment PIN_W8 -to sdRamData[9] | ||

| + | set_location_assignment PIN_Y8 -to sdRamData[10] | ||

| + | set_location_assignment PIN_V9 -to sdRamData[11] | ||

| + | set_location_assignment PIN_V10 -to sdRamData[12] | ||

| + | set_location_assignment PIN_Y10 -to sdRamData[13] | ||

| + | set_location_assignment PIN_W10 -to sdRamData[14] | ||

| + | set_location_assignment PIN_V11 -to sdRamData[15] | ||

| + | set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to hSync | ||

| + | set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to n_reset | ||

| + | set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to ps2Clk | ||

| + | set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to ps2Data | ||

| + | set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to videoB0 | ||

| + | set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to videoB1 | ||

| + | set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to videoG0 | ||

| + | set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to videoG1 | ||

| + | set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to videoR0 | ||

| + | set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to videoR1 | ||

| + | set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to vSync | ||

| + | set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to rts1 | ||

| + | set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to rxd1 | ||

| + | set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to txd1 | ||

| + | set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to n_sRamCS | ||

| + | set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to n_sRamOE | ||

| + | set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to n_sRamWE | ||

| + | set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sramData[0] | ||

| + | set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sramData[1] | ||

| + | set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sramData[2] | ||

| + | set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sramData[3] | ||

| + | set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sramData[4] | ||

| + | set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sramData[5] | ||

| + | set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sramData[6] | ||

| + | set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sramData[7] | ||

| + | set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sramAddress[0] | ||

| + | set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sramAddress[1] | ||

| + | set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sramAddress[2] | ||

| + | set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sramAddress[3] | ||

| + | set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sramAddress[4] | ||

| + | set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sramAddress[5] | ||

| + | set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sramAddress[6] | ||

| + | set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sramAddress[7] | ||

| + | set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sramAddress[8] | ||

| + | set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sramAddress[15] | ||

| + | set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sramAddress[14] | ||

| + | set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sramAddress[13] | ||

| + | set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sramAddress[10] | ||

| + | set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sramAddress[9] | ||

| + | set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sramAddress[11] | ||

| + | set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sramAddress[12] | ||

| + | set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sramAddress[16] | ||

| + | set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sramAddress[17] | ||

| + | set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sramAddress[18] | ||

| + | </pre> | ||

Latest revision as of 12:13, 12 March 2021

Contents

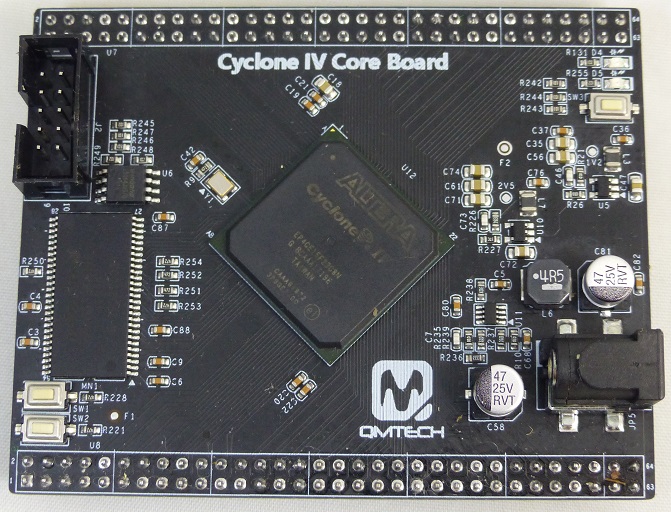

Features

- Mounts to RETRO-EP4CE15 FPGA Adapter card

- Altera Cyclone IV EP4CE15F23C8N FPGA

- Purchased QMTECH EP4CE15 FPGA Board

- QMTECH EP4CE15 FPGA Board - QMTECH GitHib page

- Crystal frequency: 50MHz

- 32MB Winbond W9825C6KH-6 4M X 4 Banks x 16 bits SDRAM

- W25Q64 SPI Flash

- Select EPCQ64

- 3 Switches

- 2 LEDs

- DC power jack

- 5V 1A

- DC-050, 5.5mmx2.1mm

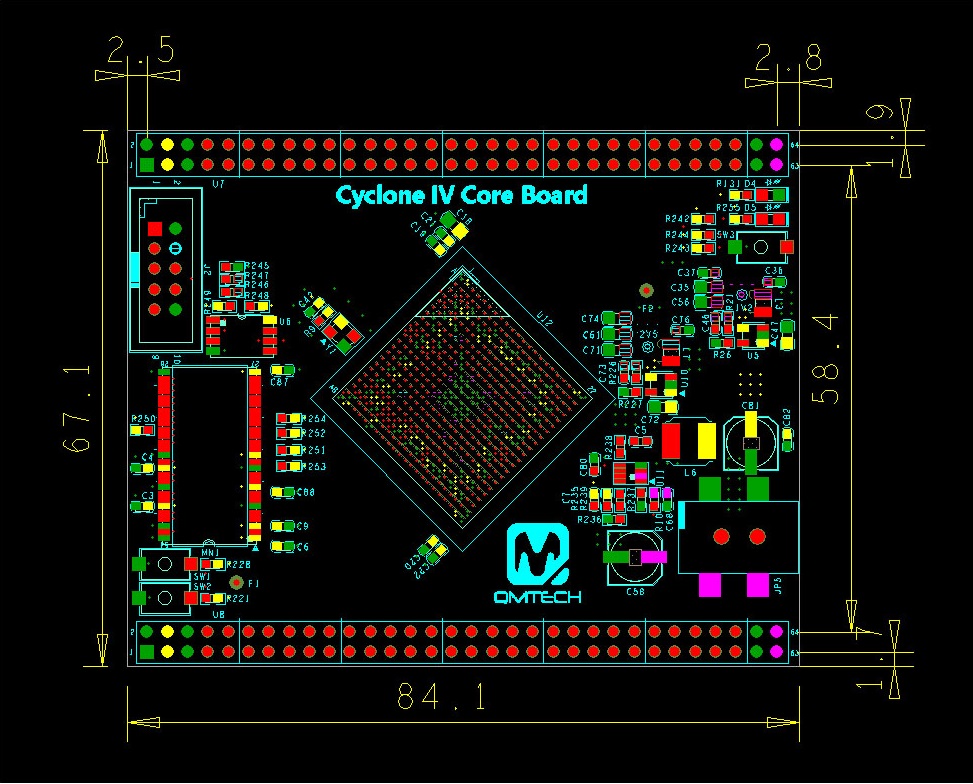

- Power supply

- 6.7cm x 8.4cm

Switches/Indications

- Power LED - D4

- User LED - D5 - FPGA Pin E4

- KEY0 - SW1 - FPGA Pin W13

- KEY1 - SW2 - FPGA Pin Y13

- nCONFIG - SW3

- JP5 - 5V

Jumpers

- J2 - JTAG

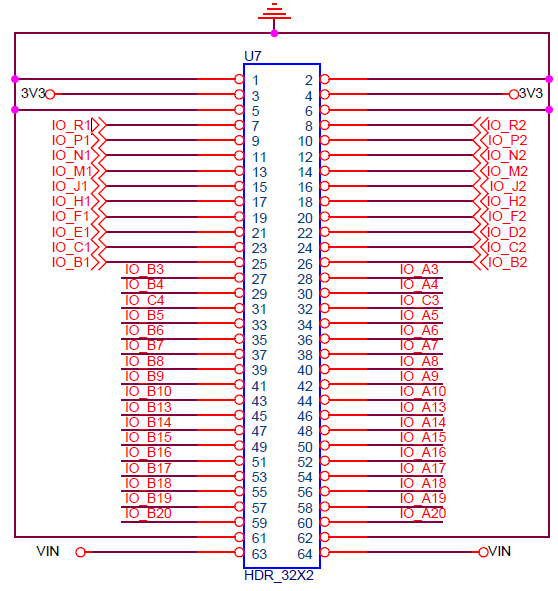

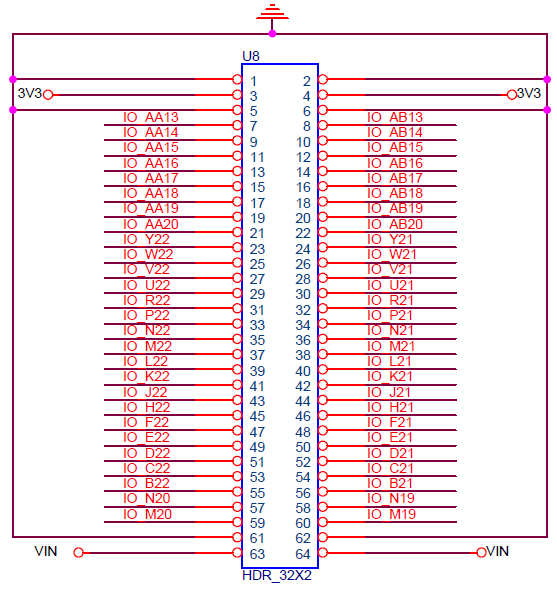

Connectors

U7

U8

Programming the FPGA EEPROM

- File

- Convert Programming File

- Configuration Device = EPCQ64

- Mode = Active Serial

- Programming File Type: *.jic

- Advanced = Check both Disables...

- Select Flash Loader

- Add Device = Cyclone IV E and EP4CE15

- Select SOF Data

- Select Add File and select the .sof file

- Generate

- In Tools, Programmer

- Add file and select the .jic file

- Select Program/Configure

- Takes a while to program

- Press button near VGA

Pages

Mechanicals

Pin List

set_location_assignment PIN_T2 -to i_CLOCK_50 set_location_assignment PIN_W13 -to n_reset set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to n_reset set_location_assignment PIN_R1 -to ps2Clk set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to ps2Clk set_location_assignment PIN_R2 -to ps2Data set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to ps2Data set_location_assignment PIN_C22 -to serSelect set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to serSelect set_location_assignment PIN_A10 -to cts1 set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to cts1 set_location_assignment PIN_A13 -to rts1 set_location_assignment PIN_B10 -to rxd1 set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to rxd1 set_location_assignment PIN_B13 -to txd1 set_location_assignment PIN_B17 -to videoB0 set_location_assignment PIN_A17 -to videoB1 set_location_assignment PIN_B16 -to videoG0 set_location_assignment PIN_A16 -to videoG1 set_location_assignment PIN_B20 -to videoR0 set_location_assignment PIN_A15 -to videoR1 set_location_assignment PIN_B18 -to hSync set_location_assignment PIN_A18 -to vSync set_location_assignment PIN_F1 -to n_sRamCS set_location_assignment PIN_B4 -to n_sRamWE set_location_assignment PIN_J2 -to n_sRamOE set_location_assignment PIN_E1 -to sramData[0] set_location_assignment PIN_C1 -to sramData[1] set_location_assignment PIN_B1 -to sramData[2] set_location_assignment PIN_B3 -to sramData[3] set_location_assignment PIN_B2 -to sramData[4] set_location_assignment PIN_C2 -to sramData[5] set_location_assignment PIN_D2 -to sramData[6] set_location_assignment PIN_F2 -to sramData[7] set_location_assignment PIN_H1 -to sramAddress[0] set_location_assignment PIN_J1 -to sramAddress[1] set_location_assignment PIN_M1 -to sramAddress[2] set_location_assignment PIN_N1 -to sramAddress[3] set_location_assignment PIN_A8 -to sramAddress[15] set_location_assignment PIN_A7 -to sramAddress[14] set_location_assignment PIN_A6 -to sramAddress[13] set_location_assignment PIN_A5 -to sramAddress[12] set_location_assignment PIN_C3 -to sramAddress[11] set_location_assignment PIN_A4 -to sramAddress[10] set_location_assignment PIN_A3 -to sramAddress[9] set_location_assignment PIN_H2 -to sramAddress[8] set_location_assignment PIN_M2 -to sramAddress[7] set_location_assignment PIN_N2 -to sramAddress[6] set_location_assignment PIN_P2 -to sramAddress[5] set_location_assignment PIN_P1 -to sramAddress[4] set_location_assignment PIN_B5 -to sramAddress[18] set_location_assignment PIN_B6 -to sramAddress[17] set_location_assignment PIN_B7 -to sramAddress[16] # SDRAM set_location_assignment PIN_Y6 -to sdRamClk set_location_assignment PIN_W6 -to sdRamClkEn set_location_assignment PIN_AA4 -to n_sdRamCas set_location_assignment PIN_AA3 -to n_sdRamCe set_location_assignment PIN_AB3 -to n_sdRamRas set_location_assignment PIN_AB4 -to n_sdRamWe set_location_assignment PIN_V2 -to sdRamAddr[0] set_location_assignment PIN_V1 -to sdRamAddr[1] set_location_assignment PIN_U2 -to sdRamAddr[2] set_location_assignment PIN_U1 -to sdRamAddr[3] set_location_assignment PIN_V3 -to sdRamAddr[4] set_location_assignment PIN_V4 -to sdRamAddr[5] set_location_assignment PIN_Y2 -to sdRamAddr[6] set_location_assignment PIN_AA1 -to sdRamAddr[7] set_location_assignment PIN_Y3 -to sdRamAddr[8] set_location_assignment PIN_V5 -to sdRamAddr[9] set_location_assignment PIN_W1 -to sdRamAddr[10] set_location_assignment PIN_Y4 -to sdRamAddr[11] set_location_assignment PIN_V6 -to sdRamAddr[12] set_location_assignment PIN_Y1 -to sdRamAddr[13] set_location_assignment PIN_W2 -to sdRamAddr[14] set_location_assignment PIN_AA10 -to sdRamData[0] set_location_assignment PIN_AB9 -to sdRamData[1] set_location_assignment PIN_AA9 -to sdRamData[2] set_location_assignment PIN_AB8 -to sdRamData[3] set_location_assignment PIN_AA8 -to sdRamData[4] set_location_assignment PIN_AB7 -to sdRamData[5] set_location_assignment PIN_AA7 -to sdRamData[6] set_location_assignment PIN_AB5 -to sdRamData[7] set_location_assignment PIN_Y7 -to sdRamData[8] set_location_assignment PIN_W8 -to sdRamData[9] set_location_assignment PIN_Y8 -to sdRamData[10] set_location_assignment PIN_V9 -to sdRamData[11] set_location_assignment PIN_V10 -to sdRamData[12] set_location_assignment PIN_Y10 -to sdRamData[13] set_location_assignment PIN_W10 -to sdRamData[14] set_location_assignment PIN_V11 -to sdRamData[15] set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to hSync set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to n_reset set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to ps2Clk set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to ps2Data set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to videoB0 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to videoB1 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to videoG0 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to videoG1 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to videoR0 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to videoR1 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to vSync set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to rts1 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to rxd1 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to txd1 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to n_sRamCS set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to n_sRamOE set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to n_sRamWE set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sramData[0] set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sramData[1] set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sramData[2] set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sramData[3] set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sramData[4] set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sramData[5] set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sramData[6] set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sramData[7] set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sramAddress[0] set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sramAddress[1] set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sramAddress[2] set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sramAddress[3] set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sramAddress[4] set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sramAddress[5] set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sramAddress[6] set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sramAddress[7] set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sramAddress[8] set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sramAddress[15] set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sramAddress[14] set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sramAddress[13] set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sramAddress[10] set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sramAddress[9] set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sramAddress[11] set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sramAddress[12] set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sramAddress[16] set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sramAddress[17] set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sramAddress[18]