Difference between revisions of "LB-BKOUT-01"

Jump to navigation

Jump to search

Blwikiadmin (talk | contribs) |

Blwikiadmin (talk | contribs) |

||

| (20 intermediate revisions by the same user not shown) | |||

| Line 5: | Line 5: | ||

* Breakout all bus lines | * Breakout all bus lines | ||

* PWR/GND bus down the middle | * PWR/GND bus down the middle | ||

| + | |||

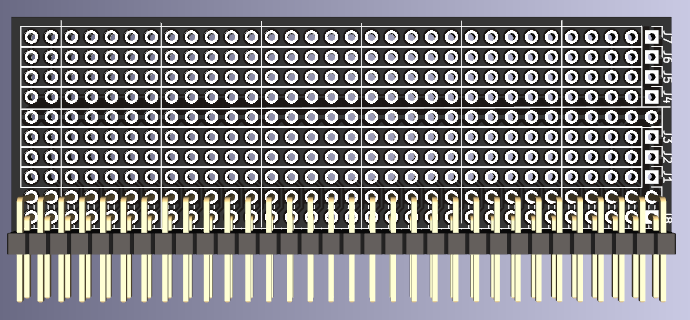

| + | [[file:LB-BKOUT_Routing.PNG]] | ||

| + | |||

| + | === NOP Tester === | ||

| + | |||

| + | [[file:LB-NOP_P1657-720px.JPG]] | ||

| + | |||

| + | * Card Can be used as a NOP tester | ||

| + | ** 10K pullup D0-D7 to Vcc | ||

| + | ** Pull down to ground with jumpers to ground strip | ||

| + | |||

| + | ==== NOP values ==== | ||

| + | |||

| + | * Z80 = 0x00 | ||

| + | * MC6809 = 0x12 | ||

| + | * 6502 = 0xEA | ||

| + | * M6800/M6802 = 0x01 | ||

| + | * MC60000 = 0x4E71 | ||

== Connectors == | == Connectors == | ||

| Line 10: | Line 28: | ||

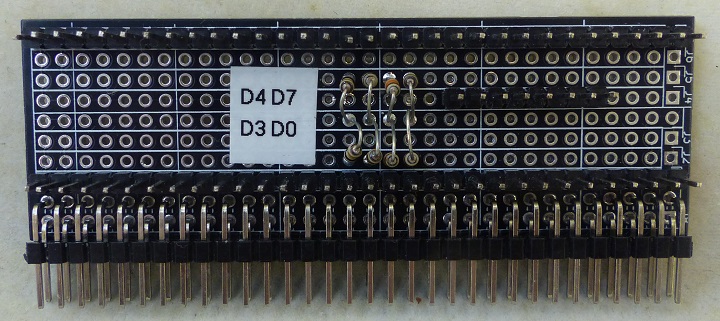

=== J8 - Backplane Connector === | === J8 - Backplane Connector === | ||

| − | [[file:LB-BKOUT- | + | [[file:LB-BKOUT-01_J8.PNG]] |

| − | === J1-J3 | + | ==== Backplane Pinout ==== |

| + | |||

| + | [[file:LB-6802-01_BKPL.PNG]] | ||

| + | |||

| + | {| class="wikitable" | ||

| + | ! Pin | ||

| + | ! LBMEM | ||

| + | ! LBZ80 | ||

| + | ! LB65C816 | ||

| + | ! LBLOGIC | ||

| + | |- | ||

| + | | 1 | ||

| + | | VCC | ||

| + | | VCC | ||

| + | | VCC | ||

| + | | VCC | ||

| + | |- | ||

| + | | 2 | ||

| + | | VCC | ||

| + | | VCC | ||

| + | | VCC | ||

| + | | VCC | ||

| + | |- | ||

| + | | 3 | ||

| + | | CPUA22 | ||

| + | | CPUA22 | ||

| + | | CPUA22 | ||

| + | | P2[6] | ||

| + | |- | ||

| + | | 4 | ||

| + | | CPUA23 | ||

| + | | CPUA23 | ||

| + | | CPUA23 | ||

| + | | P2[7] | ||

| + | |- | ||

| + | | 5 | ||

| + | | CPUA20 | ||

| + | | CPUA20 | ||

| + | | CPUA20 | ||

| + | | P2[4] | ||

| + | |- | ||

| + | | 6 | ||

| + | | CPUA21 | ||

| + | | CPUA21 | ||

| + | | CPUA21 | ||

| + | | P2[5] | ||

| + | |- | ||

| + | | 7 | ||

| + | | CPUA18 | ||

| + | | CPUA18 | ||

| + | | CPUA18 | ||

| + | | P2[2] | ||

| + | |- | ||

| + | | 8 | ||

| + | | CPUA19 | ||

| + | | CPUA19 | ||

| + | | CPUA19 | ||

| + | | P2[3] | ||

| + | |- | ||

| + | | 9 | ||

| + | | CPUA16 | ||

| + | | CPUA16 | ||

| + | | CPUA16 | ||

| + | | P2[0] | ||

| + | |- | ||

| + | | 10 | ||

| + | | CPUA17 | ||

| + | | CPUA17 | ||

| + | | CPUA17 | ||

| + | | P2[1] | ||

| + | |- | ||

| + | | 11 | ||

| + | | CPUA14 | ||

| + | | CPUA14 | ||

| + | | CPUA14 | ||

| + | | P4[6] | ||

| + | |- | ||

| + | | 12 | ||

| + | | CPUA15 | ||

| + | | CPUA15 | ||

| + | | CPUA15 | ||

| + | | P4[7] | ||

| + | |- | ||

| + | | 13 | ||

| + | | CPUA12 | ||

| + | | CPUA12 | ||

| + | | CPUA12 | ||

| + | | P4[4] | ||

| + | |- | ||

| + | | 14 | ||

| + | | CPUA13 | ||

| + | | CPUA13 | ||

| + | | CPUA13 | ||

| + | | P4[5] | ||

| + | |- | ||

| + | | 15 | ||

| + | | CPUA10 | ||

| + | | CPUA10 | ||

| + | | CPUA10 | ||

| + | | P4[2] | ||

| + | |- | ||

| + | | 16 | ||

| + | | CPUA11 | ||

| + | | CPUA11 | ||

| + | | CPUA11 | ||

| + | | P4[3] | ||

| + | |- | ||

| + | | 17 | ||

| + | | CPUA08 | ||

| + | | CPUA8 | ||

| + | | CPUA8 | ||

| + | | P4[0] | ||

| + | |- | ||

| + | | 18 | ||

| + | | CPUA09 | ||

| + | | CPUA9 | ||

| + | | CPUA9 | ||

| + | | P4[1] | ||

| + | |- | ||

| + | | 19 | ||

| + | | CPUA06 | ||

| + | | CPUA6 | ||

| + | | CPUA6 | ||

| + | | P0[6] | ||

| + | |- | ||

| + | | 20 | ||

| + | | CPUA07 | ||

| + | | CPUA7 | ||

| + | | CPUA7 | ||

| + | | P0[7] | ||

| + | |- | ||

| + | | 21 | ||

| + | | CPUA04 | ||

| + | | CPUA4 | ||

| + | | CPUA4 | ||

| + | | P0[4] | ||

| + | |- | ||

| + | | 22 | ||

| + | | CPUA05 | ||

| + | | CPUA5 | ||

| + | | CPUA5 | ||

| + | | P0[5] | ||

| + | |- | ||

| + | | 23 | ||

| + | | CPUA02 | ||

| + | | CPUA2 | ||

| + | | CPUA2 | ||

| + | | P0[2] | ||

| + | |- | ||

| + | | 24 | ||

| + | | CPUA03 | ||

| + | | CPUA3 | ||

| + | | CPUA3 | ||

| + | | P0[3] | ||

| + | |- | ||

| + | | 25 | ||

| + | | CPUA00 | ||

| + | | CPUA0 | ||

| + | | CPUA0 | ||

| + | | P0[0] | ||

| + | |- | ||

| + | | 26 | ||

| + | | CPUA01 | ||

| + | | CPUA1 | ||

| + | | CPUA1 | ||

| + | | P0[1] | ||

| + | |- | ||

| + | | 27 | ||

| + | | CPUD0 | ||

| + | | CPUD0 | ||

| + | | CPUD0 | ||

| + | | P12[0] | ||

| + | |- | ||

| + | | 28 | ||

| + | | CPUD7 | ||

| + | | CPUD7 | ||

| + | | CPUD7 | ||

| + | | P12[7] | ||

| + | |- | ||

| + | | 29 | ||

| + | | CPUD1 | ||

| + | | CPUD1 | ||

| + | | CPUD1 | ||

| + | | P12[1] | ||

| + | |- | ||

| + | | 30 | ||

| + | | CPUD6 | ||

| + | | CPUD6 | ||

| + | | CPUD6 | ||

| + | | P12[6] | ||

| + | |- | ||

| + | | 31 | ||

| + | | CPUD2 | ||

| + | | CPUD2 | ||

| + | | CPUD2 | ||

| + | | P12[2] | ||

| + | |- | ||

| + | | 32 | ||

| + | | CPUD5 | ||

| + | | CPUD5 | ||

| + | | CPUD5 | ||

| + | | P12[5] | ||

| + | |- | ||

| + | | 33 | ||

| + | | CPUD3 | ||

| + | | CPUD3 | ||

| + | | CPUD3 | ||

| + | | P12[3] | ||

| + | |- | ||

| + | | 34 | ||

| + | | CPUD4 | ||

| + | | CPUD4 | ||

| + | | CPUD4 | ||

| + | | P12[4] | ||

| + | |- | ||

| + | | 35 | ||

| + | | MEMRD* | ||

| + | | N/A | ||

| + | | N/A | ||

| + | | P3[7] | ||

| + | |- | ||

| + | | 36 | ||

| + | | RAMSEL* | ||

| + | | N/A | ||

| + | | N/A | ||

| + | | P3[6] | ||

| + | |- | ||

| + | | 37 | ||

| + | | IOCS* | ||

| + | | N/A | ||

| + | | N/A | ||

| + | | P3[4] | ||

| + | |- | ||

| + | | 38 | ||

| + | | ROMSEL* | ||

| + | | N/A | ||

| + | | N/A | ||

| + | | P3[5] | ||

| + | |- | ||

| + | | 39 | ||

| + | | GND | ||

| + | | GND | ||

| + | | GND | ||

| + | | GND | ||

| + | |- | ||

| + | | 40 | ||

| + | | GND | ||

| + | | GND | ||

| + | | GND | ||

| + | | GND | ||

| + | |- | ||

| + | | 41 | ||

| + | | N/A | ||

| + | | CPUCLK | ||

| + | | CPUCLK | ||

| + | | P3[3] | ||

| + | |- | ||

| + | | 42 | ||

| + | | N/A | ||

| + | | RFSH | ||

| + | | VPA | ||

| + | | P3[2] | ||

| + | |- | ||

| + | | 43 | ||

| + | | N/A | ||

| + | | INT* | ||

| + | | IRQB* | ||

| + | | P3[1] | ||

| + | |- | ||

| + | | 44 | ||

| + | | N/A | ||

| + | | M1* | ||

| + | | VPB | ||

| + | | P3[0] | ||

| + | |- | ||

| + | | 45 | ||

| + | | N/A | ||

| + | | NMI* | ||

| + | | NMIB* | ||

| + | | P5[7] | ||

| + | |- | ||

| + | | 46 | ||

| + | | N/A | ||

| + | | CPURST* | ||

| + | | CPURESB* | ||

| + | | P5[6] | ||

| + | |- | ||

| + | | 47 | ||

| + | | N/A | ||

| + | | HALT* | ||

| + | | ABORT* | ||

| + | | P5[5] | ||

| + | |- | ||

| + | | 48 | ||

| + | | N/A | ||

| + | | BUSRQ* | ||

| + | | MLB | ||

| + | | P5[4] | ||

| + | |- | ||

| + | | 49 | ||

| + | | N/A | ||

| + | | MREQ* | ||

| + | | VDA | ||

| + | | P1[7] | ||

| + | |- | ||

| + | | 50 | ||

| + | | N/A | ||

| + | | WAIT* | ||

| + | | RDY | ||

| + | | P1[6] | ||

| + | |- | ||

| + | | 51 | ||

| + | | N/A | ||

| + | | IORQ* | ||

| + | | IRQB* | ||

| + | | P1[5] | ||

| + | |- | ||

| + | | 52 | ||

| + | | N/A | ||

| + | | BUSACK* | ||

| + | | CPUE | ||

| + | | P1[4] | ||

| + | |- | ||

| + | | 53 | ||

| + | | N/A | ||

| + | | CPURD* | ||

| + | | CPUMX | ||

| + | | P5[3] | ||

| + | |- | ||

| + | | 54 | ||

| + | | N/A | ||

| + | | CPUWR* | ||

| + | | RWB | ||

| + | | P5[2] | ||

| + | |- | ||

| + | | 55 | ||

| + | | N/A | ||

| + | | N/A | ||

| + | | N/A | ||

| + | | N/A | ||

| + | |- | ||

| + | | 56 | ||

| + | | N/A | ||

| + | | N/A | ||

| + | | N/A | ||

| + | | N/A | ||

| + | |- | ||

| + | | 57 | ||

| + | | N/A | ||

| + | | N/A | ||

| + | | N/A | ||

| + | | N/A | ||

| + | |- | ||

| + | | 58 | ||

| + | | N/A | ||

| + | | N/A | ||

| + | | N/A | ||

| + | | N/A | ||

| + | |- | ||

| + | | 59 | ||

| + | | N/A | ||

| + | | N/A | ||

| + | | N/A | ||

| + | | N/A | ||

| + | |- | ||

| + | | 60 | ||

| + | | N/A | ||

| + | | N/A | ||

| + | | N/A | ||

| + | | N/A | ||

| + | |- | ||

| + | | 61 | ||

| + | | N/A | ||

| + | | N/A | ||

| + | | N/A | ||

| + | | N/A | ||

| + | |- | ||

| + | | 62 | ||

| + | | N/A | ||

| + | | N/A | ||

| + | | N/A | ||

| + | | N/A | ||

| + | |- | ||

| + | | 63 | ||

| + | | N/A | ||

| + | | N/A | ||

| + | | N/A | ||

| + | | N/A | ||

| + | |- | ||

| + | | 64 | ||

| + | | N/A | ||

| + | | N/A | ||

| + | | N/A | ||

| + | | N/A | ||

| + | |- | ||

| + | |} | ||

| + | |||

| + | === J1-J3 Lower Pins === | ||

[[file:LB-BKOUT-01_J1-J3.PNG]] | [[file:LB-BKOUT-01_J1-J3.PNG]] | ||

| Line 27: | Line 442: | ||

[[file:LB-BKOUT_MECHS.PNG]] | [[file:LB-BKOUT_MECHS.PNG]] | ||

| + | |||

| + | == Checkout == | ||

| + | |||

| + | * GND S/B on P39/P40 not P63/P64 | ||

| + | ** Jumper P39 to ground bus down center | ||

| + | ** Jumper P40 to ground bus down center | ||

Latest revision as of 13:25, 4 September 2024

Contents

Features

- Breakout all bus lines

- PWR/GND bus down the middle

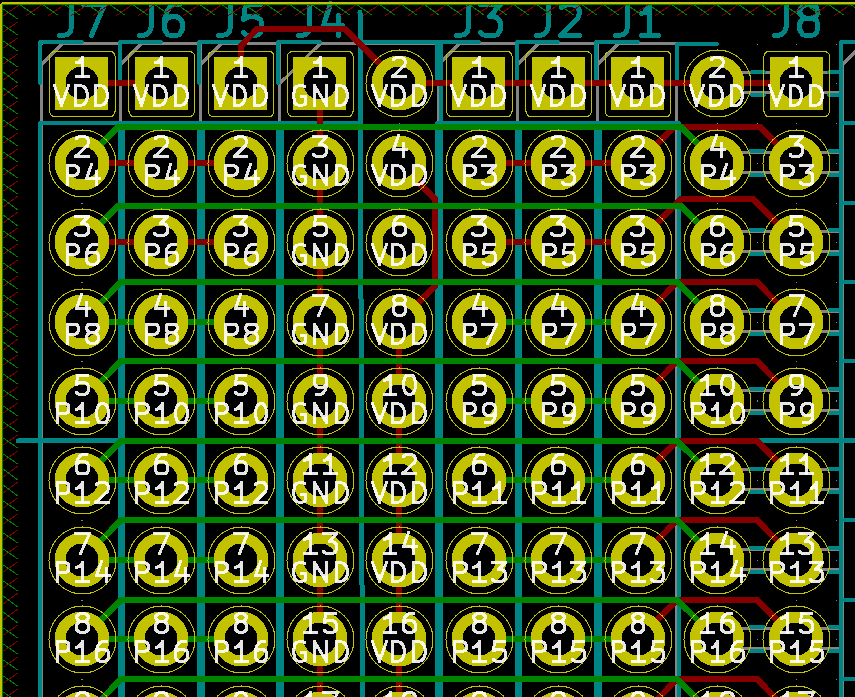

NOP Tester

- Card Can be used as a NOP tester

- 10K pullup D0-D7 to Vcc

- Pull down to ground with jumpers to ground strip

NOP values

- Z80 = 0x00

- MC6809 = 0x12

- 6502 = 0xEA

- M6800/M6802 = 0x01

- MC60000 = 0x4E71

Connectors

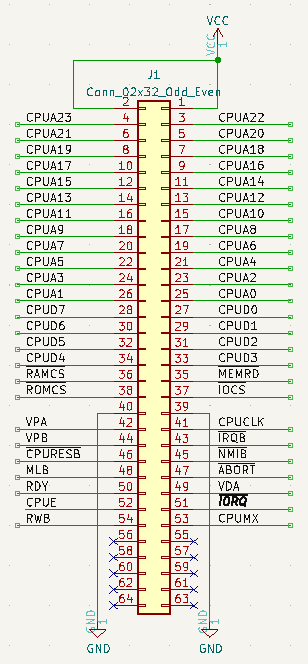

J8 - Backplane Connector

Backplane Pinout

| Pin | LBMEM | LBZ80 | LB65C816 | LBLOGIC |

|---|---|---|---|---|

| 1 | VCC | VCC | VCC | VCC |

| 2 | VCC | VCC | VCC | VCC |

| 3 | CPUA22 | CPUA22 | CPUA22 | P2[6] |

| 4 | CPUA23 | CPUA23 | CPUA23 | P2[7] |

| 5 | CPUA20 | CPUA20 | CPUA20 | P2[4] |

| 6 | CPUA21 | CPUA21 | CPUA21 | P2[5] |

| 7 | CPUA18 | CPUA18 | CPUA18 | P2[2] |

| 8 | CPUA19 | CPUA19 | CPUA19 | P2[3] |

| 9 | CPUA16 | CPUA16 | CPUA16 | P2[0] |

| 10 | CPUA17 | CPUA17 | CPUA17 | P2[1] |

| 11 | CPUA14 | CPUA14 | CPUA14 | P4[6] |

| 12 | CPUA15 | CPUA15 | CPUA15 | P4[7] |

| 13 | CPUA12 | CPUA12 | CPUA12 | P4[4] |

| 14 | CPUA13 | CPUA13 | CPUA13 | P4[5] |

| 15 | CPUA10 | CPUA10 | CPUA10 | P4[2] |

| 16 | CPUA11 | CPUA11 | CPUA11 | P4[3] |

| 17 | CPUA08 | CPUA8 | CPUA8 | P4[0] |

| 18 | CPUA09 | CPUA9 | CPUA9 | P4[1] |

| 19 | CPUA06 | CPUA6 | CPUA6 | P0[6] |

| 20 | CPUA07 | CPUA7 | CPUA7 | P0[7] |

| 21 | CPUA04 | CPUA4 | CPUA4 | P0[4] |

| 22 | CPUA05 | CPUA5 | CPUA5 | P0[5] |

| 23 | CPUA02 | CPUA2 | CPUA2 | P0[2] |

| 24 | CPUA03 | CPUA3 | CPUA3 | P0[3] |

| 25 | CPUA00 | CPUA0 | CPUA0 | P0[0] |

| 26 | CPUA01 | CPUA1 | CPUA1 | P0[1] |

| 27 | CPUD0 | CPUD0 | CPUD0 | P12[0] |

| 28 | CPUD7 | CPUD7 | CPUD7 | P12[7] |

| 29 | CPUD1 | CPUD1 | CPUD1 | P12[1] |

| 30 | CPUD6 | CPUD6 | CPUD6 | P12[6] |

| 31 | CPUD2 | CPUD2 | CPUD2 | P12[2] |

| 32 | CPUD5 | CPUD5 | CPUD5 | P12[5] |

| 33 | CPUD3 | CPUD3 | CPUD3 | P12[3] |

| 34 | CPUD4 | CPUD4 | CPUD4 | P12[4] |

| 35 | MEMRD* | N/A | N/A | P3[7] |

| 36 | RAMSEL* | N/A | N/A | P3[6] |

| 37 | IOCS* | N/A | N/A | P3[4] |

| 38 | ROMSEL* | N/A | N/A | P3[5] |

| 39 | GND | GND | GND | GND |

| 40 | GND | GND | GND | GND |

| 41 | N/A | CPUCLK | CPUCLK | P3[3] |

| 42 | N/A | RFSH | VPA | P3[2] |

| 43 | N/A | INT* | IRQB* | P3[1] |

| 44 | N/A | M1* | VPB | P3[0] |

| 45 | N/A | NMI* | NMIB* | P5[7] |

| 46 | N/A | CPURST* | CPURESB* | P5[6] |

| 47 | N/A | HALT* | ABORT* | P5[5] |

| 48 | N/A | BUSRQ* | MLB | P5[4] |

| 49 | N/A | MREQ* | VDA | P1[7] |

| 50 | N/A | WAIT* | RDY | P1[6] |

| 51 | N/A | IORQ* | IRQB* | P1[5] |

| 52 | N/A | BUSACK* | CPUE | P1[4] |

| 53 | N/A | CPURD* | CPUMX | P5[3] |

| 54 | N/A | CPUWR* | RWB | P5[2] |

| 55 | N/A | N/A | N/A | N/A |

| 56 | N/A | N/A | N/A | N/A |

| 57 | N/A | N/A | N/A | N/A |

| 58 | N/A | N/A | N/A | N/A |

| 59 | N/A | N/A | N/A | N/A |

| 60 | N/A | N/A | N/A | N/A |

| 61 | N/A | N/A | N/A | N/A |

| 62 | N/A | N/A | N/A | N/A |

| 63 | N/A | N/A | N/A | N/A |

| 64 | N/A | N/A | N/A | N/A |

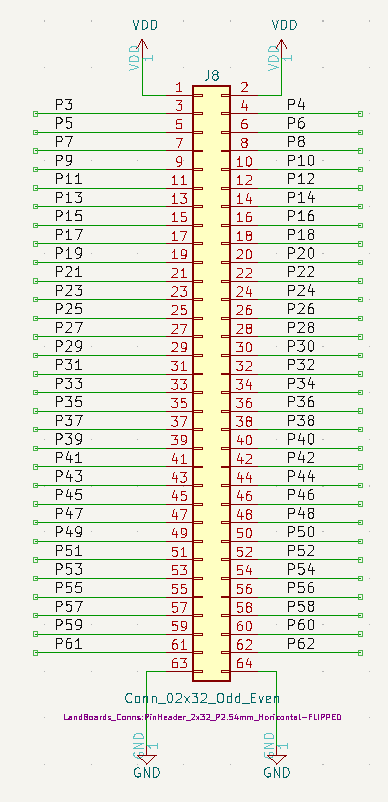

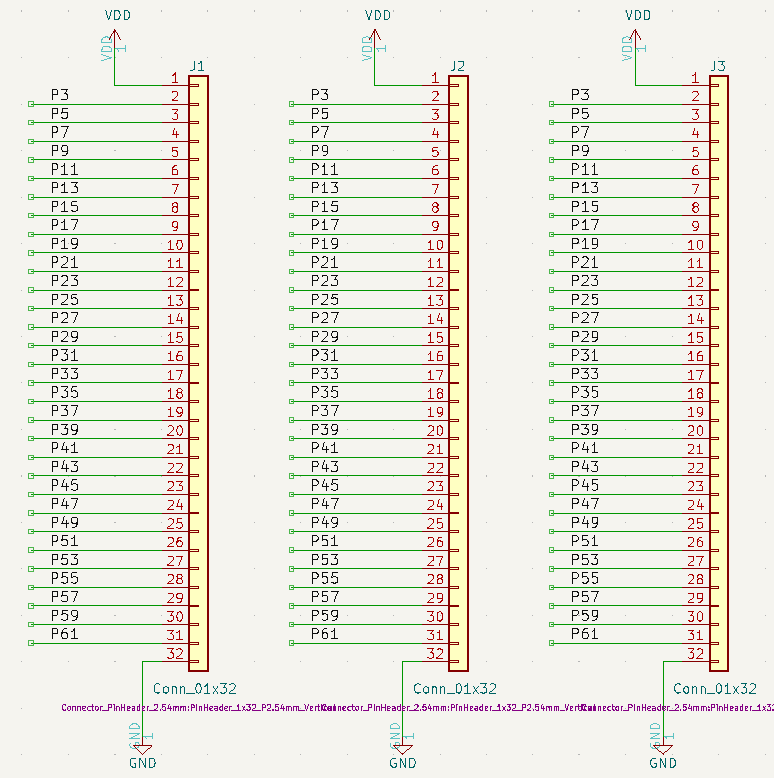

J1-J3 Lower Pins

J5-J7 Upper Pins

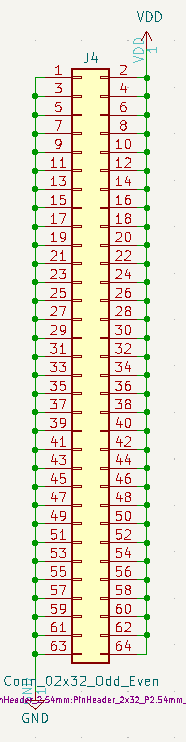

J4 - Conter Power Pins

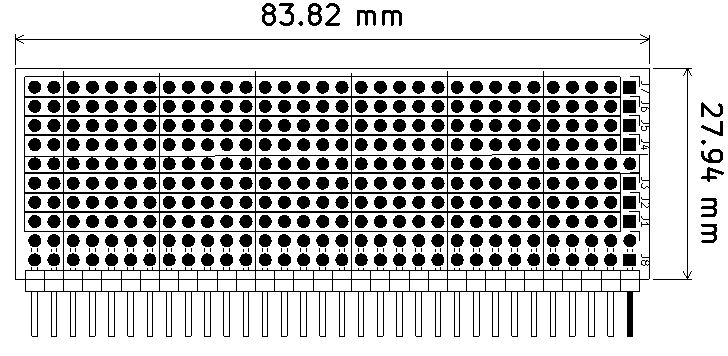

Mechanicals

Checkout

- GND S/B on P39/P40 not P63/P64

- Jumper P39 to ground bus down center

- Jumper P40 to ground bus down center