Difference between revisions of "ODAS-PSOC5"

Jump to navigation

Jump to search

Blwikiadmin (talk | contribs) |

Blwikiadmin (talk | contribs) |

||

| Line 2: | Line 2: | ||

== Features == | == Features == | ||

| + | |||

| + | * PSOC part CY8C5267AXI-LP051 | ||

| + | ** Core: ARM Cortex M3 | ||

| + | ** Data Bus Width: 32 bit | ||

| + | ** Maximum Clock Frequency: 67 MHz | ||

| + | ** Program Memory Size: 128 kB | ||

| + | ** Data RAM Size: 32 kB | ||

| + | ** ADC Resolution: 12 bit | ||

| + | ** Data RAM Type: SRAM | ||

| + | ** Interface Type: I2C, USB | ||

| + | ** Number of ADC Channels: 1 | ||

| + | ** Number of I/Os: 72 I/O | ||

| + | ** Number of Timers/Counters: 4 Timer | ||

| + | ** Program Memory Type: Flash | ||

Revision as of 12:56, 15 March 2022

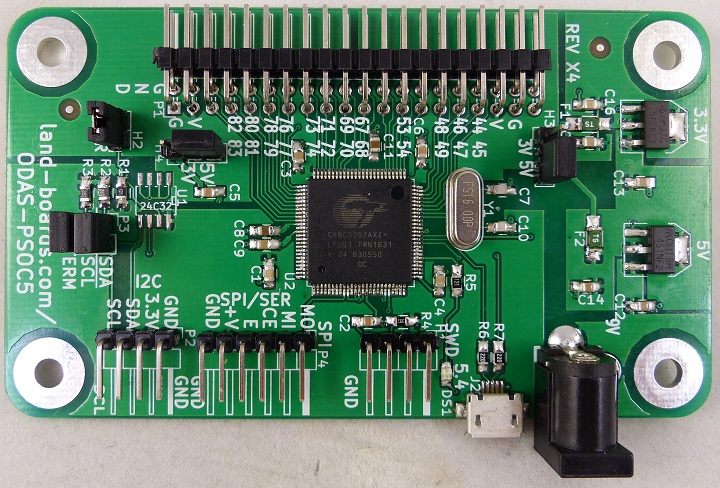

Features

- PSOC part CY8C5267AXI-LP051

- Core: ARM Cortex M3

- Data Bus Width: 32 bit

- Maximum Clock Frequency: 67 MHz

- Program Memory Size: 128 kB

- Data RAM Size: 32 kB

- ADC Resolution: 12 bit

- Data RAM Type: SRAM

- Interface Type: I2C, USB

- Number of ADC Channels: 1

- Number of I/Os: 72 I/O

- Number of Timers/Counters: 4 Timer

- Program Memory Type: Flash