Difference between revisions of "IOP16 Instructions Detail"

Jump to navigation

Jump to search

Blwikiadmin (talk | contribs) |

Blwikiadmin (talk | contribs) |

||

| Line 118: | Line 118: | ||

=== BEZ - Branch if Equal to Zero === | === BEZ - Branch if Equal to Zero === | ||

| − | * If | + | * If Condition Code Zero-bit is set take branch |

=== BNZ - Branch if Not Zero === | === BNZ - Branch if Not Zero === | ||

| − | * If | + | * If Condition Code Zero-bit is not set take branch |

=== BEQ - Branch if Equal === | === BEQ - Branch if Equal === | ||

* Psuedo-Instruction (same as BEZ) | * Psuedo-Instruction (same as BEZ) | ||

| − | * If | + | * If Condition Code Zero-bit bit is set take branch |

=== BNE - Branch if Not Equal === | === BNE - Branch if Not Equal === | ||

* Psuedo-Instruction (Same as BNZ) | * Psuedo-Instruction (Same as BNZ) | ||

| − | * If | + | * If Condition Code Zero-bit bit is clear take branch |

== Misc Instructions == | == Misc Instructions == | ||

Revision as of 15:14, 17 April 2022

Contents

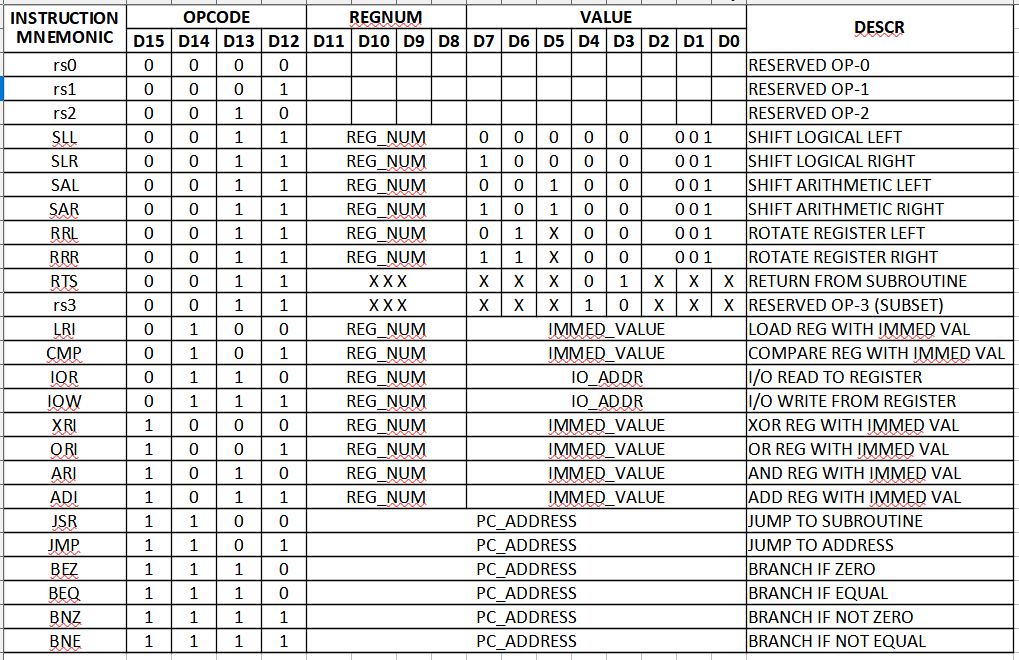

IOP16 Instructions

- Details of the instructions follow

- Some instructions are psuedo-ops which are replaced with equivalent instructions

- Used as convenience

Load Instruction

- Instruction to load register

LRI - Load Register with Immediate Value

- Load a register with an immediate value

Peripheral Load/Store Instructions

- Peripheral read/write instructions

IOR - I/O Read

- Read peripheral address into a register

IOW - I/O Write

- Write value from register to peripheral address

Shift/Rotate Instructions

- Shift/rotate instructions

- Logical/arithmetic operations

- The bottom 3-bits of the instruction have the count

- Count is set to 1

- Barrel shifter could be written to have other counts

- Shift/rotate instruction do not set the Condition Code Z-bit

SLL - Shift Logical Left

- Shift register left by 1

- Shifts in 0 to Least Significant bit

SLR - Shift Logical Right

- Shift register right by 1

- Shifts in 0 to Most Significant bit

SAL - Shift Arithmetic Left

- Shift register left by 1

- Shifts in 0 to Least Significant bit

SAR - Shift Arithmetic Right

- Shift register right by 1

- Shifts in 1 to Most Significant bit

RRL - Rotate Register Left

- Rotate Register left by 1

- Rotate Register MSB into Register Least Significant bit

RRR - Rotate Register Right

- Rotate register right by 1

- Rotate Register LSB into Register Most Significant bit

ALU Instruction

- Logical and Mathematical instructions

- Set Conditional Code Zero-bit

XRI - Exclusive-OR Register with Immediate Value

- Exclusive-OR Register with immediate value

- Store back into register

- Set Conditional Code Zero-bit

ORI - Logical OR Register with Immediate Value

- Logical OR Register with immediate value

- Store back into register

- Set Conditional Code Zero-bit

ARI - Logical AND Register with Immediate Value

- Logical AND Register with immediate value

- Store back into register

- Set Conditional Code Zero-bit

ADI - Add Register with Immediate Value

- Add Register with immediate value

- Store back into register

- Set Conditional Code Zero-bit

CMP - Compare Register with Immediate Value

- Compare register with Immediate value

- Set Conditional Code Zero-bit

Flow Control Instructions

- Various instructions that can alter program flow

- Some are conditional branches, Bxx

RTS - Return from Subroutine

- Pops the program stack to use as a return address

JSR - Jump to Subroutine

- Push next address onto stack

- Jump to address

JMP - Jump

- Jump to address

BEZ - Branch if Equal to Zero

- If Condition Code Zero-bit is set take branch

BNZ - Branch if Not Zero

- If Condition Code Zero-bit is not set take branch

BEQ - Branch if Equal

- Psuedo-Instruction (same as BEZ)

- If Condition Code Zero-bit bit is set take branch

BNE - Branch if Not Equal

- Psuedo-Instruction (Same as BNZ)

- If Condition Code Zero-bit bit is clear take branch

Misc Instructions

NOP - No operation

- Psuedo-Instruction

- Coded as ORI Reg8,0x00

HALT

- Psuedo-Instruction performs branch to self