Difference between revisions of "Front Panel for 8 Bit Computers V2"

Jump to navigation

Jump to search

Blwikiadmin (talk | contribs) |

Blwikiadmin (talk | contribs) |

||

| Line 161: | Line 161: | ||

<pre> | <pre> | ||

| − | 0x0000-0x7FFF - INTERNAL SRAM | + | 0x0000-0x7FFF - 32KB INTERNAL SRAM |

| − | + | 0XEC00-0xEFFF - 1KB INTERNAL SRAM (SCRATCHPAD SRAM USED BY MIKBUG) | |

| − | + | 0xFC18-0xFC19 - VDU (serSelect J3 JUMPER REMOVED) | |

| − | + | 0xFC28-0xFC19 - ACIA | |

| − | + | 0xFC30-0xFC3F - Front Panel | |

| + | 0xF000-0xFFFF - MIKBUG ROM - Copied 4X | ||

</pre> | </pre> | ||

| Line 172: | Line 173: | ||

===== Halt CPU ===== | ===== Halt CPU ===== | ||

| − | * Card comes up running [https://github.com/douggilliland/ | + | * Card comes up running [https://github.com/douggilliland/MultiComp/blob/master/MultiComp%20(VHDL%20Template)/Components/ROMs/MIKBUG_6800/DGG_MIKBUG_60KB.LST SMITHBUG at 0xF000] |

* RUN LED comes up on | * RUN LED comes up on | ||

* A0-A15 LEDs light "dimly" once CPU is running | * A0-A15 LEDs light "dimly" once CPU is running | ||

| Line 183: | Line 184: | ||

* Enter address set mode by pressing SW24 SETADR pushbutton, LED will illuminate | * Enter address set mode by pressing SW24 SETADR pushbutton, LED will illuminate | ||

| − | * Set address to | + | * Set address to 0xF000 by pressing A31, A30, A29, A28 LEDs will light |

* Press SETADR pushbutton again to exit set address mode, LED will go off | * Press SETADR pushbutton again to exit set address mode, LED will go off | ||

* For MIKBUG, data will be 0x8E | * For MIKBUG, data will be 0x8E | ||

* Press INCADR SW26 | * Press INCADR SW26 | ||

| − | * Address will increment to | + | * Address will increment to 0F001 |

* Data will show 0x7F | * Data will show 0x7F | ||

* Next INCADR values are as follows | * Next INCADR values are as follows | ||

<pre> | <pre> | ||

| − | + | f000 8e ef 44 LDS #STACK | |

| − | + | f003 bf ef 0a STS SP | |

| − | + | f006 7f ef 0d CLR ECHO ; DGG - default to serial port echo on | |

| − | + | f009 ce f1 25 LDX #SFE ; DGG - VECTORED SWI ROUTINE | |

| − | + | f00c ff ef 17 STX SWIPTR | |

| − | + | f00f ff ef 08 STX NIO | |

| − | |||

</pre> | </pre> | ||

Revision as of 14:18, 21 April 2022

Contents

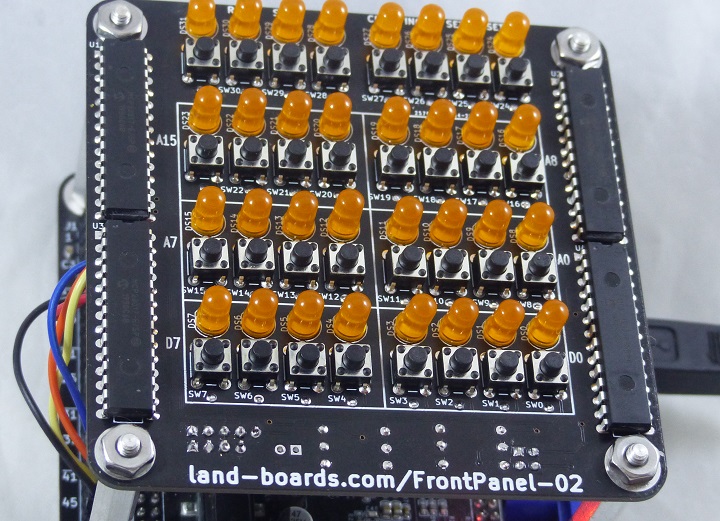

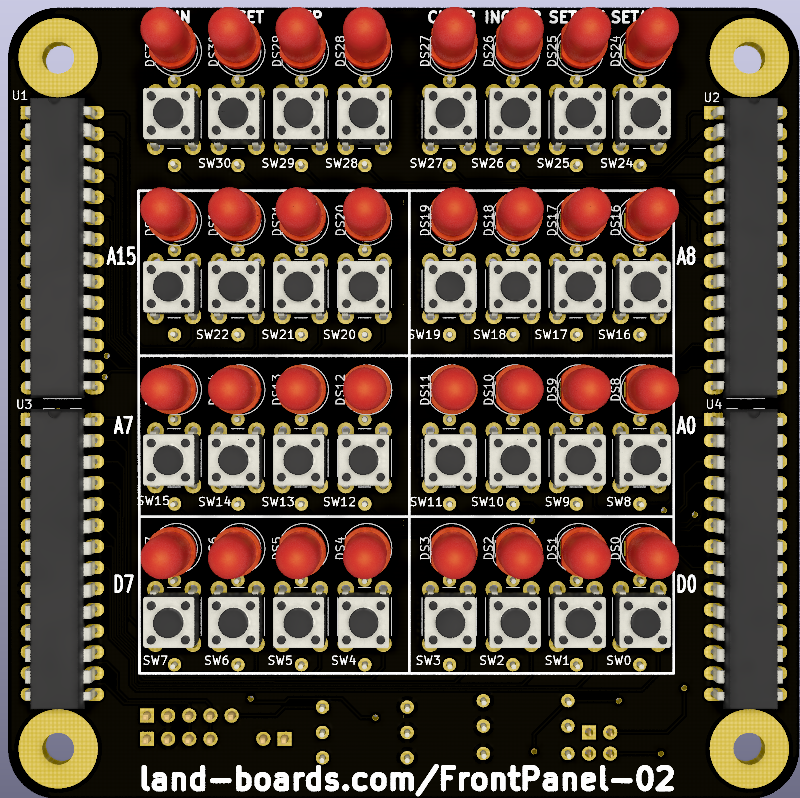

Front Panel for 8-Bit Microprocessors v2

See here for Ver 1 - SMT version

Features

This is a through-hole version of Front Panel for 8_Bit Computers.

It has these features. They may not fit your generic design. Especially since this card has to have an I2C interface.

- 32 Pushbutton Switches

- 32 LEDs

- I2C interface (Two Wire interface - plus power and ground)

- Jumper selectable base address

- Occupies I2C addresses either 0x20-0x23 or 0x24-0x27

- Jumper Selectable I2C terminators

- I2C daisy-chain connector

- Interrupt line

- Can be configured to interrupt on button presses

- MCP23017 need to be set to Open-Drain output - card has pull-up to Vcc

- Interrupt line

- 4 of MCP23017 16-bit I2C Port Expanders

- These are fine pitch surface mount parts

- 3.3V or 5V operation

- Compatible form factor with RETRO-EP4CE15 and other cards

- 95x95mm

- 6-32 mounting holes

Connector

J2 - I2C Connector

- Two row header on bottom of card

- 5 pin in

- 4 pin out (daisy-chain)

- GND

- VCC

- SDA

- SCL

- INT*

And

- GND

- VCC

- SDA

- SCL

Schematic

Legends

- D0-D7 - Data bus

- A0-A15 - Address bus

- Controls

Top row controls

Board has typical control silkscreen markings. It is all through hole so that it is much easier to assemble.

- RUN - Run/Halt pushbutton, RUN LED on for CPU running

- RESET - Reset the CPU

- STEP - Single Step the CPU

- Undefined

- CLEAR - Clear address bus (if SETADR is ON) or data bus lines (if SETDAT is ON)

- INCADR - Increment the address

- If SETDAT is on write data

- SETDAT - Set the data value

- SETADR - Set the address

Drivers

VHDL Driver

- VHDL code to control Front Panel autonomously - Great for FPGA Retro-computers

- Converts pushbuttons into raw, debounced, and toggled outputs

- Example: 6800 running MIKBUG using the Front Panel - Run/Halt the CPU, Read SRAM, ROM, etc, Write to SRAM

- IOP Code - Controls the Front Panel

VHDL Entities

- Panel Entity

-- ------------------------------------------------------------------------------------------------------- -- Front Panel starts here -- Pass IOP16 code size and stack size down to the Front Panel fp01 : work.FrontPanel01 generic map ( INST_ROM_SIZE_IN => 512, -- 512W code size STACK_DEPTH_IN => 4 -- 16 deep stack size ) port map ( -- Clock and reset i_CLOCK_50 => i_CLOCK_50, -- Clock (50 MHz) i_n_reset => i_n_reset, -- Reset (from FGPGA KEY) -- 32 outs, 32 ins i_FPLEDs => w_LEDsOut, -- Out to LEDs (32) o_PBRaw => w_PBsRaw, -- Raw version of the Pushbuttons (32) o_PBLatched => w_PBLatched, -- Latched version of the Pushbuttons (32) o_PBToggled => w_PBsToggled, -- Toggle version of the Pushbuttons (32) -- I2C interface io_I2C_SCL => io_I2C_SCL, -- I2C clock to Front Panel card io_I2C_SDA => io_I2C_SDA, -- I2C data to/from Front Panel card i_I2C_INTn => i_I2C_INTn -- Interrupt input - active low ); -- Front Panel ends here -- -------------------------------------------------------------------------------------------------------

- Higher level entity

- 6800 with front Panel application

-- Front Panel MIKBUG_FRPNL : entity work.MIKBUG_FRPNL port map ( -- Clock and reset i_CLOCK_50 => i_CLOCK_50, i_cpuClock => w_cpuClock, i_n_reset => w_resetLow, o_FPReset => w_FPReset, -- CPU intercepts -- Front Panel loops back signals when in Front Panel switch is in Run Mode i_CPUAddress => w_cpuAddressB, o_CPUAddress => w_cpuAddress, i_cpuData => w_cpuDataOutB, o_cpuData => w_cpuDataOut, i_CPURdData => w_cpuDataIn, io_run0Halt1 => w_run0Halt1, o_wrRamStr => w_wrRamStr, i_R1W0 => w_R1W0B, o_R1W0 => w_R1W0, -- External I2C connections io_I2C_SCL => io_I2C_SCL, io_I2C_SDA => io_I2C_SDA, i_I2C_INTn => i_I2C_INTn );

6800 with Front Panel Operation

- Memory map for this configuration is

0x0000-0x7FFF - 32KB INTERNAL SRAM 0XEC00-0xEFFF - 1KB INTERNAL SRAM (SCRATCHPAD SRAM USED BY MIKBUG) 0xFC18-0xFC19 - VDU (serSelect J3 JUMPER REMOVED) 0xFC28-0xFC19 - ACIA 0xFC30-0xFC3F - Front Panel 0xF000-0xFFFF - MIKBUG ROM - Copied 4X

Halt CPU

- Card comes up running SMITHBUG at 0xF000

- RUN LED comes up on

- A0-A15 LEDs light "dimly" once CPU is running

- Other control LEDs off

- Press RUN SW32 to halt CPU, LED will go off

- A0-A31, D0-D7 LEDs may be off if run first time

- May come up at address 0x0000 and show value in SRAM at that address (0x00 at power on)

Read from Program ROM

- Enter address set mode by pressing SW24 SETADR pushbutton, LED will illuminate

- Set address to 0xF000 by pressing A31, A30, A29, A28 LEDs will light

- Press SETADR pushbutton again to exit set address mode, LED will go off

- For MIKBUG, data will be 0x8E

- Press INCADR SW26

- Address will increment to 0F001

- Data will show 0x7F

- Next INCADR values are as follows

f000 8e ef 44 LDS #STACK f003 bf ef 0a STS SP f006 7f ef 0d CLR ECHO ; DGG - default to serial port echo on f009 ce f1 25 LDX #SFE ; DGG - VECTORED SWI ROUTINE f00c ff ef 17 STX SWIPTR f00f ff ef 08 STX NIO

Access SRAM

- Enter address set mode by pressing SW24 SETADR pushbutton, LED will illuminate

- Set address to 0x0000

- Press SETADR pushbutton again to exit set address mode, LED will go off

- Press INCADR pushbutton to read data

- Press SETDAT pushbutton to enter write data mode

- Set the data value to write to SRAM on pushbuttons

- Press INCADR to do the write and advance the address

- Press SETDAT pushbutton again to exit write data mode

- Verify data as above

Arduino Driver

- I2C parts are standard MCP23017 drivers which are supported in Arduino and most microprocessors

Micro-Python

PSoC Control

- Z80 example