Difference between revisions of "LB-6809-01"

Jump to navigation

Jump to search

Blwikiadmin (talk | contribs) |

Blwikiadmin (talk | contribs) |

||

| Line 8: | Line 8: | ||

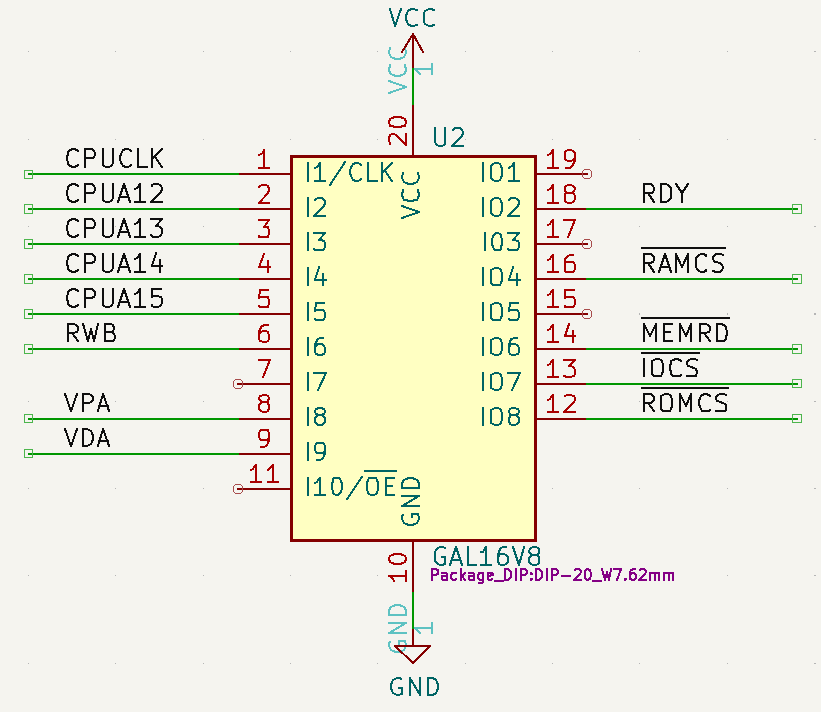

* Address decoder PLD drives RAM/ROM/IO chip selects | * Address decoder PLD drives RAM/ROM/IO chip selects | ||

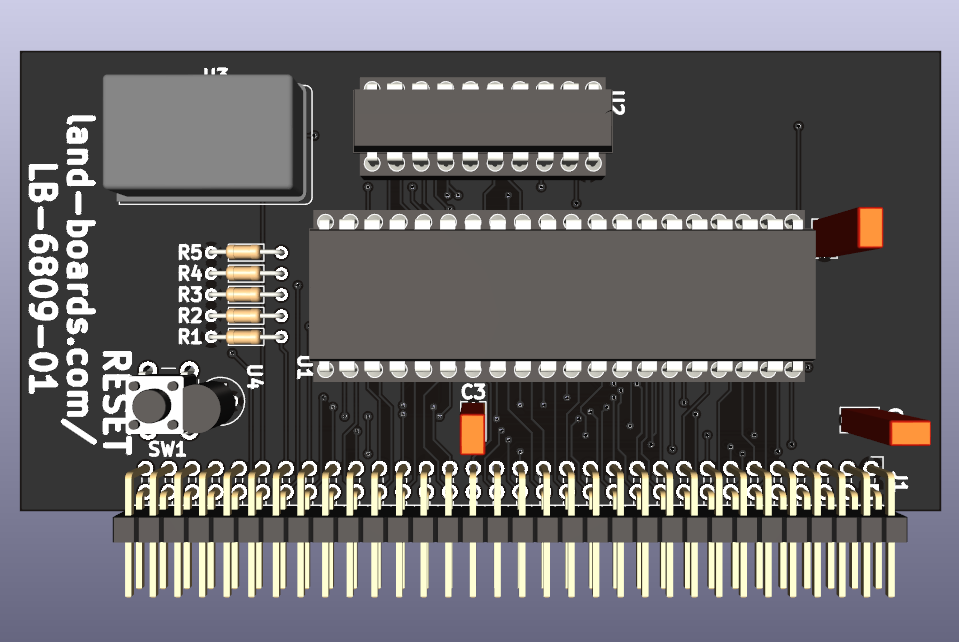

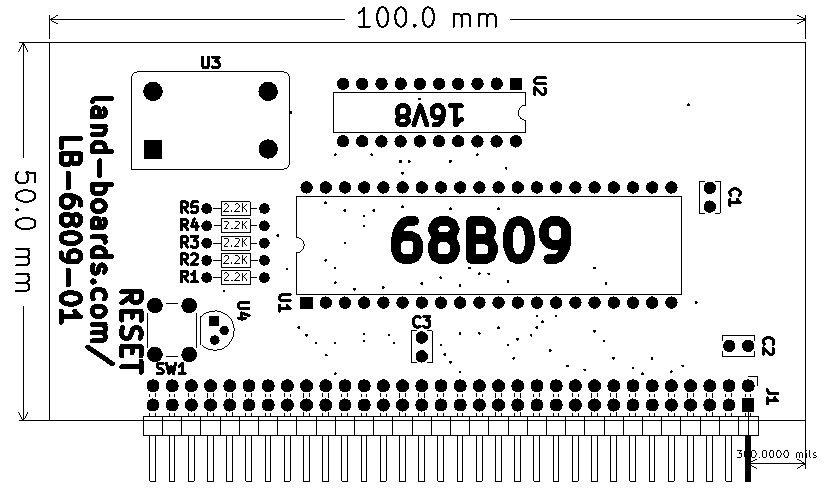

* 100x50mm card | * 100x50mm card | ||

| + | |||

| + | === Memory Map === | ||

== Design == | == Design == | ||

Revision as of 11:26, 19 August 2024

Contents

Features

- 68B09 CPU

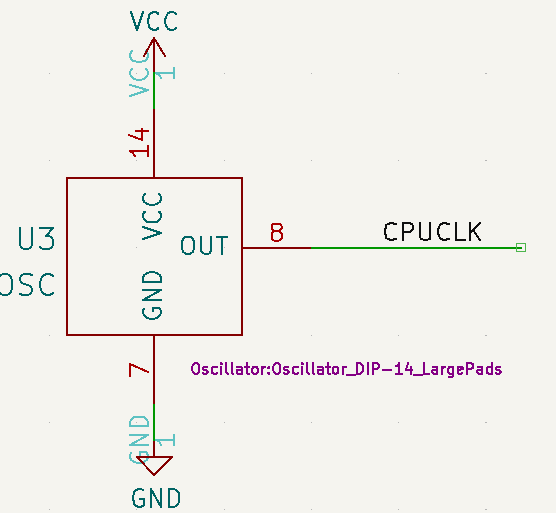

- 2 MHz (typical) Oscillator on card

- Reset switch/power monitor

- Address decoder PLD drives RAM/ROM/IO chip selects

- 100x50mm card

Memory Map

Design

68B09 CPU

Oscillator

PLD

PLD Listing

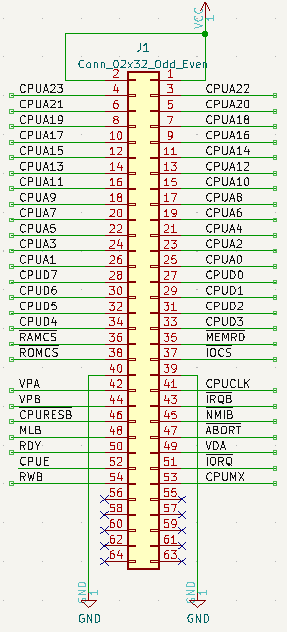

Backplane connector

Mechanicals

Checkout

Rev 1 Checkout Notes

- Add wire U1-34 to U2-7 (E)