Difference between revisions of "QTPy49"

Jump to navigation

Jump to search

Blwikiadmin (talk | contribs) |

Blwikiadmin (talk | contribs) |

||

| Line 9: | Line 9: | ||

** [https://www.seeedstudio.com/XIAO-RP2040-v1-0-p-5026.html Seeed XIAO RP2040] | ** [https://www.seeedstudio.com/XIAO-RP2040-v1-0-p-5026.html Seeed XIAO RP2040] | ||

* Socketed CPU | * Socketed CPU | ||

| − | * | + | * Headers |

** DC Power | ** DC Power | ||

** AD0-AD3 GVS | ** AD0-AD3 GVS | ||

Revision as of 15:11, 4 June 2022

Contents

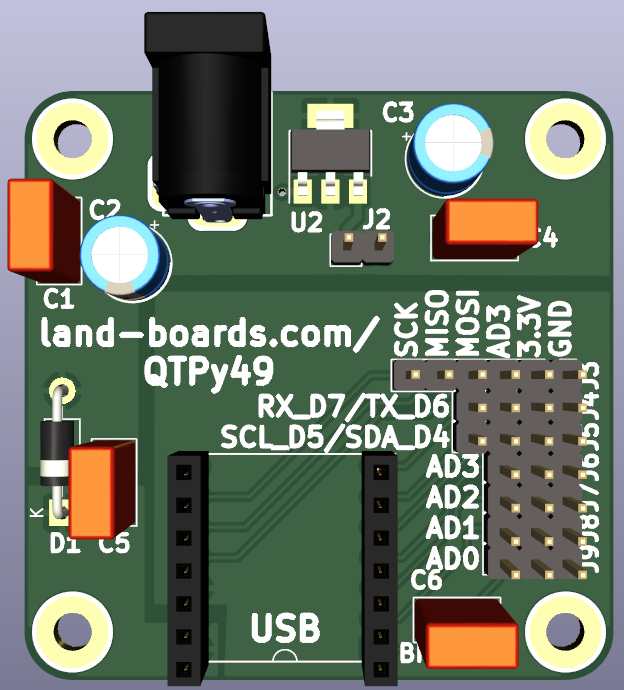

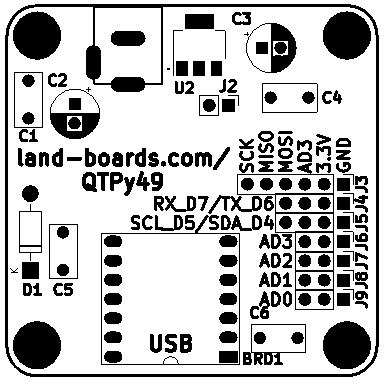

Features

- CPU choices are

- Socketed CPU

- Headers

- DC Power

- AD0-AD3 GVS

- I2C

- TX/RX

- SPi

- Power input

- 7-12V

- 5V

- 49x49mm ODAS form factor

- (4) 4-40 mounting holes

Connectors

- Ground, Voltage, Signal (GVS) connections

J1 - DC In

- 7-12V

- Center positive

J2 - Short Regulator

- Install if J1 has 5V

- No need to install U2 regulator

J3 - SPI

- GND

- 3.3V

- SS, AD3

- MOSI, S10

- MISO, D9

- SCK, D8

J4 - UART

- GND

- 3.3V

- TX, D6

- RX, D7

J5 - I2C

- GND

- 3.3V

- D4, SDA

- D5, SCL

J6 - AD3

- Digital I/O 3

- Analog In 3

- PWM output

- Capacitive touch input

- Pinout

- GND

- 3.3V

- AD3

J7 - AD2

- Digital I/O 2

- Analog In 2

- PWM

- Capacitive touch input

- Pinout

- GND

- 3.3V

- AD2

J8 - AD1

- Digital I/O 1

- Analog In 1

- Capacitive touch input

- AREF pin

- Pinout

- GND

- 3.3V

- AD1

J9 - AD0

- Digital I/O 0

- Analog In 0

- True analog output with 10 bit precision

- Does not have PWM

- Capacitive touch input

- Pinout

- GND

- 3.3V

- AD0

Mechanicals