IOP16 16-bit I/O CPU Design

Jump to navigation

Jump to search

Contents

Overview

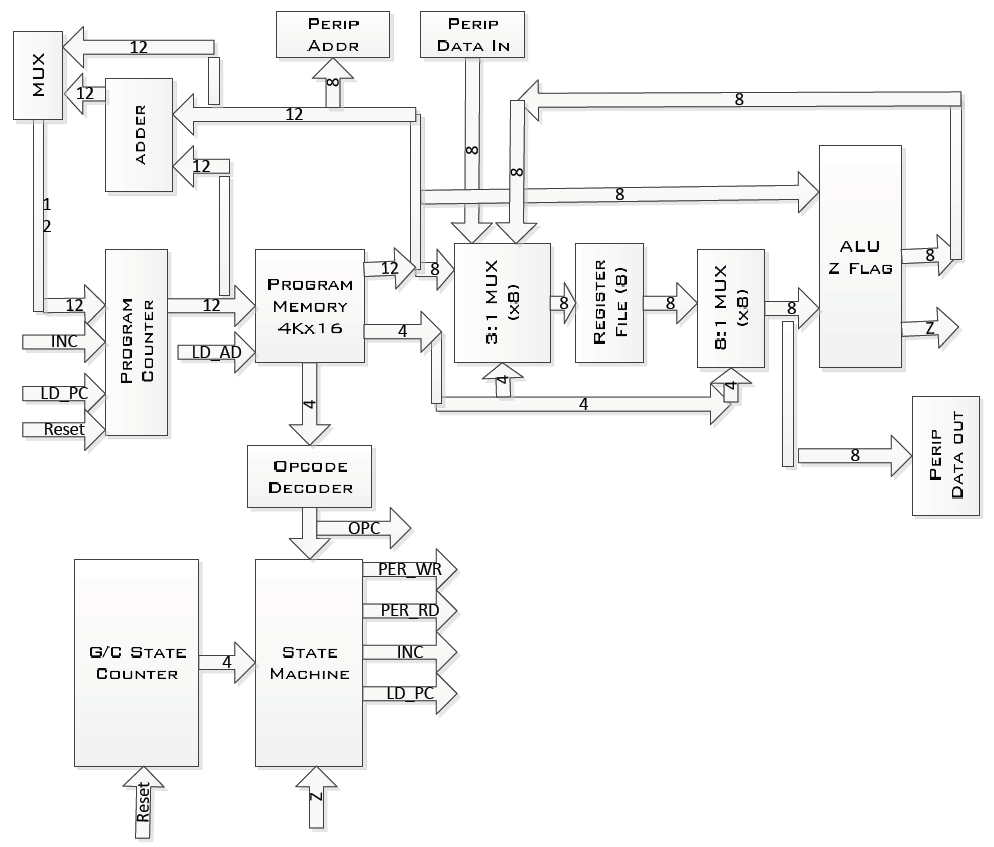

This CPU is intended to be used as an I/O Processor. The CPU can be used as a Microcontroller replacement in many applications. It can be embedded into an FPGA with a separate Host Computer off-loading tedious I/O programming. It is useful for offloading polled I/O or replacing CPUs in small applications. The majority of these applications deal with 8-bit data and that's where this CPU excels.

Features Set

- 16-bit CPU

- Simple/consistent opcode bit fields

- Instructions are always 16-bits wide

- 4-bit opcode

- Some "sub-instructions" allow more than 16 instructions

- 4-bit register field (shared with address/offset)

- 8-bit constant (shared with address/offset)

- High enough IOP-16 Performance - 12.5 MIPS

- 4 of 50 MHz FPGA clocks

- Register File

- 4, 8, or 13 General Purpose registers

- 3 constant value registers

- Registers are 8-bits

- 12-bit of Program address (up to 4K instructions)

- IOP-16 Stack

- 0 (none)

- 1 deep

- Optionally deeper as build option (uses SRAM)

IOP16 Block Diagram

Instruction Set

Assembler

- Table driven Assembler

- Input comes from a CSV file

- Outputs .MIF and Listing files

- MIF (Memory Initialization File) is Altera ROM initialization File

Hardware Requirements

- Targeted at an FPGA implementation

- The CPU could easily be run on pretty much any FPGA

- Coded in VHDL

Resources

- Very small LUT/Memory footprint in FPGA

- Uses 271 logic cells in an Altera EP4 FPGA

- Uses 76 registers in an Altera EP4 FPGA

- Requires a minimum 1 of 1K SRAM blocks (depends on program size)

- Trade-off - SRAM could be replaced with logic cells (in theory)

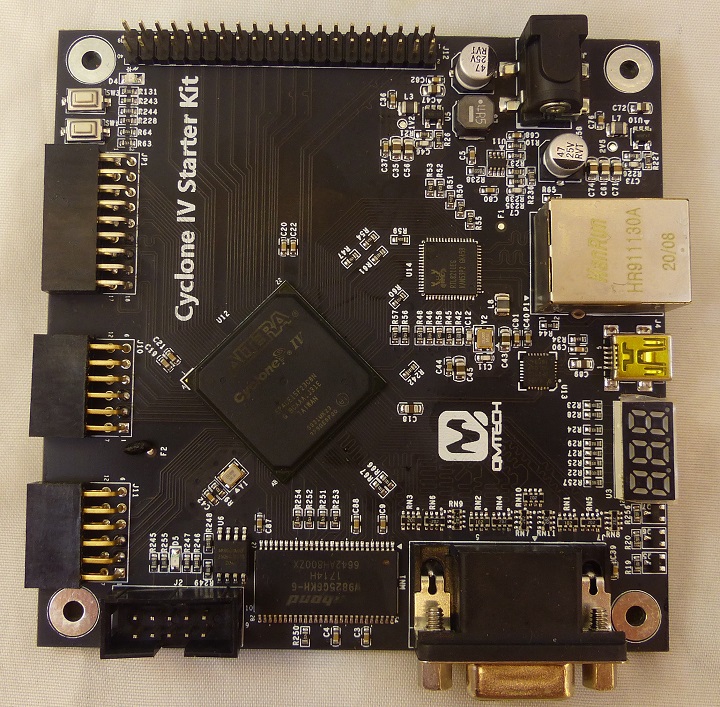

Target Hardware

- The initial targeted hardware is the QMTECH EP4CE15 FPGA Starter Kit card

- This FPGA is inexpensive and powerful

- The CPU takes up very little of the resources of the FPGA

- QMTECH CYCLONE IV STARTER KIT GitHub

- QMTECH FPGA Files Reflector

- QMTECH EP4CE15 FPGA card - AliExpress page

Build on Cyclone 10 FPGA

Build into MultiComp in a Box

Peripheral Support

- Extensive Peripheral Support

- 8-bit address (controls up to 256 peripherals)

- 8-bit data

- Read strobe (a couple of clocks wide)

- Write strobe (a couple of clocks wide)

Code Examples

Here are some Code and FPGA build example applications

- Design a CPU Base Code - GitHub

Blink LED

Almost minimal design = CPU + Timer + LED