Difference between revisions of "PDP-8 Front Panel"

Jump to navigation

Jump to search

Blwikiadmin (talk | contribs) |

Blwikiadmin (talk | contribs) |

||

| (52 intermediate revisions by the same user not shown) | |||

| Line 1: | Line 1: | ||

| − | [[File:PDP- | + | [[File:tindie-mediums.png|link=https://www.tindie.com/products/23753/]] |

| + | |||

| + | [[File:PDP-8_P17546_cropped_720px.jpg]] | ||

| + | |||

| + | <video type="youtube">1-lU59broa4</video> | ||

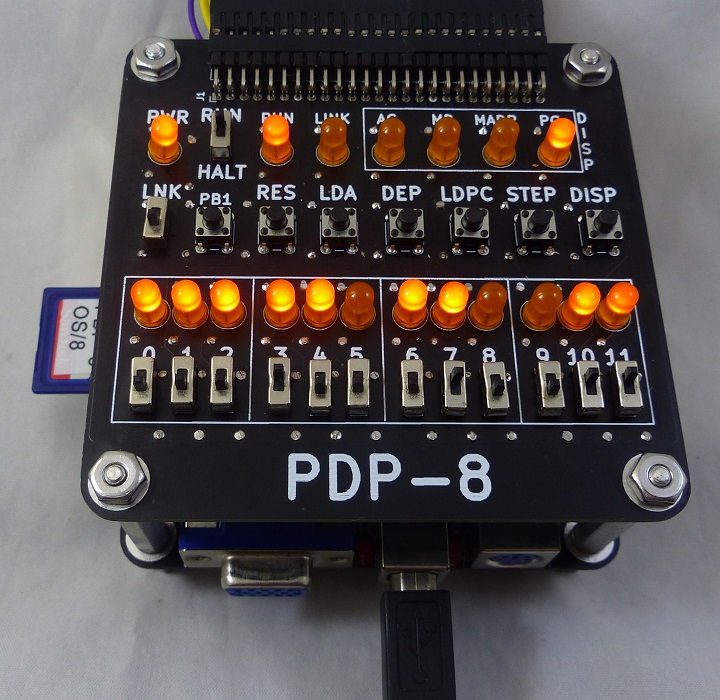

== Features == | == Features == | ||

| − | * 50 pin connector | + | * 50-pin connector |

| − | ** 2x25 Pinout matches [[RETRO-EP4CE15]] Card pins | + | ** 2x25 Pinout matches [[RETRO-EP4CE15]] Card pins (1:1 cable) |

| − | * 12 Value LEDs ( | + | ** Some unused pins - wired to +3.3V/GND for connecting other cards |

| − | ** | + | * 12 Value LEDs (DB-11) - silkscreen marked in octal format |

| + | * DISP pushbutton - Selects what is on the 12 Value LEDs | ||

| + | ** I like diffused orange color the best for LEDs - looks retro | ||

| + | ** Pushing DISP cycles between LEDs displaying PC, Memory Address, Memory Data, Accumulator | ||

* 12 Load Value Slide Switches (SL0-11) - octal format | * 12 Load Value Slide Switches (SL0-11) - octal format | ||

| − | ** Enter values: PC | + | ** Enter values: Program Counter (PC), Memory Address, Memory Data, Accumulator |

| − | |||

| − | |||

| − | |||

* Pushbutton Switches | * Pushbutton Switches | ||

** STEP pushbutton - Increment PC | ** STEP pushbutton - Increment PC | ||

| − | ** LDPC pushbutton - | + | ** LDPC pushbutton - Store value from Value Slide Switches to Program Counter (PC) |

** DEP pushbutton - Store value from Value Slide Switches to memory | ** DEP pushbutton - Store value from Value Slide Switches to memory | ||

** LDA pushbutton - Store value from Value Slide Switches to Accumulator | ** LDA pushbutton - Store value from Value Slide Switches to Accumulator | ||

** RES - Reset pushbutton - Resets CPU | ** RES - Reset pushbutton - Resets CPU | ||

** PB1 - spare pushbutton | ** PB1 - spare pushbutton | ||

| − | * 4 DISP LEDs - Cycle between 12 LEDs source with DISP pushbutton | + | * 4 DISP LEDs - Indicates what is being shown on the 12 LEDs |

| + | ** Cycle between 12 LEDs source with DISP pushbutton | ||

** PC - 12 LEDs display Program Counter value | ** PC - 12 LEDs display Program Counter value | ||

** MADR - 12 LEDs display Memory Address value | ** MADR - 12 LEDs display Memory Address value | ||

** MD - 12 LEDs display Memory Data value | ** MD - 12 LEDs display Memory Data value | ||

** AC - 12 LEDs display Accumulator value | ** AC - 12 LEDs display Accumulator value | ||

| + | * LNK - Link value slide switch | ||

* LINK LED - Displays Link value | * LINK LED - Displays Link value | ||

* RUN LED - Running program | * RUN LED - Running program | ||

* RUN/HALT slide switch | * RUN/HALT slide switch | ||

* PWR - Power LED | * PWR - Power LED | ||

| − | * 95x95mm form factor | + | * 95x95mm form factor matches [[RETRO-EP4CE15]] |

* (4) 6-32 mounting holes | * (4) 6-32 mounting holes | ||

| + | ** Boards can be stacked with standoffs | ||

| − | == PDP-8 FPGA | + | == PDP-8 FPGA Designs == |

| − | * [https://www.amazon.com/PDP-8-Class-Project-Resoling-Machine | + | * Two working designs |

| + | ** Tom Almy's PDP-8 | ||

| + | ** OpenCores PDP-8 FPGA designs | ||

| + | |||

| + | === Build of Tom Almy's PDP-8 FPGA (Working 2021-May) === | ||

| + | |||

| + | Build is based on [https://almy.us/ Tom Almy]'s book [https://www.amazon.com/PDP-8-Class-Project-Resoling-Machine/dp/1790487978/ref=sr_1_1?dchild=1&keywords=tom+almy+pdp-8&qid=1619874138&sr=8-1 The PDP-8 Class Project: Resoling An Old Machine]. | ||

| + | |||

| + | * [https://hackaday.io/project/179357-pdp-8-fpga Hackaday page with progress logs] | ||

* [https://github.com/douggilliland/Retro-Computers/tree/master/PDP-8/PDP8_Book(Almy) PDP-8 PFGA Design] - GitHub repo | * [https://github.com/douggilliland/Retro-Computers/tree/master/PDP-8/PDP8_Book(Almy) PDP-8 PFGA Design] - GitHub repo | ||

| − | ** [https://github.com/douggilliland/Retro-Computers/tree/master/PDP-8/PDP8_Book(Almy)/PDP8_VDU_FrPnl PDP-8 with Front Panel and VDU] | + | * [https://github.com/douggilliland/Linux-68k/tree/master/pdp8 My PDP-8 Software GitHub repository] |

| + | * [https://github.com/douggilliland/Retro-Computers/tree/master/PDP-8/PDP8_Book(Almy)/PDP8_VDU_FrPnl PDP-8 with Front Panel and VDU] | ||

| + | |||

| + | ==== Hardware used ==== | ||

| + | |||

| + | * [http://land-boards.com/blwiki/index.php?title=RETRO-EP4CE15 RETRO-EP4CE15] - FPGA Hardware used | ||

| + | * [http://land-boards.com/blwiki/index.php?title=QMTECH_EP4CE15_FPGA_Card QMTECH EP4CE15 FPGA Card] | ||

| + | * [http://land-boards.com/blwiki/index.php?title=PDP-8_Front_Panel PDP-8 Front Panel] | ||

| + | |||

| + | ==== FPGA Resources ==== | ||

| + | |||

| + | * Front Panel | ||

| + | * Cyclone IV | ||

| + | |||

| + | <pre> | ||

| + | +----------------------------------------------------------------------------------+ | ||

| + | ; Fitter Summary ; | ||

| + | +------------------------------------+---------------------------------------------+ | ||

| + | ; Fitter Status ; Successful - Sat Apr 30 20:28:20 2022 ; | ||

| + | ; Quartus Prime Version ; 21.1.0 Build 842 10/21/2021 SJ Lite Edition ; | ||

| + | ; Revision Name ; pdp8 ; | ||

| + | ; Top-level Entity Name ; pdp8 ; | ||

| + | ; Family ; Cyclone IV E ; | ||

| + | ; Device ; EP4CE15F23C8 ; | ||

| + | ; Timing Models ; Final ; | ||

| + | ; Total logic elements ; 2,390 / 15,408 ( 16 % ) ; | ||

| + | ; Total combinational functions ; 2,300 / 15,408 ( 15 % ) ; | ||

| + | ; Dedicated logic registers ; 734 / 15,408 ( 5 % ) ; | ||

| + | ; Total registers ; 734 ; | ||

| + | ; Total pins ; 51 / 344 ( 15 % ) ; | ||

| + | ; Total virtual pins ; 0 ; | ||

| + | ; Total memory bits ; 98,304 / 516,096 ( 19 % ) ; | ||

| + | ; Embedded Multiplier 9-bit elements ; 2 / 112 ( 2 % ) ; | ||

| + | ; Total PLLs ; 0 / 4 ( 0 % ) ; | ||

| + | +------------------------------------+---------------------------------------------+ | ||

| + | </pre> | ||

| + | |||

| + | === OpenCores PDP-8 Build === | ||

| + | |||

| + | * [https://hackaday.io/project/180081-opencores-pdp-8-on-fpga Hackaday page with progress logs] | ||

| + | * Wider features than Tom Almy's design | ||

| + | * Supports 32 K words of memory | ||

| + | * SD card support | ||

| + | * Boot OS/8 | ||

| + | * [https://github.com/douggilliland/Retro-Computers/tree/master/PDP-8/PDP8_OpenCores Land Board OpenCores PDP-8 Builds] - GitHub repository | ||

| + | * Two tested/working builds | ||

| + | ** Built in ANSI Terminal build | ||

| + | ** Serial I/O build | ||

| + | |||

| + | ==== RETRO-EP4CE15_CYCLONE_IV_VDU PDP-8 Build ==== | ||

| + | |||

| + | * [https://github.com/douggilliland/Retro-Computers/tree/master/PDP-8/PDP8_OpenCores/RETRO-EP4CE15_CYCLONE_IV_VDU RETRO-EP4CE15_CYCLONE_IV_VDU PDP-8 Build] | ||

| + | * Built in ANSI Terminal with cpu_001 (IOP16B built-in) - Latest build | ||

| + | * [https://github.com/douggilliland/Retro-Computers/tree/master/PDP-8/PDP8_OpenCores/RETRO-EP4CE15_CYCLONE_IV_VDU/ANSITerm/Assy_Code VDU IOP assembly code] | ||

| + | * [https://hackaday.io/project/180415-ansi-terminal-in-an-fpga Hackaday project page for ANSI Terminal] | ||

| + | |||

| + | ==== RETRO-EP4CE15_CYCLONE_IV PDP-8 Build ==== | ||

| + | |||

| + | * [https://github.com/douggilliland/Retro-Computers/tree/master/PDP-8/PDP8_OpenCores/RETRO-EP4CE15_CYCLONE_IV RETRO-EP4CE15_CYCLONE_IV] | ||

| + | * Serial only (no VDU) | ||

| + | |||

| + | ==== RETRO-EP4CE15_CYCLONE_V PDP-8 Build ==== | ||

| + | |||

| + | * [https://github.com/douggilliland/Retro-Computers/tree/master/PDP-8/PDP8_OpenCores/RETRO-EP4CE15_CYCLONE_V RETRO-EP4CE15_CYCLONE_V] | ||

| + | * WIP - missing pin assignment | ||

| + | |||

| + | ==== Hardware used ==== | ||

| + | |||

| + | * [http://land-boards.com/blwiki/index.php?title=RETRO-EP4CE15 RETRO-EP4CE15] - FPGA Hardware used | ||

| + | * [http://land-boards.com/blwiki/index.php?title=QMTECH_EP4CE15_FPGA_Card QMTECH EP4CE15 FPGA Card] | ||

| + | * [http://land-boards.com/blwiki/index.php?title=PDP-8_Front_Panel PDP-8 Front Panel] | ||

| + | |||

| + | ==== FPGA Resources ==== | ||

| + | |||

| + | * ANSI Terminal (IOP-16) | ||

| + | * Cyclone IV | ||

| + | |||

| + | <pre> | ||

| + | +----------------------------------------------------------------------------------+ | ||

| + | ; Fitter Summary ; | ||

| + | +------------------------------------+---------------------------------------------+ | ||

| + | ; Fitter Status ; Successful - Sat Apr 9 19:53:05 2022 ; | ||

| + | ; Quartus Prime Version ; 21.1.0 Build 842 10/21/2021 SJ Lite Edition ; | ||

| + | ; Revision Name ; pdp8_top ; | ||

| + | ; Top-level Entity Name ; pdp8_top ; | ||

| + | ; Family ; Cyclone IV E ; | ||

| + | ; Device ; EP4CE15F23C8 ; | ||

| + | ; Timing Models ; Final ; | ||

| + | ; Total logic elements ; 5,273 / 15,408 ( 34 % ) ; | ||

| + | ; Total combinational functions ; 5,023 / 15,408 ( 33 % ) ; | ||

| + | ; Dedicated logic registers ; 1,569 / 15,408 ( 10 % ) ; | ||

| + | ; Total registers ; 1569 ; | ||

| + | ; Total pins ; 128 / 344 ( 37 % ) ; | ||

| + | ; Total virtual pins ; 0 ; | ||

| + | ; Total memory bits ; 426,112 / 516,096 ( 83 % ) ; | ||

| + | ; Embedded Multiplier 9-bit elements ; 2 / 112 ( 2 % ) ; | ||

| + | ; Total PLLs ; 0 / 4 ( 0 % ) ; | ||

| + | +------------------------------------+---------------------------------------------+ | ||

| + | </pre> | ||

| + | |||

| + | ==== opencores PDP-8 Processor Reference ==== | ||

| + | |||

| + | * [http://opencores.org/project,pdp8 opencores PDP-8 Processor Core and System Overview] | ||

| + | * [https://opencores.org/projects/pdp8/quick%20start Quickstart page] | ||

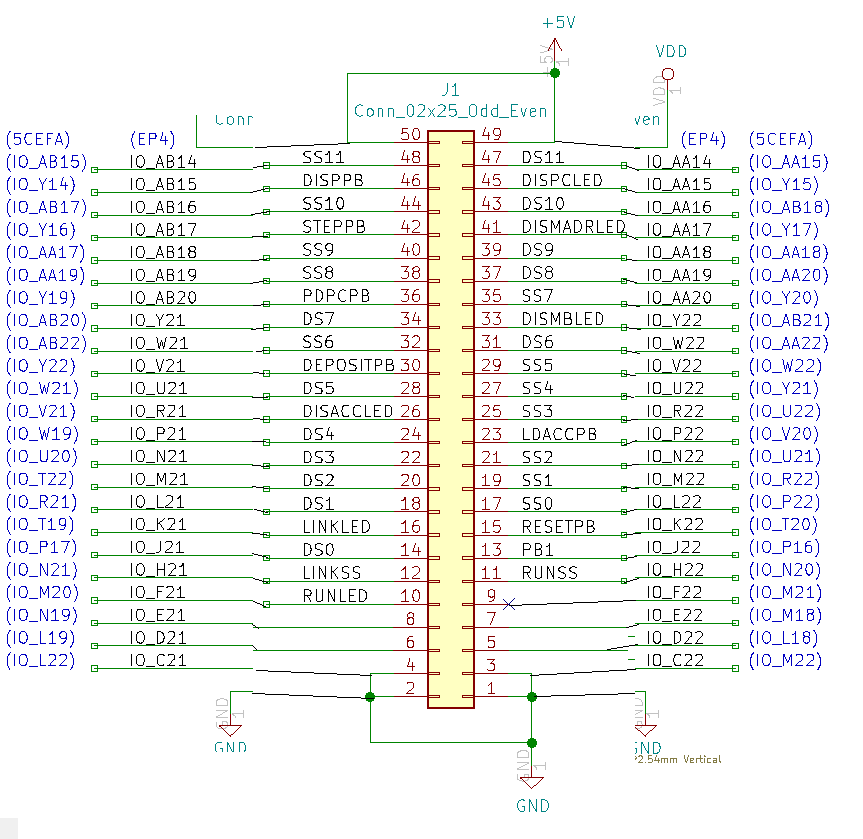

== J1 Connector == | == J1 Connector == | ||

| Line 52: | Line 170: | ||

[[File:PDP-8F_FrontPanel_720px.jpg]] | [[File:PDP-8F_FrontPanel_720px.jpg]] | ||

| − | == Pin List == | + | == Pin List for Tom Almy FPGA Build== |

| + | * For [https://github.com/douggilliland/Retro-Computers/tree/master/PDP-8/PDP8_Book(Almy)/PDP8_VDU_FrPnl Tom Almy's PDP-8 FPGA Code] | ||

<pre> | <pre> | ||

set_global_assignment -name FAMILY "Cyclone IV E" | set_global_assignment -name FAMILY "Cyclone IV E" | ||

| Line 129: | Line 248: | ||

# Status/Operation LEDs | # Status/Operation LEDs | ||

set_location_assignment PIN_K21 -to linkLED | set_location_assignment PIN_K21 -to linkLED | ||

| − | set_location_assignment | + | set_location_assignment PIN_Y22 -to dispMDLED |

| − | set_location_assignment | + | set_location_assignment PIN_AA17 -to dispMALED |

set_location_assignment PIN_AA15 -to dispPCLED | set_location_assignment PIN_AA15 -to dispPCLED | ||

set_location_assignment PIN_R21 -to dispACLED | set_location_assignment PIN_R21 -to dispACLED | ||

| Line 140: | Line 259: | ||

set_location_assignment PIN_P22 -to ldACPB | set_location_assignment PIN_P22 -to ldACPB | ||

set_location_assignment PIN_AB15 -to dispPB | set_location_assignment PIN_AB15 -to dispPB | ||

| + | |||

| + | </pre> | ||

| + | |||

| + | == Pin List for OpenCores Build == | ||

| + | |||

| + | <pre> | ||

| + | set_global_assignment -name FAMILY "Cyclone IV E" | ||

| + | set_global_assignment -name DEVICE EP4CE15F23C8 | ||

| + | set_global_assignment -name TOP_LEVEL_ENTITY pdp8_top | ||

| + | set_global_assignment -name ORIGINAL_QUARTUS_VERSION 11.1 | ||

| + | set_global_assignment -name PROJECT_CREATION_TIME_DATE "19:28:47 OCTOBER 30, 2013" | ||

| + | set_global_assignment -name LAST_QUARTUS_VERSION "20.1.0 Lite Edition" | ||

| + | set_global_assignment -name MIN_CORE_JUNCTION_TEMP 0 | ||

| + | set_global_assignment -name MAX_CORE_JUNCTION_TEMP 85 | ||

| + | set_global_assignment -name ERROR_CHECK_FREQUENCY_DIVISOR 1 | ||

| + | set_global_assignment -name POWER_PRESET_COOLING_SOLUTION "23 MM HEAT SINK WITH 200 LFPM AIRFLOW" | ||

| + | set_global_assignment -name POWER_BOARD_THERMAL_MODEL "NONE (CONSERVATIVE)" | ||

| + | set_global_assignment -name PARTITION_NETLIST_TYPE SOURCE -section_id Top | ||

| + | set_global_assignment -name PARTITION_FITTER_PRESERVATION_LEVEL PLACEMENT_AND_ROUTING -section_id Top | ||

| + | set_global_assignment -name PARTITION_COLOR 16764057 -section_id Top | ||

| + | set_global_assignment -name STRATIX_DEVICE_IO_STANDARD "3.3-V LVTTL" | ||

| + | # Clock and reset | ||

| + | set_location_assignment PIN_T2 -to CLOCK_50 | ||

| + | set_location_assignment PIN_K22 -to reset_n | ||

| + | set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to reset_n | ||

| + | # PS/2 | ||

| + | set_location_assignment PIN_R1 -to io_PS2_CLK | ||

| + | set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to io_PS2_CLK | ||

| + | set_location_assignment PIN_R2 -to io_PS2_DAT | ||

| + | set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to io_PS2_DAT | ||

| + | # | ||

| + | set_location_assignment PIN_B10 -to TTY1_TXD_Ser | ||

| + | set_location_assignment PIN_B13 -to TTY1_RXD_Ser | ||

| + | set_location_assignment PIN_A10 -to TTY1_RTS_ser | ||

| + | set_location_assignment PIN_A13 -to TTY1_CTS_ser | ||

| + | set_location_assignment PIN_B22 -to serSelect | ||

| + | set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to serSelect | ||

| + | # Video | ||

| + | set_location_assignment PIN_B15 -to o_videoR0 | ||

| + | set_location_assignment PIN_A15 -to o_videoR1 | ||

| + | set_location_assignment PIN_B16 -to o_videoG0 | ||

| + | set_location_assignment PIN_A16 -to o_videoG1 | ||

| + | set_location_assignment PIN_B17 -to o_videoB0 | ||

| + | set_location_assignment PIN_A17 -to o_videoB1 | ||

| + | set_location_assignment PIN_B18 -to o_hSync | ||

| + | set_location_assignment PIN_A18 -to o_vSync | ||

| + | # SD Card | ||

| + | set_location_assignment PIN_B19 -to sdCS | ||

| + | set_location_assignment PIN_B20 -to sdCLK | ||

| + | set_location_assignment PIN_A19 -to sdDI | ||

| + | set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to sdDI | ||

| + | set_location_assignment PIN_A20 -to sdDO | ||

| + | set_location_assignment PIN_B14 -to sdCD | ||

| + | set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to sdCD | ||

| + | # Front Panel LEDs | ||

| + | set_location_assignment PIN_F21 -to RUN_LED | ||

| + | set_location_assignment PIN_AA15 -to PC_LED | ||

| + | set_location_assignment PIN_R21 -to AC_LED | ||

| + | set_location_assignment PIN_AA17 -to MADR_LED | ||

| + | set_location_assignment PIN_Y22 -to MD_LED | ||

| + | set_location_assignment PIN_K21 -to LINK_LED | ||

| + | # Front Panel Pushbuttons and Slide Switches | ||

| + | set_location_assignment PIN_P22 -to LDA_PB | ||

| + | set_location_assignment PIN_AB20 -to LDPC_PB | ||

| + | set_location_assignment PIN_V21 -to DEP_PB | ||

| + | set_location_assignment PIN_AB17 -to STEP_PB | ||

| + | set_location_assignment PIN_H21 -to LINK_SS | ||

| + | set_location_assignment PIN_AB15 -to DISP_PB | ||

| + | set_location_assignment PIN_J22 -to EXAM_PB | ||

| + | set_location_assignment PIN_H22 -to RUN_SS | ||

| + | # 12 LEDs | ||

| + | set_location_assignment PIN_AA14 -to OUT12_LEDs[0] | ||

| + | set_location_assignment PIN_AA16 -to OUT12_LEDs[1] | ||

| + | set_location_assignment PIN_AA18 -to OUT12_LEDs[2] | ||

| + | set_location_assignment PIN_AA19 -to OUT12_LEDs[3] | ||

| + | set_location_assignment PIN_Y21 -to OUT12_LEDs[4] | ||

| + | set_location_assignment PIN_W22 -to OUT12_LEDs[5] | ||

| + | set_location_assignment PIN_U21 -to OUT12_LEDs[6] | ||

| + | set_location_assignment PIN_P21 -to OUT12_LEDs[7] | ||

| + | set_location_assignment PIN_N21 -to OUT12_LEDs[8] | ||

| + | set_location_assignment PIN_M21 -to OUT12_LEDs[9] | ||

| + | set_location_assignment PIN_L21 -to OUT12_LEDs[10] | ||

| + | set_location_assignment PIN_J21 -to OUT12_LEDs[11] | ||

| + | # 12 Slide switches | ||

| + | set_location_assignment PIN_AB14 -to SW12_SS[0] | ||

| + | set_location_assignment PIN_AB16 -to SW12_SS[1] | ||

| + | set_location_assignment PIN_AB18 -to SW12_SS[2] | ||

| + | set_location_assignment PIN_AB19 -to SW12_SS[3] | ||

| + | set_location_assignment PIN_AA20 -to SW12_SS[4] | ||

| + | set_location_assignment PIN_W21 -to SW12_SS[5] | ||

| + | set_location_assignment PIN_V22 -to SW12_SS[6] | ||

| + | set_location_assignment PIN_U22 -to SW12_SS[7] | ||

| + | set_location_assignment PIN_R22 -to SW12_SS[8] | ||

| + | set_location_assignment PIN_N22 -to SW12_SS[9] | ||

| + | set_location_assignment PIN_M22 -to SW12_SS[10] | ||

| + | set_location_assignment PIN_L22 -to SW12_SS[11] | ||

| + | # SRAM (not used) | ||

| + | set_location_assignment PIN_F1 -to n_sRamCS | ||

| + | set_location_assignment PIN_J2 -to n_sRamOE | ||

| + | set_location_assignment PIN_B4 -to n_sRamWE | ||

| + | set_location_assignment PIN_E1 -to sramData[0] | ||

| + | set_location_assignment PIN_C1 -to sramData[1] | ||

| + | set_location_assignment PIN_B1 -to sramData[2] | ||

| + | set_location_assignment PIN_B3 -to sramData[3] | ||

| + | set_location_assignment PIN_B2 -to sramData[4] | ||

| + | set_location_assignment PIN_C2 -to sramData[5] | ||

| + | set_location_assignment PIN_D2 -to sramData[6] | ||

| + | set_location_assignment PIN_F2 -to sramData[7] | ||

| + | set_location_assignment PIN_H1 -to sramAddress[0] | ||

| + | set_location_assignment PIN_J1 -to sramAddress[1] | ||

| + | set_location_assignment PIN_M1 -to sramAddress[2] | ||

| + | set_location_assignment PIN_N1 -to sramAddress[3] | ||

| + | set_location_assignment PIN_P1 -to sramAddress[4] | ||

| + | set_location_assignment PIN_P2 -to sramAddress[5] | ||

| + | set_location_assignment PIN_N2 -to sramAddress[6] | ||

| + | set_location_assignment PIN_M2 -to sramAddress[7] | ||

| + | set_location_assignment PIN_H2 -to sramAddress[8] | ||

| + | set_location_assignment PIN_A3 -to sramAddress[9] | ||

| + | set_location_assignment PIN_A4 -to sramAddress[10] | ||

| + | set_location_assignment PIN_C3 -to sramAddress[11] | ||

| + | set_location_assignment PIN_A5 -to sramAddress[12] | ||

| + | set_location_assignment PIN_A6 -to sramAddress[13] | ||

| + | set_location_assignment PIN_A7 -to sramAddress[14] | ||

| + | set_location_assignment PIN_A8 -to sramAddress[15] | ||

| + | set_location_assignment PIN_B7 -to sramAddress[16] | ||

| + | set_location_assignment PIN_B6 -to sramAddress[17] | ||

| + | set_location_assignment PIN_B5 -to sramAddress[18] | ||

| + | set_location_assignment PIN_C4 -to sramAddress[19] | ||

| + | # SDRAM (not used) | ||

| + | set_location_assignment PIN_Y6 -to sdRamClk | ||

| + | set_location_assignment PIN_W6 -to sdRamClkEn | ||

| + | set_location_assignment PIN_AA4 -to n_sdRamCas | ||

| + | set_location_assignment PIN_AA3 -to n_sdRamCe | ||

| + | set_location_assignment PIN_AB3 -to n_sdRamRas | ||

| + | set_location_assignment PIN_AB4 -to n_sdRamWe | ||

| + | set_location_assignment PIN_V2 -to sdRamAddr[0] | ||

| + | set_location_assignment PIN_V1 -to sdRamAddr[1] | ||

| + | set_location_assignment PIN_U2 -to sdRamAddr[2] | ||

| + | set_location_assignment PIN_U1 -to sdRamAddr[3] | ||

| + | set_location_assignment PIN_V3 -to sdRamAddr[4] | ||

| + | set_location_assignment PIN_V4 -to sdRamAddr[5] | ||

| + | set_location_assignment PIN_Y2 -to sdRamAddr[6] | ||

| + | set_location_assignment PIN_AA1 -to sdRamAddr[7] | ||

| + | set_location_assignment PIN_Y3 -to sdRamAddr[8] | ||

| + | set_location_assignment PIN_V5 -to sdRamAddr[9] | ||

| + | set_location_assignment PIN_W1 -to sdRamAddr[10] | ||

| + | set_location_assignment PIN_Y4 -to sdRamAddr[11] | ||

| + | set_location_assignment PIN_V6 -to sdRamAddr[12] | ||

| + | set_location_assignment PIN_Y1 -to sdRamAddr[13] | ||

| + | set_location_assignment PIN_W2 -to sdRamAddr[14] | ||

| + | set_location_assignment PIN_AA10 -to sdRamData[0] | ||

| + | set_location_assignment PIN_AB9 -to sdRamData[1] | ||

| + | set_location_assignment PIN_AA9 -to sdRamData[2] | ||

| + | set_location_assignment PIN_AB8 -to sdRamData[3] | ||

| + | set_location_assignment PIN_AA8 -to sdRamData[4] | ||

| + | set_location_assignment PIN_AB7 -to sdRamData[5] | ||

| + | set_location_assignment PIN_AA7 -to sdRamData[6] | ||

| + | set_location_assignment PIN_AB5 -to sdRamData[7] | ||

| + | set_location_assignment PIN_Y7 -to sdRamData[8] | ||

| + | set_location_assignment PIN_W8 -to sdRamData[9] | ||

| + | set_location_assignment PIN_Y8 -to sdRamData[10] | ||

| + | set_location_assignment PIN_V9 -to sdRamData[11] | ||

| + | set_location_assignment PIN_V10 -to sdRamData[12] | ||

| + | set_location_assignment PIN_Y10 -to sdRamData[13] | ||

| + | set_location_assignment PIN_W10 -to sdRamData[14] | ||

| + | set_location_assignment PIN_V11 -to sdRamData[15] | ||

| + | |||

</pre> | </pre> | ||

| Line 145: | Line 431: | ||

== PDP-8 Front Panel Assembly Sheet == | == PDP-8 Front Panel Assembly Sheet == | ||

| − | [[PDP-8 Front Panel Assembly Sheet]] | + | * [[PDP-8 Front Panel Assembly Sheet]] |

Revision as of 14:29, 25 May 2022

Contents

Features

- 50-pin connector

- 2x25 Pinout matches RETRO-EP4CE15 Card pins (1:1 cable)

- Some unused pins - wired to +3.3V/GND for connecting other cards

- 12 Value LEDs (DB-11) - silkscreen marked in octal format

- DISP pushbutton - Selects what is on the 12 Value LEDs

- I like diffused orange color the best for LEDs - looks retro

- Pushing DISP cycles between LEDs displaying PC, Memory Address, Memory Data, Accumulator

- 12 Load Value Slide Switches (SL0-11) - octal format

- Enter values: Program Counter (PC), Memory Address, Memory Data, Accumulator

- Pushbutton Switches

- STEP pushbutton - Increment PC

- LDPC pushbutton - Store value from Value Slide Switches to Program Counter (PC)

- DEP pushbutton - Store value from Value Slide Switches to memory

- LDA pushbutton - Store value from Value Slide Switches to Accumulator

- RES - Reset pushbutton - Resets CPU

- PB1 - spare pushbutton

- 4 DISP LEDs - Indicates what is being shown on the 12 LEDs

- Cycle between 12 LEDs source with DISP pushbutton

- PC - 12 LEDs display Program Counter value

- MADR - 12 LEDs display Memory Address value

- MD - 12 LEDs display Memory Data value

- AC - 12 LEDs display Accumulator value

- LNK - Link value slide switch

- LINK LED - Displays Link value

- RUN LED - Running program

- RUN/HALT slide switch

- PWR - Power LED

- 95x95mm form factor matches RETRO-EP4CE15

- (4) 6-32 mounting holes

- Boards can be stacked with standoffs

PDP-8 FPGA Designs

- Two working designs

- Tom Almy's PDP-8

- OpenCores PDP-8 FPGA designs

Build of Tom Almy's PDP-8 FPGA (Working 2021-May)

Build is based on Tom Almy's book The PDP-8 Class Project: Resoling An Old Machine.

- Hackaday page with progress logs

- PDP-8 PFGA Design - GitHub repo

- My PDP-8 Software GitHub repository

- PDP-8 with Front Panel and VDU

Hardware used

- RETRO-EP4CE15 - FPGA Hardware used

- QMTECH EP4CE15 FPGA Card

- PDP-8 Front Panel

FPGA Resources

- Front Panel

- Cyclone IV

+----------------------------------------------------------------------------------+ ; Fitter Summary ; +------------------------------------+---------------------------------------------+ ; Fitter Status ; Successful - Sat Apr 30 20:28:20 2022 ; ; Quartus Prime Version ; 21.1.0 Build 842 10/21/2021 SJ Lite Edition ; ; Revision Name ; pdp8 ; ; Top-level Entity Name ; pdp8 ; ; Family ; Cyclone IV E ; ; Device ; EP4CE15F23C8 ; ; Timing Models ; Final ; ; Total logic elements ; 2,390 / 15,408 ( 16 % ) ; ; Total combinational functions ; 2,300 / 15,408 ( 15 % ) ; ; Dedicated logic registers ; 734 / 15,408 ( 5 % ) ; ; Total registers ; 734 ; ; Total pins ; 51 / 344 ( 15 % ) ; ; Total virtual pins ; 0 ; ; Total memory bits ; 98,304 / 516,096 ( 19 % ) ; ; Embedded Multiplier 9-bit elements ; 2 / 112 ( 2 % ) ; ; Total PLLs ; 0 / 4 ( 0 % ) ; +------------------------------------+---------------------------------------------+

OpenCores PDP-8 Build

- Hackaday page with progress logs

- Wider features than Tom Almy's design

- Supports 32 K words of memory

- SD card support

- Boot OS/8

- Land Board OpenCores PDP-8 Builds - GitHub repository

- Two tested/working builds

- Built in ANSI Terminal build

- Serial I/O build

RETRO-EP4CE15_CYCLONE_IV_VDU PDP-8 Build

- RETRO-EP4CE15_CYCLONE_IV_VDU PDP-8 Build

- Built in ANSI Terminal with cpu_001 (IOP16B built-in) - Latest build

- VDU IOP assembly code

- Hackaday project page for ANSI Terminal

RETRO-EP4CE15_CYCLONE_IV PDP-8 Build

- RETRO-EP4CE15_CYCLONE_IV

- Serial only (no VDU)

RETRO-EP4CE15_CYCLONE_V PDP-8 Build

- RETRO-EP4CE15_CYCLONE_V

- WIP - missing pin assignment

Hardware used

- RETRO-EP4CE15 - FPGA Hardware used

- QMTECH EP4CE15 FPGA Card

- PDP-8 Front Panel

FPGA Resources

- ANSI Terminal (IOP-16)

- Cyclone IV

+----------------------------------------------------------------------------------+ ; Fitter Summary ; +------------------------------------+---------------------------------------------+ ; Fitter Status ; Successful - Sat Apr 9 19:53:05 2022 ; ; Quartus Prime Version ; 21.1.0 Build 842 10/21/2021 SJ Lite Edition ; ; Revision Name ; pdp8_top ; ; Top-level Entity Name ; pdp8_top ; ; Family ; Cyclone IV E ; ; Device ; EP4CE15F23C8 ; ; Timing Models ; Final ; ; Total logic elements ; 5,273 / 15,408 ( 34 % ) ; ; Total combinational functions ; 5,023 / 15,408 ( 33 % ) ; ; Dedicated logic registers ; 1,569 / 15,408 ( 10 % ) ; ; Total registers ; 1569 ; ; Total pins ; 128 / 344 ( 37 % ) ; ; Total virtual pins ; 0 ; ; Total memory bits ; 426,112 / 516,096 ( 83 % ) ; ; Embedded Multiplier 9-bit elements ; 2 / 112 ( 2 % ) ; ; Total PLLs ; 0 / 4 ( 0 % ) ; +------------------------------------+---------------------------------------------+

opencores PDP-8 Processor Reference

J1 Connector

- Extra power and ground pins (not on RETRO-EP4CE15 Card)

- Pins 3,4 = GND

- Pins 5-8 = VCC

- Pin 9 = N/C

J1 to RETRO-EP4CE15 Pin Mapping

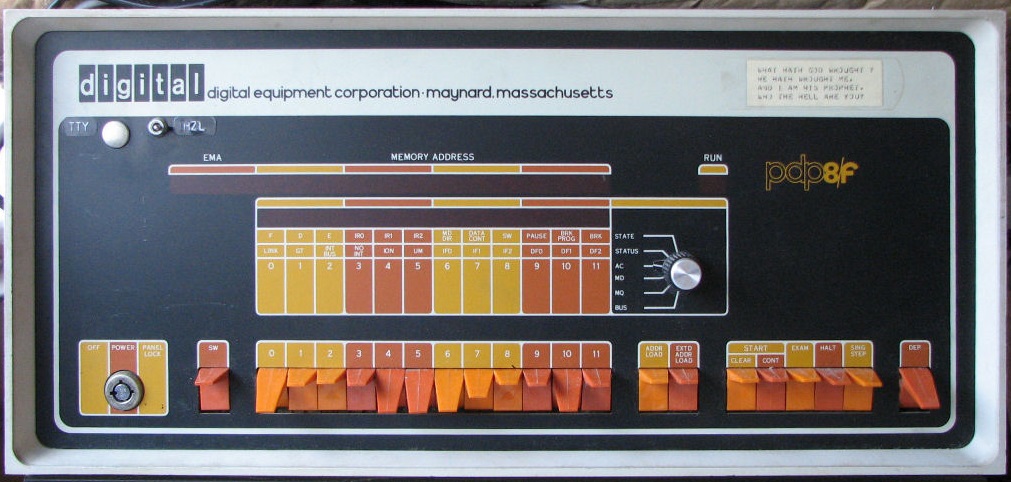

Real PDP-8/F Front Panel

Pin List for Tom Almy FPGA Build

set_global_assignment -name FAMILY "Cyclone IV E" set_global_assignment -name DEVICE EP4CE15F23C8 set_global_assignment -name TOP_LEVEL_ENTITY pdp8 set_global_assignment -name ORIGINAL_QUARTUS_VERSION 18.1.0 set_global_assignment -name PROJECT_CREATION_TIME_DATE "13:56:19 MARCH 15, 2021" set_global_assignment -name LAST_QUARTUS_VERSION "20.1.0 Lite Edition" set_global_assignment -name PROJECT_OUTPUT_DIRECTORY output_files set_global_assignment -name MIN_CORE_JUNCTION_TEMP 0 set_global_assignment -name MAX_CORE_JUNCTION_TEMP 85 set_global_assignment -name ERROR_CHECK_FREQUENCY_DIVISOR 1 set_global_assignment -name NOMINAL_CORE_SUPPLY_VOLTAGE 1.2V set_global_assignment -name PARTITION_NETLIST_TYPE SOURCE -section_id Top set_global_assignment -name PARTITION_FITTER_PRESERVATION_LEVEL PLACEMENT_AND_ROUTING -section_id Top set_global_assignment -name PARTITION_COLOR 16764057 -section_id Top set_global_assignment -name POWER_PRESET_COOLING_SOLUTION "23 MM HEAT SINK WITH 200 LFPM AIRFLOW" set_global_assignment -name POWER_BOARD_THERMAL_MODEL "NONE (CONSERVATIVE)" set_global_assignment -name TIMING_ANALYZER_MULTICORNER_ANALYSIS ON set_global_assignment -name SMART_RECOMPILE ON set_global_assignment -name PROJECT_IP_REGENERATION_POLICY ALWAYS_REGENERATE_IP set_global_assignment -name STRATIX_DEVICE_IO_STANDARD "3.3-V LVTTL" # Clock, reset button set_location_assignment PIN_T2 -to clk set_location_assignment PIN_K22 -to btnCpuReset set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to btnCpuReset # Run Switch/LED set_location_assignment PIN_H22 -to runSwitch set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to runSwitch set_location_assignment PIN_F21 -to runLED # Serial set_location_assignment PIN_B13 -to RsRx set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to RsRx set_location_assignment PIN_B10 -to RsTx # PS/2 set_location_assignment PIN_R1 -to io_ps2Clk set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to io_ps2Clk set_location_assignment PIN_R2 -to io_ps2Data set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to io_ps2Data # VGA set_location_assignment PIN_A17 -to o_vid_blu[1] set_location_assignment PIN_B17 -to o_vid_blu[0] set_location_assignment PIN_A16 -to o_vid_grn[1] set_location_assignment PIN_B16 -to o_vid_grn[0] set_location_assignment PIN_A15 -to o_vid_red[1] set_location_assignment PIN_B15 -to o_vid_red[0] set_location_assignment PIN_B18 -to o_vid_hSync set_location_assignment PIN_A18 -to o_vid_vSync # 12 Slide switches set_location_assignment PIN_AB14 -to sw[0] set_location_assignment PIN_AB16 -to sw[1] set_location_assignment PIN_AB18 -to sw[2] set_location_assignment PIN_AB19 -to sw[3] set_location_assignment PIN_AA20 -to sw[4] set_location_assignment PIN_W21 -to sw[5] set_location_assignment PIN_V22 -to sw[6] set_location_assignment PIN_U22 -to sw[7] set_location_assignment PIN_R22 -to sw[8] set_location_assignment PIN_N22 -to sw[9] set_location_assignment PIN_M22 -to sw[10] set_location_assignment PIN_L22 -to sw[11] # 12 LEDs set_location_assignment PIN_J21 -to dispLEDs[11] set_location_assignment PIN_L21 -to dispLEDs[10] set_location_assignment PIN_M21 -to dispLEDs[9] set_location_assignment PIN_N21 -to dispLEDs[8] set_location_assignment PIN_P21 -to dispLEDs[7] set_location_assignment PIN_U21 -to dispLEDs[6] set_location_assignment PIN_W22 -to dispLEDs[5] set_location_assignment PIN_Y21 -to dispLEDs[4] set_location_assignment PIN_AA19 -to dispLEDs[3] set_location_assignment PIN_AA18 -to dispLEDs[2] set_location_assignment PIN_AA16 -to dispLEDs[1] set_location_assignment PIN_AA14 -to dispLEDs[0] # Status/Operation LEDs set_location_assignment PIN_K21 -to linkLED set_location_assignment PIN_Y22 -to dispMDLED set_location_assignment PIN_AA17 -to dispMALED set_location_assignment PIN_AA15 -to dispPCLED set_location_assignment PIN_R21 -to dispACLED set_location_assignment PIN_H21 -to lnkSwitch # Pushbuttons set_location_assignment PIN_AB17 -to stepPB set_location_assignment PIN_V21 -to depPB set_location_assignment PIN_AB20 -to ldPCPB set_location_assignment PIN_P22 -to ldACPB set_location_assignment PIN_AB15 -to dispPB

Pin List for OpenCores Build

set_global_assignment -name FAMILY "Cyclone IV E" set_global_assignment -name DEVICE EP4CE15F23C8 set_global_assignment -name TOP_LEVEL_ENTITY pdp8_top set_global_assignment -name ORIGINAL_QUARTUS_VERSION 11.1 set_global_assignment -name PROJECT_CREATION_TIME_DATE "19:28:47 OCTOBER 30, 2013" set_global_assignment -name LAST_QUARTUS_VERSION "20.1.0 Lite Edition" set_global_assignment -name MIN_CORE_JUNCTION_TEMP 0 set_global_assignment -name MAX_CORE_JUNCTION_TEMP 85 set_global_assignment -name ERROR_CHECK_FREQUENCY_DIVISOR 1 set_global_assignment -name POWER_PRESET_COOLING_SOLUTION "23 MM HEAT SINK WITH 200 LFPM AIRFLOW" set_global_assignment -name POWER_BOARD_THERMAL_MODEL "NONE (CONSERVATIVE)" set_global_assignment -name PARTITION_NETLIST_TYPE SOURCE -section_id Top set_global_assignment -name PARTITION_FITTER_PRESERVATION_LEVEL PLACEMENT_AND_ROUTING -section_id Top set_global_assignment -name PARTITION_COLOR 16764057 -section_id Top set_global_assignment -name STRATIX_DEVICE_IO_STANDARD "3.3-V LVTTL" # Clock and reset set_location_assignment PIN_T2 -to CLOCK_50 set_location_assignment PIN_K22 -to reset_n set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to reset_n # PS/2 set_location_assignment PIN_R1 -to io_PS2_CLK set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to io_PS2_CLK set_location_assignment PIN_R2 -to io_PS2_DAT set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to io_PS2_DAT # set_location_assignment PIN_B10 -to TTY1_TXD_Ser set_location_assignment PIN_B13 -to TTY1_RXD_Ser set_location_assignment PIN_A10 -to TTY1_RTS_ser set_location_assignment PIN_A13 -to TTY1_CTS_ser set_location_assignment PIN_B22 -to serSelect set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to serSelect # Video set_location_assignment PIN_B15 -to o_videoR0 set_location_assignment PIN_A15 -to o_videoR1 set_location_assignment PIN_B16 -to o_videoG0 set_location_assignment PIN_A16 -to o_videoG1 set_location_assignment PIN_B17 -to o_videoB0 set_location_assignment PIN_A17 -to o_videoB1 set_location_assignment PIN_B18 -to o_hSync set_location_assignment PIN_A18 -to o_vSync # SD Card set_location_assignment PIN_B19 -to sdCS set_location_assignment PIN_B20 -to sdCLK set_location_assignment PIN_A19 -to sdDI set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to sdDI set_location_assignment PIN_A20 -to sdDO set_location_assignment PIN_B14 -to sdCD set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to sdCD # Front Panel LEDs set_location_assignment PIN_F21 -to RUN_LED set_location_assignment PIN_AA15 -to PC_LED set_location_assignment PIN_R21 -to AC_LED set_location_assignment PIN_AA17 -to MADR_LED set_location_assignment PIN_Y22 -to MD_LED set_location_assignment PIN_K21 -to LINK_LED # Front Panel Pushbuttons and Slide Switches set_location_assignment PIN_P22 -to LDA_PB set_location_assignment PIN_AB20 -to LDPC_PB set_location_assignment PIN_V21 -to DEP_PB set_location_assignment PIN_AB17 -to STEP_PB set_location_assignment PIN_H21 -to LINK_SS set_location_assignment PIN_AB15 -to DISP_PB set_location_assignment PIN_J22 -to EXAM_PB set_location_assignment PIN_H22 -to RUN_SS # 12 LEDs set_location_assignment PIN_AA14 -to OUT12_LEDs[0] set_location_assignment PIN_AA16 -to OUT12_LEDs[1] set_location_assignment PIN_AA18 -to OUT12_LEDs[2] set_location_assignment PIN_AA19 -to OUT12_LEDs[3] set_location_assignment PIN_Y21 -to OUT12_LEDs[4] set_location_assignment PIN_W22 -to OUT12_LEDs[5] set_location_assignment PIN_U21 -to OUT12_LEDs[6] set_location_assignment PIN_P21 -to OUT12_LEDs[7] set_location_assignment PIN_N21 -to OUT12_LEDs[8] set_location_assignment PIN_M21 -to OUT12_LEDs[9] set_location_assignment PIN_L21 -to OUT12_LEDs[10] set_location_assignment PIN_J21 -to OUT12_LEDs[11] # 12 Slide switches set_location_assignment PIN_AB14 -to SW12_SS[0] set_location_assignment PIN_AB16 -to SW12_SS[1] set_location_assignment PIN_AB18 -to SW12_SS[2] set_location_assignment PIN_AB19 -to SW12_SS[3] set_location_assignment PIN_AA20 -to SW12_SS[4] set_location_assignment PIN_W21 -to SW12_SS[5] set_location_assignment PIN_V22 -to SW12_SS[6] set_location_assignment PIN_U22 -to SW12_SS[7] set_location_assignment PIN_R22 -to SW12_SS[8] set_location_assignment PIN_N22 -to SW12_SS[9] set_location_assignment PIN_M22 -to SW12_SS[10] set_location_assignment PIN_L22 -to SW12_SS[11] # SRAM (not used) set_location_assignment PIN_F1 -to n_sRamCS set_location_assignment PIN_J2 -to n_sRamOE set_location_assignment PIN_B4 -to n_sRamWE set_location_assignment PIN_E1 -to sramData[0] set_location_assignment PIN_C1 -to sramData[1] set_location_assignment PIN_B1 -to sramData[2] set_location_assignment PIN_B3 -to sramData[3] set_location_assignment PIN_B2 -to sramData[4] set_location_assignment PIN_C2 -to sramData[5] set_location_assignment PIN_D2 -to sramData[6] set_location_assignment PIN_F2 -to sramData[7] set_location_assignment PIN_H1 -to sramAddress[0] set_location_assignment PIN_J1 -to sramAddress[1] set_location_assignment PIN_M1 -to sramAddress[2] set_location_assignment PIN_N1 -to sramAddress[3] set_location_assignment PIN_P1 -to sramAddress[4] set_location_assignment PIN_P2 -to sramAddress[5] set_location_assignment PIN_N2 -to sramAddress[6] set_location_assignment PIN_M2 -to sramAddress[7] set_location_assignment PIN_H2 -to sramAddress[8] set_location_assignment PIN_A3 -to sramAddress[9] set_location_assignment PIN_A4 -to sramAddress[10] set_location_assignment PIN_C3 -to sramAddress[11] set_location_assignment PIN_A5 -to sramAddress[12] set_location_assignment PIN_A6 -to sramAddress[13] set_location_assignment PIN_A7 -to sramAddress[14] set_location_assignment PIN_A8 -to sramAddress[15] set_location_assignment PIN_B7 -to sramAddress[16] set_location_assignment PIN_B6 -to sramAddress[17] set_location_assignment PIN_B5 -to sramAddress[18] set_location_assignment PIN_C4 -to sramAddress[19] # SDRAM (not used) set_location_assignment PIN_Y6 -to sdRamClk set_location_assignment PIN_W6 -to sdRamClkEn set_location_assignment PIN_AA4 -to n_sdRamCas set_location_assignment PIN_AA3 -to n_sdRamCe set_location_assignment PIN_AB3 -to n_sdRamRas set_location_assignment PIN_AB4 -to n_sdRamWe set_location_assignment PIN_V2 -to sdRamAddr[0] set_location_assignment PIN_V1 -to sdRamAddr[1] set_location_assignment PIN_U2 -to sdRamAddr[2] set_location_assignment PIN_U1 -to sdRamAddr[3] set_location_assignment PIN_V3 -to sdRamAddr[4] set_location_assignment PIN_V4 -to sdRamAddr[5] set_location_assignment PIN_Y2 -to sdRamAddr[6] set_location_assignment PIN_AA1 -to sdRamAddr[7] set_location_assignment PIN_Y3 -to sdRamAddr[8] set_location_assignment PIN_V5 -to sdRamAddr[9] set_location_assignment PIN_W1 -to sdRamAddr[10] set_location_assignment PIN_Y4 -to sdRamAddr[11] set_location_assignment PIN_V6 -to sdRamAddr[12] set_location_assignment PIN_Y1 -to sdRamAddr[13] set_location_assignment PIN_W2 -to sdRamAddr[14] set_location_assignment PIN_AA10 -to sdRamData[0] set_location_assignment PIN_AB9 -to sdRamData[1] set_location_assignment PIN_AA9 -to sdRamData[2] set_location_assignment PIN_AB8 -to sdRamData[3] set_location_assignment PIN_AA8 -to sdRamData[4] set_location_assignment PIN_AB7 -to sdRamData[5] set_location_assignment PIN_AA7 -to sdRamData[6] set_location_assignment PIN_AB5 -to sdRamData[7] set_location_assignment PIN_Y7 -to sdRamData[8] set_location_assignment PIN_W8 -to sdRamData[9] set_location_assignment PIN_Y8 -to sdRamData[10] set_location_assignment PIN_V9 -to sdRamData[11] set_location_assignment PIN_V10 -to sdRamData[12] set_location_assignment PIN_Y10 -to sdRamData[13] set_location_assignment PIN_W10 -to sdRamData[14] set_location_assignment PIN_V11 -to sdRamData[15]