Difference between revisions of "TG68 AMR Build"

Jump to navigation

Jump to search

Blwikiadmin (talk | contribs) |

Blwikiadmin (talk | contribs) |

||

| (30 intermediate revisions by the same user not shown) | |||

| Line 1: | Line 1: | ||

| + | [[FILE:TG68_AMR_P18123_720PX.jpg]] | ||

| + | |||

== TG68 AMR Build == | == TG68 AMR Build == | ||

| − | * [[ | + | TG68 AMR is a 68000 based Computer with a large Video Frame Buffer. |

| + | |||

| + | * [https://hackaday.io/project/174679-68k-cpu-with-frame-buffer-on-fpga Hackaday Project page] | ||

| + | * [[QMTECH_EP4CE15_FPGA_Starter_Kit|QMTECH EP4CE15 Standalone Board]] | ||

** 68000 CPU | ** 68000 CPU | ||

** VGA (5:6:5) | ** VGA (5:6:5) | ||

** 32 MB SDRAM | ** 32 MB SDRAM | ||

* [[SD_CARD_X49|Land Boards SD Card]] | * [[SD_CARD_X49|Land Boards SD Card]] | ||

| + | ** FAT32 format (used 8 GB standard SD card) | ||

* [[FTDI-49MM|Land Boards FTDI Card]] | * [[FTDI-49MM|Land Boards FTDI Card]] | ||

| + | ** USB to Serial | ||

| + | ** 115,200 baud, n,8,1, no handshake | ||

* [[PS2X49|Land Boards PS/2 card]] | * [[PS2X49|Land Boards PS/2 card]] | ||

| + | ** Mouse/keyboard | ||

| + | * Stereo Output | ||

* [https://www.amazon.com/dp/B07SW4RQBQ?psc=1&ref=ppx_yo2_dt_b_product_details YaeCCC Rectangle Project Enclosure Case Electric Junction Box Blue] | * [https://www.amazon.com/dp/B07SW4RQBQ?psc=1&ref=ppx_yo2_dt_b_product_details YaeCCC Rectangle Project Enclosure Case Electric Junction Box Blue] | ||

** 170mm x 130mm x 80mm / 6.4" x 4.3" x 2.7" | ** 170mm x 130mm x 80mm / 6.4" x 4.3" x 2.7" | ||

| + | |||

| + | == Credits == | ||

| + | |||

| + | Original design by Alastair M. Robinson referred to by his initials AMR. | ||

| + | |||

| + | * [http://retroramblings.net/?page_id=770 Retro Ramblings TG68 Experiments] - AMRs BLOG | ||

| + | * [https://github.com/robinsonb5/TG68_MiniSOC AMR's GitHub Repository] | ||

| + | |||

| + | == Performance == | ||

| + | |||

| + | * VAX MIPS rating * 1000 = 4773 (4.77 MIPS) | ||

| + | |||

| + | == PuTTY Setup == | ||

| + | |||

| + | * Terminal | ||

| + | ** Implicit CR in every LF | ||

| + | ** Implicit LF in every CR | ||

| + | * Window - Appearance | ||

| + | ** Window Title: COMxx_TG68_AMR | ||

| + | * Connection - Serial | ||

| + | ** No hardware handshake | ||

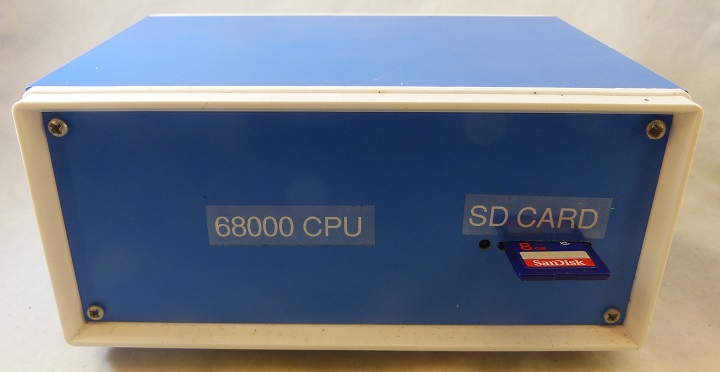

== J12 - I/O Connector == | == J12 - I/O Connector == | ||

| Line 15: | Line 46: | ||

[[File:QMTECH_EP4CE15_StarterKit_J12.PNG]] | [[File:QMTECH_EP4CE15_StarterKit_J12.PNG]] | ||

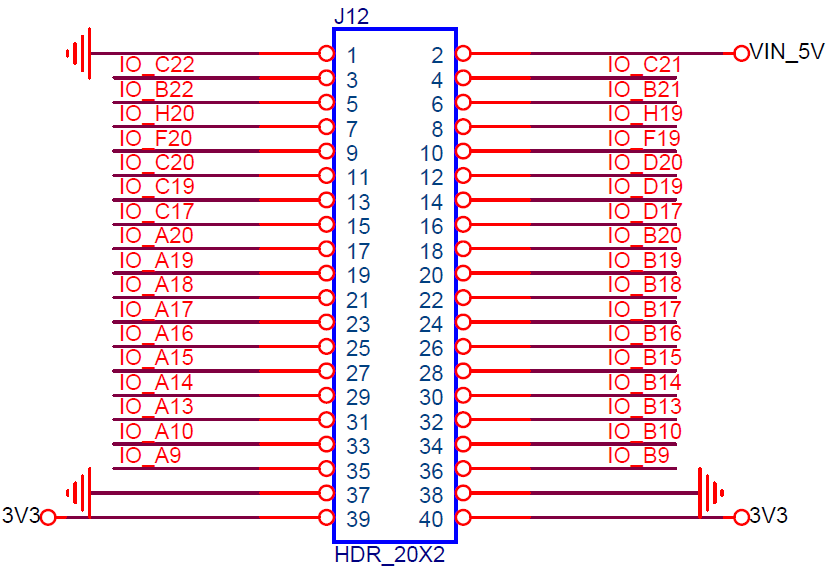

| − | == | + | == Wiring == |

| − | [[file: | + | [[file:TG68_WIRING.PNG]] |

| − | + | == Software == | |

| − | [[ | + | * [https://github.com/douggilliland/Linux-68k/tree/master/TG68_AMR_Software GitHub Repo] |

| + | ** [https://github.com/douggilliland/Linux-68k/tree/master/TG68_AMR_Software/Apps/ Applications] | ||

| − | + | === Demo === | |

| − | [ | + | * [https://github.com/douggilliland/Linux-68k/tree/master/TG68_AMR_Software/Apps/Demo Demo GitHub Repo] |

| + | ** Load boot.sre to FAT32 formatted SD card | ||

| + | ** Load test.img to SD card | ||

| + | ** Insert SD card | ||

| + | ** Turn on (plug in USB power cable) | ||

| + | ** Press F1-F9,F12 for demos | ||

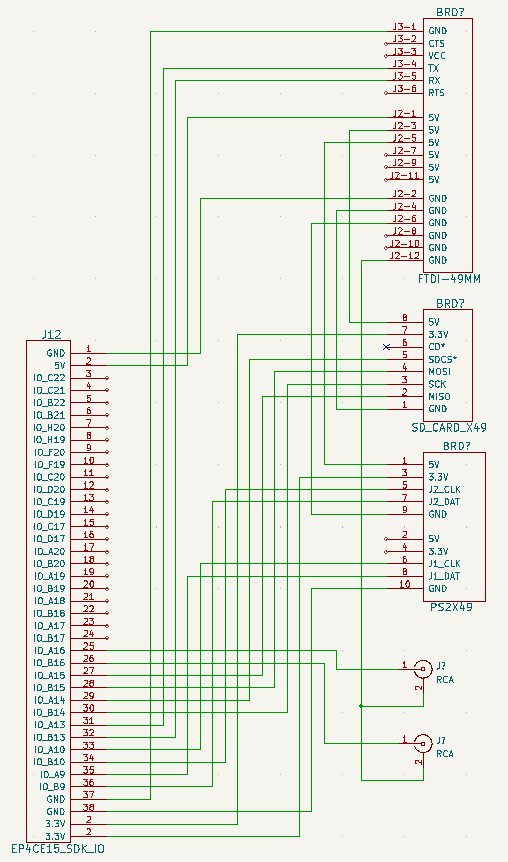

| − | + | == VHDL Code == | |

| − | [ | + | * [https://github.com/douggilliland/Retro-Computers/tree/master/68000/TG68_AMR/TG68_AMR_FPGA/SOC/fpga/QMTECH_CycloneIV_Starter_Kit GitHub Repo] |

| − | + | === Resources === | |

| + | [[file:TG68_AMR_Resources.PNG]] | ||

== Pin List == | == Pin List == | ||

| + | |||

| + | {| class="wikitable" | ||

| + | ! To | ||

| + | ! Direction | ||

| + | ! Location | ||

| + | ! I/O Standard | ||

| + | ! Pull-Up | ||

| + | |- | ||

| + | | aud_l | ||

| + | | Output | ||

| + | | PIN_B16 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | aud_r | ||

| + | | Output | ||

| + | | PIN_A16 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | clk_50 | ||

| + | | Input | ||

| + | | PIN_T2 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | io_sdram_data[15] | ||

| + | | Bidir | ||

| + | | PIN_V11 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | io_sdram_data[14] | ||

| + | | Bidir | ||

| + | | PIN_W10 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | io_sdram_data[13] | ||

| + | | Bidir | ||

| + | | PIN_Y10 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | io_sdram_data[12] | ||

| + | | Bidir | ||

| + | | PIN_V10 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | io_sdram_data[11] | ||

| + | | Bidir | ||

| + | | PIN_V9 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | io_sdram_data[10] | ||

| + | | Bidir | ||

| + | | PIN_Y8 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | io_sdram_data[9] | ||

| + | | Bidir | ||

| + | | PIN_W8 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | io_sdram_data[8] | ||

| + | | Bidir | ||

| + | | PIN_Y7 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | io_sdram_data[7] | ||

| + | | Bidir | ||

| + | | PIN_AB5 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | io_sdram_data[6] | ||

| + | | Bidir | ||

| + | | PIN_AA7 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | io_sdram_data[5] | ||

| + | | Bidir | ||

| + | | PIN_AB7 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | io_sdram_data[4] | ||

| + | | Bidir | ||

| + | | PIN_AA8 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | io_sdram_data[3] | ||

| + | | Bidir | ||

| + | | PIN_AB8 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | io_sdram_data[2] | ||

| + | | Bidir | ||

| + | | PIN_AA9 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | io_sdram_data[1] | ||

| + | | Bidir | ||

| + | | PIN_AB9 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | io_sdram_data[0] | ||

| + | | Bidir | ||

| + | | PIN_AA10 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | leds[3] | ||

| + | | Output | ||

| + | | PIN_B21 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | leds[2] | ||

| + | | Output | ||

| + | | PIN_B22 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | leds[1] | ||

| + | | Output | ||

| + | | PIN_C21 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | leds[0] | ||

| + | | Output | ||

| + | | PIN_C22 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | o_sdram_addr[12] | ||

| + | | Output | ||

| + | | PIN_V6 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | o_sdram_addr[11] | ||

| + | | Output | ||

| + | | PIN_Y4 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | o_sdram_addr[10] | ||

| + | | Output | ||

| + | | PIN_W1 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | o_sdram_addr[9] | ||

| + | | Output | ||

| + | | PIN_V5 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | o_sdram_addr[8] | ||

| + | | Output | ||

| + | | PIN_Y3 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | o_sdram_addr[7] | ||

| + | | Output | ||

| + | | PIN_AA1 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | o_sdram_addr[6] | ||

| + | | Output | ||

| + | | PIN_Y2 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | o_sdram_addr[5] | ||

| + | | Output | ||

| + | | PIN_V4 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | o_sdram_addr[4] | ||

| + | | Output | ||

| + | | PIN_V3 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | o_sdram_addr[3] | ||

| + | | Output | ||

| + | | PIN_U1 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | o_sdram_addr[2] | ||

| + | | Output | ||

| + | | PIN_U2 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | o_sdram_addr[1] | ||

| + | | Output | ||

| + | | PIN_V1 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | o_sdram_addr[0] | ||

| + | | Output | ||

| + | | PIN_V2 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | o_sdram_ba[1] | ||

| + | | Output | ||

| + | | PIN_W2 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | o_sdram_ba[0] | ||

| + | | Output | ||

| + | | PIN_Y1 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | o_sdram_cas | ||

| + | | Output | ||

| + | | PIN_AA4 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | o_sdram_cke | ||

| + | | Output | ||

| + | | PIN_W6 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | o_sdram_clk | ||

| + | | Output | ||

| + | | PIN_Y6 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | o_sdram_cs | ||

| + | | Output | ||

| + | | PIN_AA3 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | o_sdram_ldqm | ||

| + | | Output | ||

| + | | PIN_AA5 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | o_sdram_ras | ||

| + | | Output | ||

| + | | PIN_AB3 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | o_sdram_udqm | ||

| + | | Output | ||

| + | | PIN_W7 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | o_sdram_we | ||

| + | | Output | ||

| + | | PIN_AB4 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | o_vga_blue[4] | ||

| + | | Output | ||

| + | | PIN_AA14 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | o_vga_blue[3] | ||

| + | | Output | ||

| + | | PIN_AB13 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | o_vga_blue[2] | ||

| + | | Output | ||

| + | | PIN_AA15 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | o_vga_blue[1] | ||

| + | | Output | ||

| + | | PIN_AB14 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | o_vga_blue[0] | ||

| + | | Output | ||

| + | | PIN_AB15 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | o_vga_green[5] | ||

| + | | Output | ||

| + | | PIN_AB16 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | o_vga_green[4] | ||

| + | | Output | ||

| + | | PIN_AA16 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | o_vga_green[3] | ||

| + | | Output | ||

| + | | PIN_AB17 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | o_vga_green[2] | ||

| + | | Output | ||

| + | | PIN_AA17 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | o_vga_green[1] | ||

| + | | Output | ||

| + | | PIN_AA18 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | o_vga_green[0] | ||

| + | | Output | ||

| + | | PIN_AB18 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | o_vga_hsync | ||

| + | | Output | ||

| + | | PIN_AA13 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | o_vga_red[4] | ||

| + | | Output | ||

| + | | PIN_AB19 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | o_vga_red[3] | ||

| + | | Output | ||

| + | | PIN_AA19 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | o_vga_red[2] | ||

| + | | Output | ||

| + | | PIN_AB20 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | o_vga_red[1] | ||

| + | | Output | ||

| + | | PIN_AA20 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | o_vga_red[0] | ||

| + | | Output | ||

| + | | PIN_AA21 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | o_vga_vsync | ||

| + | | Output | ||

| + | | PIN_AB10 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | power_button | ||

| + | | Input | ||

| + | | PIN_C20 | ||

| + | | 3.3-V LVTTL | ||

| + | | on | ||

| + | |- | ||

| + | | power_hold | ||

| + | | Output | ||

| + | | PIN_D20 | ||

| + | | 3.3-V LVTTL | ||

| + | | on | ||

| + | |- | ||

| + | | ps2k_clk | ||

| + | | Bidir | ||

| + | | PIN_A10 | ||

| + | | 3.3-V LVTTL | ||

| + | | on | ||

| + | |- | ||

| + | | ps2k_dat | ||

| + | | Bidir | ||

| + | | PIN_A9 | ||

| + | | 3.3-V LVTTL | ||

| + | | on | ||

| + | |- | ||

| + | | ps2m_clk | ||

| + | | Bidir | ||

| + | | PIN_B10 | ||

| + | | 3.3-V LVTTL | ||

| + | | on | ||

| + | |- | ||

| + | | ps2m_dat | ||

| + | | Bidir | ||

| + | | PIN_B9 | ||

| + | | 3.3-V LVTTL | ||

| + | | on | ||

| + | |- | ||

| + | | reset_n | ||

| + | | Input | ||

| + | | PIN_J4 | ||

| + | | 3.3-V LVTTL | ||

| + | | on | ||

| + | |- | ||

| + | | rs232_rxd | ||

| + | | Input | ||

| + | | PIN_A13 | ||

| + | | 3.3-V LVTTL | ||

| + | | on | ||

| + | |- | ||

| + | | rs232_txd | ||

| + | | Output | ||

| + | | PIN_B13 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | sd_clk | ||

| + | | Output | ||

| + | | PIN_B14 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | sd_cs | ||

| + | | Output | ||

| + | | PIN_A14 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | | sd_miso | ||

| + | | Input | ||

| + | | PIN_A15 | ||

| + | | 3.3-V LVTTL | ||

| + | | on | ||

| + | |- | ||

| + | | sd_mosi | ||

| + | | Output | ||

| + | | PIN_B15 | ||

| + | | 3.3-V LVTTL | ||

| + | | | ||

| + | |- | ||

| + | |} | ||

| + | |||

| + | === qsf file === | ||

| + | |||

| + | * [https://github.com/douggilliland/Retro-Computers/blob/master/68000/TG68_AMR/TG68_AMR_FPGA/SOC/fpga/QMTECH_CycloneIV_Starter_Kit/SOC.qsf qsf pin file] | ||

<pre> | <pre> | ||

| + | set_global_assignment -name FAMILY "Cyclone IV E" | ||

| + | set_global_assignment -name DEVICE EP4CE15F23C8 | ||

| + | set_global_assignment -name CYCLONEIII_CONFIGURATION_DEVICE EPCQ64 | ||

| + | set_global_assignment -name LAST_QUARTUS_VERSION "20.1.0 Lite Edition" | ||

| + | set_global_assignment -name SMART_RECOMPILE ON | ||

| + | set_global_assignment -name RESERVE_ASDO_AFTER_CONFIGURATION "AS INPUT TRI-STATED" | ||

| + | set_global_assignment -name STRATIX_DEVICE_IO_STANDARD "3.3-V LVTTL" | ||

| + | # Clock, reset button | ||

| + | set_location_assignment PIN_T2 -to clk_50 | ||

| + | set_location_assignment PIN_J4 -to reset_n | ||

| + | set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to reset_n | ||

# Keyboard, Mouse - external card | # Keyboard, Mouse - external card | ||

set_location_assignment PIN_A9 -to ps2k_dat | set_location_assignment PIN_A9 -to ps2k_dat | ||

| Line 50: | Line 574: | ||

set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to rs232_rxd | set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to rs232_rxd | ||

set_location_assignment PIN_B13 -to rs232_txd | set_location_assignment PIN_B13 -to rs232_txd | ||

| − | |||

| − | |||

# SD card - external card | # SD card - external card | ||

set_location_assignment PIN_B14 -to sd_clk | set_location_assignment PIN_B14 -to sd_clk | ||

| Line 58: | Line 580: | ||

set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to sd_miso | set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to sd_miso | ||

set_location_assignment PIN_B15 -to sd_mosi | set_location_assignment PIN_B15 -to sd_mosi | ||

| − | # Power buttons | + | # Power buttons - Pulled-up |

set_location_assignment PIN_C20 -to power_button | set_location_assignment PIN_C20 -to power_button | ||

set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to power_button | set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to power_button | ||

set_location_assignment PIN_D20 -to power_hold | set_location_assignment PIN_D20 -to power_hold | ||

set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to power_hold | set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to power_hold | ||

| − | # LEDs | + | # LEDs - External card |

set_location_assignment PIN_B21 -to leds[3] | set_location_assignment PIN_B21 -to leds[3] | ||

set_location_assignment PIN_B22 -to leds[2] | set_location_assignment PIN_B22 -to leds[2] | ||

set_location_assignment PIN_C21 -to leds[1] | set_location_assignment PIN_C21 -to leds[1] | ||

set_location_assignment PIN_C22 -to leds[0] | set_location_assignment PIN_C22 -to leds[0] | ||

| − | # Audio outputs | + | # Audio outputs on J12 |

| − | set_location_assignment | + | set_location_assignment PIN_B16 -to aud_l |

| − | set_location_assignment | + | set_location_assignment PIN_A16 -to aud_r |

| + | # VGA video - (on-board FPGA card) | ||

| + | set_location_assignment PIN_AA13 -to o_vga_hsync | ||

| + | set_location_assignment PIN_AB10 -to o_vga_vsync | ||

| + | set_location_assignment PIN_AA21 -to o_vga_red[0] | ||

| + | set_location_assignment PIN_AA20 -to o_vga_red[1] | ||

| + | set_location_assignment PIN_AB20 -to o_vga_red[2] | ||

| + | set_location_assignment PIN_AA19 -to o_vga_red[3] | ||

| + | set_location_assignment PIN_AB19 -to o_vga_red[4] | ||

| + | set_location_assignment PIN_AB15 -to o_vga_blue[0] | ||

| + | set_location_assignment PIN_AB14 -to o_vga_blue[1] | ||

| + | set_location_assignment PIN_AA15 -to o_vga_blue[2] | ||

| + | set_location_assignment PIN_AB13 -to o_vga_blue[3] | ||

| + | set_location_assignment PIN_AA14 -to o_vga_blue[4] | ||

| + | set_location_assignment PIN_AB18 -to o_vga_green[0] | ||

| + | set_location_assignment PIN_AA18 -to o_vga_green[1] | ||

| + | set_location_assignment PIN_AA17 -to o_vga_green[2] | ||

| + | set_location_assignment PIN_AB17 -to o_vga_green[3] | ||

| + | set_location_assignment PIN_AA16 -to o_vga_green[4] | ||

| + | set_location_assignment PIN_AB16 -to o_vga_green[5] | ||

| + | # SDRAM (on-board FPGA card) | ||

| + | set_location_assignment PIN_W6 -to o_sdram_cke | ||

| + | set_location_assignment PIN_Y6 -to o_sdram_clk | ||

| + | set_location_assignment PIN_AA3 -to o_sdram_cs | ||

| + | set_location_assignment PIN_AA5 -to o_sdram_ldqm | ||

| + | set_location_assignment PIN_W7 -to o_sdram_udqm | ||

| + | set_location_assignment PIN_AB3 -to o_sdram_ras | ||

| + | set_location_assignment PIN_AA4 -to o_sdram_cas | ||

| + | set_location_assignment PIN_AB4 -to o_sdram_we | ||

| + | set_location_assignment PIN_W2 -to o_sdram_ba[1] | ||

| + | set_location_assignment PIN_Y1 -to o_sdram_ba[0] | ||

| + | set_location_assignment PIN_V6 -to o_sdram_addr[12] | ||

| + | set_location_assignment PIN_Y4 -to o_sdram_addr[11] | ||

| + | set_location_assignment PIN_W1 -to o_sdram_addr[10] | ||

| + | set_location_assignment PIN_V5 -to o_sdram_addr[9] | ||

| + | set_location_assignment PIN_Y3 -to o_sdram_addr[8] | ||

| + | set_location_assignment PIN_AA1 -to o_sdram_addr[7] | ||

| + | set_location_assignment PIN_Y2 -to o_sdram_addr[6] | ||

| + | set_location_assignment PIN_V4 -to o_sdram_addr[5] | ||

| + | set_location_assignment PIN_V3 -to o_sdram_addr[4] | ||

| + | set_location_assignment PIN_U1 -to o_sdram_addr[3] | ||

| + | set_location_assignment PIN_U2 -to o_sdram_addr[2] | ||

| + | set_location_assignment PIN_V1 -to o_sdram_addr[1] | ||

| + | set_location_assignment PIN_V2 -to o_sdram_addr[0] | ||

| + | set_location_assignment PIN_V11 -to io_sdram_data[15] | ||

| + | set_location_assignment PIN_W10 -to io_sdram_data[14] | ||

| + | set_location_assignment PIN_Y10 -to io_sdram_data[13] | ||

| + | set_location_assignment PIN_V10 -to io_sdram_data[12] | ||

| + | set_location_assignment PIN_V9 -to io_sdram_data[11] | ||

| + | set_location_assignment PIN_Y8 -to io_sdram_data[10] | ||

| + | set_location_assignment PIN_W8 -to io_sdram_data[9] | ||

| + | set_location_assignment PIN_Y7 -to io_sdram_data[8] | ||

| + | set_location_assignment PIN_AB5 -to io_sdram_data[7] | ||

| + | set_location_assignment PIN_AA7 -to io_sdram_data[6] | ||

| + | set_location_assignment PIN_AB7 -to io_sdram_data[5] | ||

| + | set_location_assignment PIN_AA8 -to io_sdram_data[4] | ||

| + | set_location_assignment PIN_AB8 -to io_sdram_data[3] | ||

| + | set_location_assignment PIN_AA9 -to io_sdram_data[2] | ||

| + | set_location_assignment PIN_AB9 -to io_sdram_data[1] | ||

| + | set_location_assignment PIN_AA10 -to io_sdram_data[0] | ||

</pre> | </pre> | ||

| + | |||

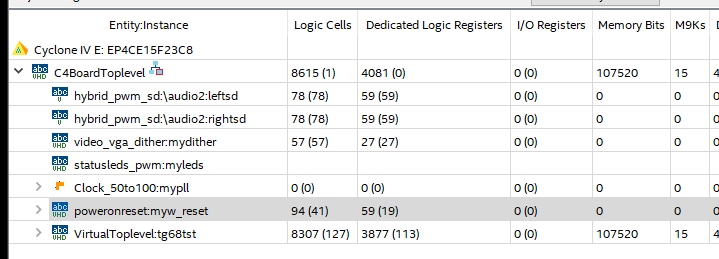

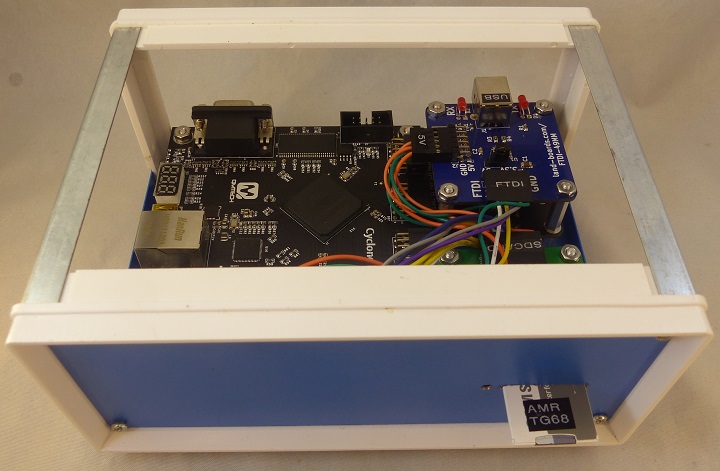

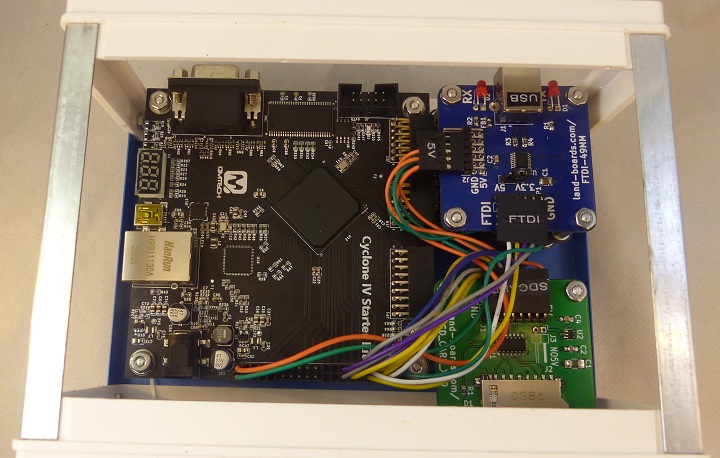

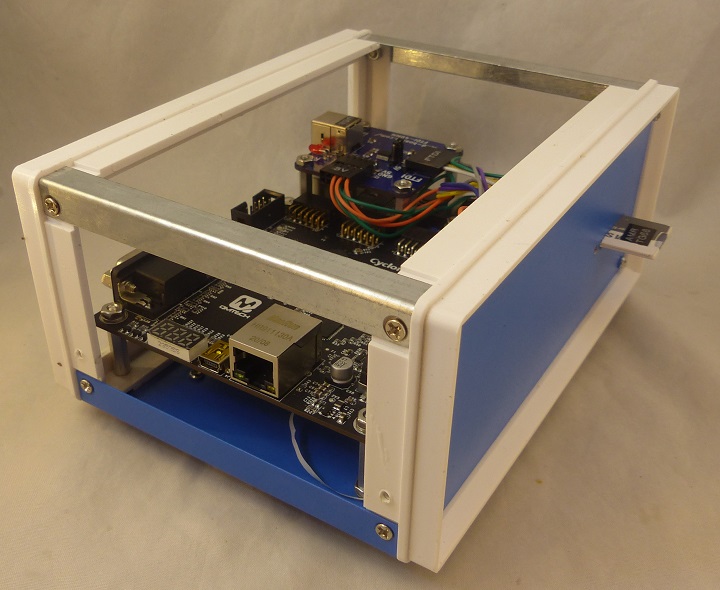

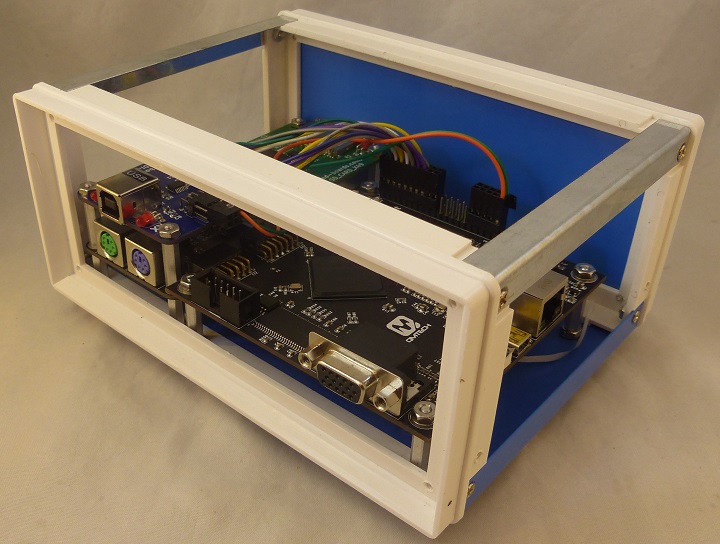

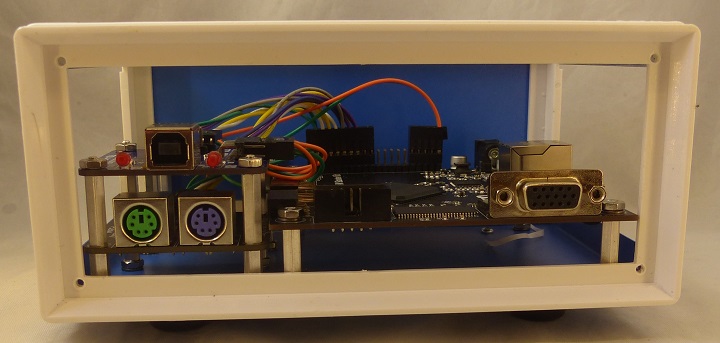

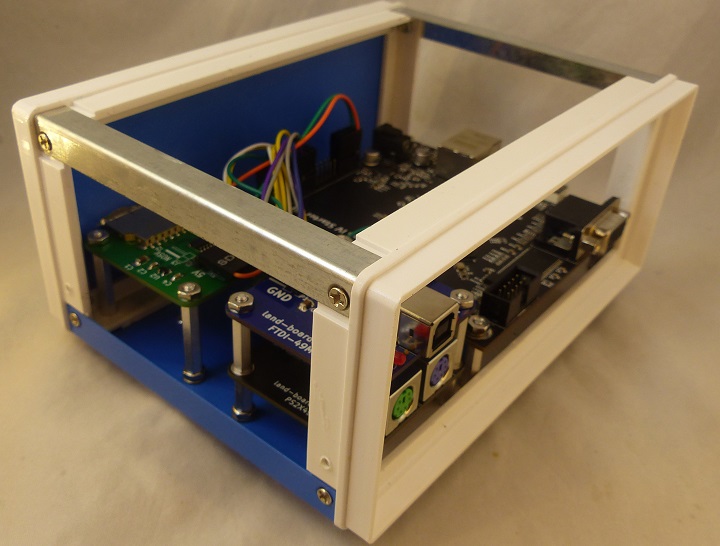

| + | == Chassis == | ||

| + | |||

| + | * Front view | ||

| + | |||

| + | [[file:TG68_AMR_P18123_720PX.jpg]] | ||

| + | |||

| + | * Rear view | ||

| + | |||

| + | [[file:TG68_AMR_P18118_720PX.jpg]] | ||

| + | |||

| + | [[file:Multicomp-Enclosure-P733-720px.jpg]] | ||

| + | |||

| + | [[file:Multicomp-Enclosure-P734-720px.jpg]] | ||

| + | |||

| + | * Top views | ||

| + | |||

| + | [[file:Multicomp-Enclosure-P736-720px.jpg]] | ||

| + | |||

| + | [[file:Multicomp-Enclosure-P737-720px.jpg]] | ||

| + | |||

| + | [[file:Multicomp-Enclosure-P738-720px.jpg]] | ||

| + | |||

| + | * Rear view stackup | ||

| + | |||

| + | [[file:Multicomp-Enclosure-P739-720px.jpg]] | ||

| + | |||

| + | [[file:Multicomp-Enclosure-P740-720px.jpg]] | ||

Latest revision as of 14:10, 26 August 2022

Contents

TG68 AMR Build

TG68 AMR is a 68000 based Computer with a large Video Frame Buffer.

- Hackaday Project page

- QMTECH EP4CE15 Standalone Board

- 68000 CPU

- VGA (5:6:5)

- 32 MB SDRAM

- Land Boards SD Card

- FAT32 format (used 8 GB standard SD card)

- Land Boards FTDI Card

- USB to Serial

- 115,200 baud, n,8,1, no handshake

- Land Boards PS/2 card

- Mouse/keyboard

- Stereo Output

- YaeCCC Rectangle Project Enclosure Case Electric Junction Box Blue

- 170mm x 130mm x 80mm / 6.4" x 4.3" x 2.7"

Credits

Original design by Alastair M. Robinson referred to by his initials AMR.

Performance

- VAX MIPS rating * 1000 = 4773 (4.77 MIPS)

PuTTY Setup

- Terminal

- Implicit CR in every LF

- Implicit LF in every CR

- Window - Appearance

- Window Title: COMxx_TG68_AMR

- Connection - Serial

- No hardware handshake

J12 - I/O Connector

Wiring

Software

Demo

- Demo GitHub Repo

- Load boot.sre to FAT32 formatted SD card

- Load test.img to SD card

- Insert SD card

- Turn on (plug in USB power cable)

- Press F1-F9,F12 for demos

VHDL Code

Resources

Pin List

| To | Direction | Location | I/O Standard | Pull-Up |

|---|---|---|---|---|

| aud_l | Output | PIN_B16 | 3.3-V LVTTL | |

| aud_r | Output | PIN_A16 | 3.3-V LVTTL | |

| clk_50 | Input | PIN_T2 | 3.3-V LVTTL | |

| io_sdram_data[15] | Bidir | PIN_V11 | 3.3-V LVTTL | |

| io_sdram_data[14] | Bidir | PIN_W10 | 3.3-V LVTTL | |

| io_sdram_data[13] | Bidir | PIN_Y10 | 3.3-V LVTTL | |

| io_sdram_data[12] | Bidir | PIN_V10 | 3.3-V LVTTL | |

| io_sdram_data[11] | Bidir | PIN_V9 | 3.3-V LVTTL | |

| io_sdram_data[10] | Bidir | PIN_Y8 | 3.3-V LVTTL | |

| io_sdram_data[9] | Bidir | PIN_W8 | 3.3-V LVTTL | |

| io_sdram_data[8] | Bidir | PIN_Y7 | 3.3-V LVTTL | |

| io_sdram_data[7] | Bidir | PIN_AB5 | 3.3-V LVTTL | |

| io_sdram_data[6] | Bidir | PIN_AA7 | 3.3-V LVTTL | |

| io_sdram_data[5] | Bidir | PIN_AB7 | 3.3-V LVTTL | |

| io_sdram_data[4] | Bidir | PIN_AA8 | 3.3-V LVTTL | |

| io_sdram_data[3] | Bidir | PIN_AB8 | 3.3-V LVTTL | |

| io_sdram_data[2] | Bidir | PIN_AA9 | 3.3-V LVTTL | |

| io_sdram_data[1] | Bidir | PIN_AB9 | 3.3-V LVTTL | |

| io_sdram_data[0] | Bidir | PIN_AA10 | 3.3-V LVTTL | |

| leds[3] | Output | PIN_B21 | 3.3-V LVTTL | |

| leds[2] | Output | PIN_B22 | 3.3-V LVTTL | |

| leds[1] | Output | PIN_C21 | 3.3-V LVTTL | |

| leds[0] | Output | PIN_C22 | 3.3-V LVTTL | |

| o_sdram_addr[12] | Output | PIN_V6 | 3.3-V LVTTL | |

| o_sdram_addr[11] | Output | PIN_Y4 | 3.3-V LVTTL | |

| o_sdram_addr[10] | Output | PIN_W1 | 3.3-V LVTTL | |

| o_sdram_addr[9] | Output | PIN_V5 | 3.3-V LVTTL | |

| o_sdram_addr[8] | Output | PIN_Y3 | 3.3-V LVTTL | |

| o_sdram_addr[7] | Output | PIN_AA1 | 3.3-V LVTTL | |

| o_sdram_addr[6] | Output | PIN_Y2 | 3.3-V LVTTL | |

| o_sdram_addr[5] | Output | PIN_V4 | 3.3-V LVTTL | |

| o_sdram_addr[4] | Output | PIN_V3 | 3.3-V LVTTL | |

| o_sdram_addr[3] | Output | PIN_U1 | 3.3-V LVTTL | |

| o_sdram_addr[2] | Output | PIN_U2 | 3.3-V LVTTL | |

| o_sdram_addr[1] | Output | PIN_V1 | 3.3-V LVTTL | |

| o_sdram_addr[0] | Output | PIN_V2 | 3.3-V LVTTL | |

| o_sdram_ba[1] | Output | PIN_W2 | 3.3-V LVTTL | |

| o_sdram_ba[0] | Output | PIN_Y1 | 3.3-V LVTTL | |

| o_sdram_cas | Output | PIN_AA4 | 3.3-V LVTTL | |

| o_sdram_cke | Output | PIN_W6 | 3.3-V LVTTL | |

| o_sdram_clk | Output | PIN_Y6 | 3.3-V LVTTL | |

| o_sdram_cs | Output | PIN_AA3 | 3.3-V LVTTL | |

| o_sdram_ldqm | Output | PIN_AA5 | 3.3-V LVTTL | |

| o_sdram_ras | Output | PIN_AB3 | 3.3-V LVTTL | |

| o_sdram_udqm | Output | PIN_W7 | 3.3-V LVTTL | |

| o_sdram_we | Output | PIN_AB4 | 3.3-V LVTTL | |

| o_vga_blue[4] | Output | PIN_AA14 | 3.3-V LVTTL | |

| o_vga_blue[3] | Output | PIN_AB13 | 3.3-V LVTTL | |

| o_vga_blue[2] | Output | PIN_AA15 | 3.3-V LVTTL | |

| o_vga_blue[1] | Output | PIN_AB14 | 3.3-V LVTTL | |

| o_vga_blue[0] | Output | PIN_AB15 | 3.3-V LVTTL | |

| o_vga_green[5] | Output | PIN_AB16 | 3.3-V LVTTL | |

| o_vga_green[4] | Output | PIN_AA16 | 3.3-V LVTTL | |

| o_vga_green[3] | Output | PIN_AB17 | 3.3-V LVTTL | |

| o_vga_green[2] | Output | PIN_AA17 | 3.3-V LVTTL | |

| o_vga_green[1] | Output | PIN_AA18 | 3.3-V LVTTL | |

| o_vga_green[0] | Output | PIN_AB18 | 3.3-V LVTTL | |

| o_vga_hsync | Output | PIN_AA13 | 3.3-V LVTTL | |

| o_vga_red[4] | Output | PIN_AB19 | 3.3-V LVTTL | |

| o_vga_red[3] | Output | PIN_AA19 | 3.3-V LVTTL | |

| o_vga_red[2] | Output | PIN_AB20 | 3.3-V LVTTL | |

| o_vga_red[1] | Output | PIN_AA20 | 3.3-V LVTTL | |

| o_vga_red[0] | Output | PIN_AA21 | 3.3-V LVTTL | |

| o_vga_vsync | Output | PIN_AB10 | 3.3-V LVTTL | |

| power_button | Input | PIN_C20 | 3.3-V LVTTL | on |

| power_hold | Output | PIN_D20 | 3.3-V LVTTL | on |

| ps2k_clk | Bidir | PIN_A10 | 3.3-V LVTTL | on |

| ps2k_dat | Bidir | PIN_A9 | 3.3-V LVTTL | on |

| ps2m_clk | Bidir | PIN_B10 | 3.3-V LVTTL | on |

| ps2m_dat | Bidir | PIN_B9 | 3.3-V LVTTL | on |

| reset_n | Input | PIN_J4 | 3.3-V LVTTL | on |

| rs232_rxd | Input | PIN_A13 | 3.3-V LVTTL | on |

| rs232_txd | Output | PIN_B13 | 3.3-V LVTTL | |

| sd_clk | Output | PIN_B14 | 3.3-V LVTTL | |

| sd_cs | Output | PIN_A14 | 3.3-V LVTTL | |

| sd_miso | Input | PIN_A15 | 3.3-V LVTTL | on |

| sd_mosi | Output | PIN_B15 | 3.3-V LVTTL |

qsf file

set_global_assignment -name FAMILY "Cyclone IV E" set_global_assignment -name DEVICE EP4CE15F23C8 set_global_assignment -name CYCLONEIII_CONFIGURATION_DEVICE EPCQ64 set_global_assignment -name LAST_QUARTUS_VERSION "20.1.0 Lite Edition" set_global_assignment -name SMART_RECOMPILE ON set_global_assignment -name RESERVE_ASDO_AFTER_CONFIGURATION "AS INPUT TRI-STATED" set_global_assignment -name STRATIX_DEVICE_IO_STANDARD "3.3-V LVTTL" # Clock, reset button set_location_assignment PIN_T2 -to clk_50 set_location_assignment PIN_J4 -to reset_n set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to reset_n # Keyboard, Mouse - external card set_location_assignment PIN_A9 -to ps2k_dat set_location_assignment PIN_A10 -to ps2k_clk set_location_assignment PIN_B10 -to ps2m_clk set_location_assignment PIN_B9 -to ps2m_dat set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to ps2k_clk set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to ps2k_dat set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to ps2m_clk set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to ps2m_dat # Serial - external card set_location_assignment PIN_A13 -to rs232_rxd set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to rs232_rxd set_location_assignment PIN_B13 -to rs232_txd # SD card - external card set_location_assignment PIN_B14 -to sd_clk set_location_assignment PIN_A14 -to sd_cs set_location_assignment PIN_A15 -to sd_miso set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to sd_miso set_location_assignment PIN_B15 -to sd_mosi # Power buttons - Pulled-up set_location_assignment PIN_C20 -to power_button set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to power_button set_location_assignment PIN_D20 -to power_hold set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to power_hold # LEDs - External card set_location_assignment PIN_B21 -to leds[3] set_location_assignment PIN_B22 -to leds[2] set_location_assignment PIN_C21 -to leds[1] set_location_assignment PIN_C22 -to leds[0] # Audio outputs on J12 set_location_assignment PIN_B16 -to aud_l set_location_assignment PIN_A16 -to aud_r # VGA video - (on-board FPGA card) set_location_assignment PIN_AA13 -to o_vga_hsync set_location_assignment PIN_AB10 -to o_vga_vsync set_location_assignment PIN_AA21 -to o_vga_red[0] set_location_assignment PIN_AA20 -to o_vga_red[1] set_location_assignment PIN_AB20 -to o_vga_red[2] set_location_assignment PIN_AA19 -to o_vga_red[3] set_location_assignment PIN_AB19 -to o_vga_red[4] set_location_assignment PIN_AB15 -to o_vga_blue[0] set_location_assignment PIN_AB14 -to o_vga_blue[1] set_location_assignment PIN_AA15 -to o_vga_blue[2] set_location_assignment PIN_AB13 -to o_vga_blue[3] set_location_assignment PIN_AA14 -to o_vga_blue[4] set_location_assignment PIN_AB18 -to o_vga_green[0] set_location_assignment PIN_AA18 -to o_vga_green[1] set_location_assignment PIN_AA17 -to o_vga_green[2] set_location_assignment PIN_AB17 -to o_vga_green[3] set_location_assignment PIN_AA16 -to o_vga_green[4] set_location_assignment PIN_AB16 -to o_vga_green[5] # SDRAM (on-board FPGA card) set_location_assignment PIN_W6 -to o_sdram_cke set_location_assignment PIN_Y6 -to o_sdram_clk set_location_assignment PIN_AA3 -to o_sdram_cs set_location_assignment PIN_AA5 -to o_sdram_ldqm set_location_assignment PIN_W7 -to o_sdram_udqm set_location_assignment PIN_AB3 -to o_sdram_ras set_location_assignment PIN_AA4 -to o_sdram_cas set_location_assignment PIN_AB4 -to o_sdram_we set_location_assignment PIN_W2 -to o_sdram_ba[1] set_location_assignment PIN_Y1 -to o_sdram_ba[0] set_location_assignment PIN_V6 -to o_sdram_addr[12] set_location_assignment PIN_Y4 -to o_sdram_addr[11] set_location_assignment PIN_W1 -to o_sdram_addr[10] set_location_assignment PIN_V5 -to o_sdram_addr[9] set_location_assignment PIN_Y3 -to o_sdram_addr[8] set_location_assignment PIN_AA1 -to o_sdram_addr[7] set_location_assignment PIN_Y2 -to o_sdram_addr[6] set_location_assignment PIN_V4 -to o_sdram_addr[5] set_location_assignment PIN_V3 -to o_sdram_addr[4] set_location_assignment PIN_U1 -to o_sdram_addr[3] set_location_assignment PIN_U2 -to o_sdram_addr[2] set_location_assignment PIN_V1 -to o_sdram_addr[1] set_location_assignment PIN_V2 -to o_sdram_addr[0] set_location_assignment PIN_V11 -to io_sdram_data[15] set_location_assignment PIN_W10 -to io_sdram_data[14] set_location_assignment PIN_Y10 -to io_sdram_data[13] set_location_assignment PIN_V10 -to io_sdram_data[12] set_location_assignment PIN_V9 -to io_sdram_data[11] set_location_assignment PIN_Y8 -to io_sdram_data[10] set_location_assignment PIN_W8 -to io_sdram_data[9] set_location_assignment PIN_Y7 -to io_sdram_data[8] set_location_assignment PIN_AB5 -to io_sdram_data[7] set_location_assignment PIN_AA7 -to io_sdram_data[6] set_location_assignment PIN_AB7 -to io_sdram_data[5] set_location_assignment PIN_AA8 -to io_sdram_data[4] set_location_assignment PIN_AB8 -to io_sdram_data[3] set_location_assignment PIN_AA9 -to io_sdram_data[2] set_location_assignment PIN_AB9 -to io_sdram_data[1] set_location_assignment PIN_AA10 -to io_sdram_data[0]

Chassis

- Front view

- Rear view

- Top views

- Rear view stackup