Difference between revisions of "LB-65CXX-01"

Jump to navigation

Jump to search

Blwikiadmin (talk | contribs) (→Rev 1) |

Blwikiadmin (talk | contribs) |

||

| (122 intermediate revisions by the same user not shown) | |||

| Line 1: | Line 1: | ||

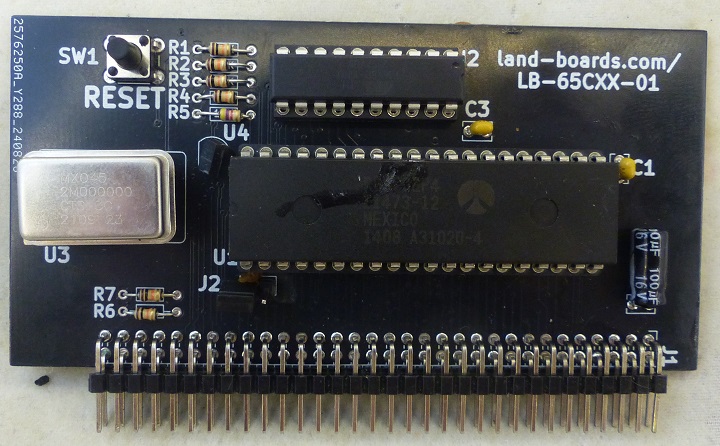

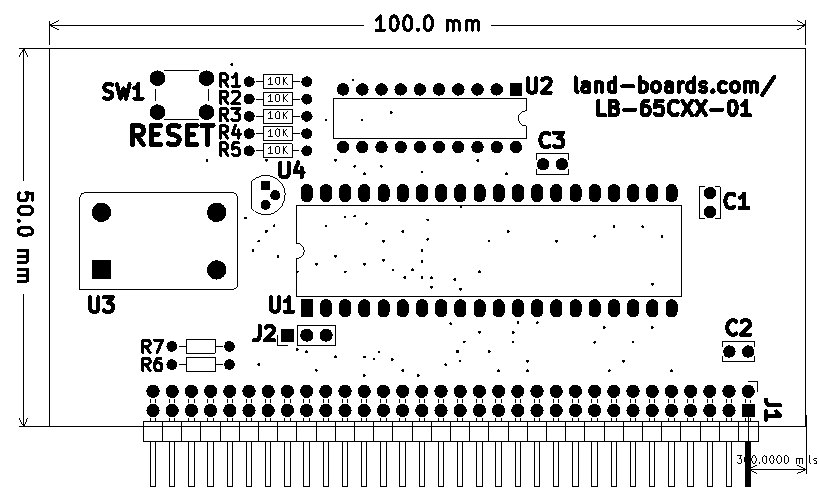

| − | [[file:LB- | + | [[file:LB-65CXX-01_P1090724-720px.jpg]] |

== Features == | == Features == | ||

| Line 16: | Line 16: | ||

0x0000-0x7FFF - 32KB SRAM | 0x0000-0x7FFF - 32KB SRAM | ||

0x8000-0x8FFF - 4KB I/O space | 0x8000-0x8FFF - 4KB I/O space | ||

| − | 0x9000-0xBFFF - 12 KB SRAM | + | 0x9000-0xBFFF - Free space (12 KB SRAM Using 128KB SRAM) |

0xC000-0xFFFF - 16KB EPROM space | 0xC000-0xFFFF - 16KB EPROM space | ||

</pre> | </pre> | ||

| Line 25: | Line 25: | ||

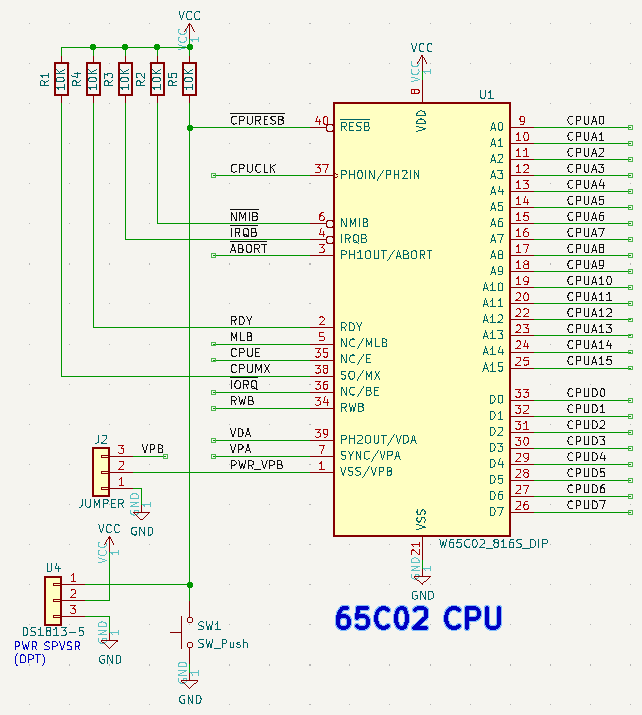

* 65C02 or 65C816 CPU | * 65C02 or 65C816 CPU | ||

| + | ** 65C816 requires mods to the PCB (see Checkout notes below) or Rev 2 PCB | ||

* 2 MHz | * 2 MHz | ||

* Install jumper J2:1-2 if CPU is not a WDC 65C02 or WDC 65C816 | * Install jumper J2:1-2 if CPU is not a WDC 65C02 or WDC 65C816 | ||

| − | ==== R65C02 vs W65C02 CPUs ==== | + | ==== R65C02 vs W65C02 vs W65C816 CPUs ==== |

| − | + | {| class="wikitable" | |

| + | ! U1 Pin | ||

| + | ! U1 Pin Name | ||

| + | ! Sig Name | ||

| + | ! Pullup | ||

| + | ! R65C02 sig | ||

| + | ! W65C02 sig | ||

| + | ! W65C816 sig | ||

| + | |- | ||

| + | | 1 | ||

| + | | VSS/VPB | ||

| + | | J2 selects | ||

| + | | N | ||

| + | | VSS (IN) | ||

| + | | VPB (OUT) | ||

| + | | VPB (OUT) | ||

| + | |- | ||

| + | | 3 | ||

| + | | PH1OUT/ABORT | ||

| + | | ABORT* | ||

| + | | REV2 | ||

| + | | PH1OUT (OUT) | ||

| + | | PH1OUT (OUT) | ||

| + | | ABORT (IN) | ||

| + | |- | ||

| + | | 5 | ||

| + | | NC/MLB | ||

| + | | MLB | ||

| + | | N | ||

| + | | NC | ||

| + | | MLB (OUT) | ||

| + | | MLB (OUT) | ||

| + | |- | ||

| + | | 7 | ||

| + | | SYNC/VPA | ||

| + | | VPA | ||

| + | | N | ||

| + | | SYNC (OUT) | ||

| + | | SYNC (OUT) | ||

| + | | VPA (OUT) | ||

| + | |- | ||

| + | | 35 | ||

| + | | NC/E | ||

| + | | CPUE | ||

| + | | N | ||

| + | | NC | ||

| + | | NC | ||

| + | | EM/NAT (OUT) | ||

| + | |- | ||

| + | | 36 | ||

| + | | NC/BE | ||

| + | | IORQ* | ||

| + | | REV2 | ||

| + | | NC | ||

| + | | BE (IN) | ||

| + | | BE (IN) | ||

| + | |- | ||

| + | | 37 | ||

| + | | PH0IN/PH2IN | ||

| + | | CPUCLK | ||

| + | | N | ||

| + | | PH0IN | ||

| + | | PH2IN | ||

| + | | PH2IN | ||

| + | |- | ||

| + | | 38 | ||

| + | | SO/MX | ||

| + | | CPUMX | ||

| + | | REV1/2 | ||

| + | | SO* (IN) | ||

| + | | SOB (IN) | ||

| + | | MX (OUT) | ||

| + | |- | ||

| + | | 39 | ||

| + | | PH2OUT/VDA | ||

| + | | VDA | ||

| + | | N | ||

| + | | PH2OUT (OUT) | ||

| + | | PH2OUT (OUT) | ||

| + | | VDA (OUT) | ||

| + | |- | ||

| + | |} | ||

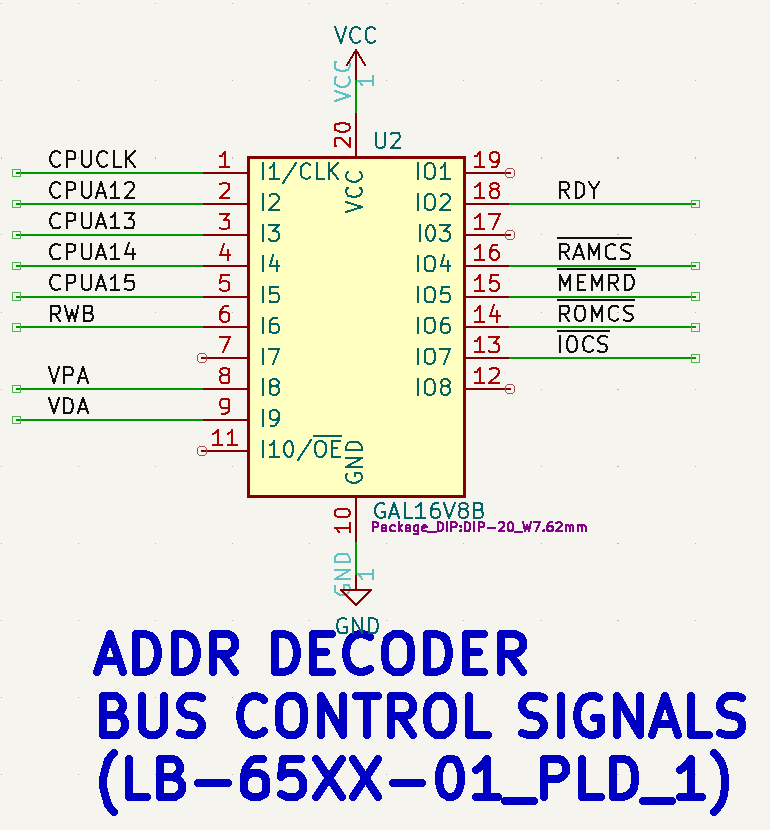

| − | + | [[file:R65C02_vs_W65C02_w65c816_Pinout_800PX.png]] | |

| − | * | + | ===== VDA/VPA (65C816) ===== |

| − | ** | + | |

| − | ** | + | * VDA/VDA |

| − | * | + | ** 00, Internal operation (invalid address bus) |

| − | ** | + | ** 01, Valid Program Address |

| − | ** | + | ** 10, Valid Data Address |

| − | * | + | ** 11, Opcode-fetch |

| − | * | + | |

| − | + | === Chip Set === | |

| + | |||

| + | * [https://www.ebay.com/itm/114007713791 Ordered from Ebay] | ||

| + | |||

| + | [[file:LB_65C02_PARTS.jpg]] | ||

| + | |||

| + | * Picture shows 3 MHz CPU | ||

| + | * Received 2 MHz CPU | ||

| + | * As received: | ||

| + | |||

| + | [[file:SIMPLE-6502_P1090155-720px.jpg]] | ||

=== Oscillator === | === Oscillator === | ||

| Line 49: | Line 141: | ||

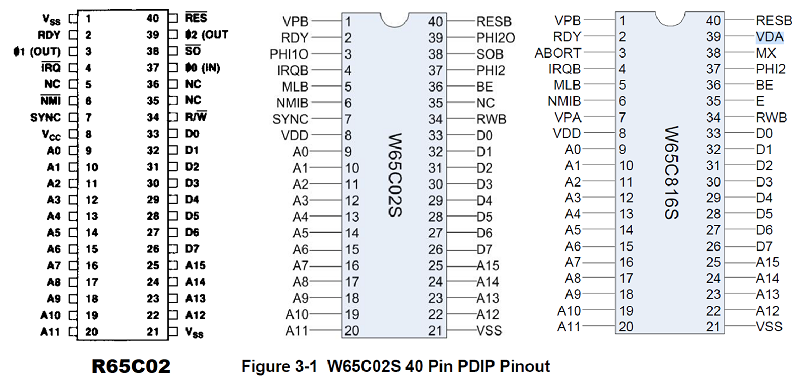

=== PLD === | === PLD === | ||

| + | |||

| + | * ATF16V8B part | ||

| + | * [[TL866ii Plus Programmer]] | ||

[[file:LB-65CXX-01_PLS.PNG]] | [[file:LB-65CXX-01_PLS.PNG]] | ||

=== PLD Listing === | === PLD Listing === | ||

| + | |||

| + | * [https://github.com/land-boards/lb-boards/blob/master/RetroCPUs/LB-RETRO-SET/LB-65CXX-01/LOGIC/LB-65CXX-01_PLD.PLD PLD File] | ||

<pre> | <pre> | ||

Name LB-65CXX-01_PLD; | Name LB-65CXX-01_PLD; | ||

Partno ATF16V8B; | Partno ATF16V8B; | ||

| − | Date | + | Date 09/12/24; |

Revision 01; | Revision 01; | ||

Designer DOUG G; | Designer DOUG G; | ||

| Line 66: | Line 163: | ||

/* | /* | ||

| − | + | 65C02 Control | |

*/ | */ | ||

| − | |||

/* Control inputs */ | /* Control inputs */ | ||

| Line 78: | Line 174: | ||

PIN 6 = CPUREAD; | PIN 6 = CPUREAD; | ||

PIN 8 = VPA; | PIN 8 = VPA; | ||

| − | PIN 9 = VDA; | + | PIN 9 = VDA; /* Pin 39, PH2OUT - Enable line */ |

| − | /* | + | /* Address Decode and Chip Select outputs */ |

PIN 13 = !IOCS; | PIN 13 = !IOCS; | ||

PIN 14 = !ROMCS; | PIN 14 = !ROMCS; | ||

| Line 87: | Line 183: | ||

PIN 18 = RDY; | PIN 18 = RDY; | ||

| − | RAMCS = !CPUA15 & | + | RAMCS = !CPUA15 & CPUREAD /* 0x0000-0x7FFF */ |

| − | # | + | # !CPUA15 & !CPUREAD & VDA; |

| − | |||

| − | IOCS = CPUA15 & !CPUA14 & | + | IOCS = CPUA15 & !CPUA14 & CPUA13 & !CPUA12 & CPUREAD /* 0x8000-0x8FFF */ |

| + | # CPUA15 & !CPUA14 & CPUA13 & !CPUA12 & !CPUREAD & VDA; | ||

| − | ROMCS = CPUA15 & CPUA14 & CPUREAD | + | ROMCS = CPUA15 & CPUA14 & CPUREAD; /* 0xC000-0xFFFF (16KB space) */ |

| − | + | RDY = VDA; | |

| − | + | MEMRD = CPUREAD; | |

| − | |||

| − | |||

| − | |||

</pre> | </pre> | ||

| Line 115: | Line 208: | ||

[[file:LB-65CXX-01_BKPL.PNG]] | [[file:LB-65CXX-01_BKPL.PNG]] | ||

| + | |||

| + | == Software == | ||

| + | |||

| + | * [https://github.com/douggilliland/Retro-Computers/tree/master/6502/LB-6502 LB-6502 GitHub] | ||

| + | * [[SIMPLE-6502#Software|SIMPLE-6502 Software]] - Reference software | ||

| + | |||

| + | === Assembly Language Development Toolchain === | ||

| + | |||

| + | * [https://cc65.github.io/ cc65 Assembler, Linker, Compiler] | ||

| + | ** [https://github.com/douggilliland/Retro-Computers/tree/master/6502/LB-6502 Backup copy] | ||

| + | * [https://github.com/douggilliland/Retro-Computers/blob/master/6502/LB-6502/AciaTest/AciaTest.bat Example batch file] to assemble code and produce .hex file | ||

| + | |||

| + | <pre> | ||

| + | ca65 AciaTest.s -o AciaTest.o -l | ||

| + | ld65 -C AciaTest.cfg AciaTest.o -o AciaTest.bin | ||

| + | srec_cat.exe AciaTest.bin -binary -o AciaTest.hex -Intel | ||

| + | </pre> | ||

| + | |||

| + | * [https://github.com/douggilliland/Retro-Computers/blob/master/6502/LB-6502/AciaTest/AciaTest.cfg AciaTest.cfg] | ||

| + | |||

| + | <pre> | ||

| + | MEMORY { | ||

| + | ROM: start = $C000, size = $3FFA, fill = yes, fillval=$FF, file = %O; | ||

| + | VECTS: start = $FFFA, size = $6, fill = yes, fillval=$FF, file = %O; | ||

| + | } | ||

| + | |||

| + | SEGMENTS { | ||

| + | CODE: load = ROM, type = ro; | ||

| + | VECTS: load = VECTS, type = ro; | ||

| + | } | ||

| + | </pre> | ||

| + | |||

| + | === ACIA Test Code === | ||

| + | |||

| + | * [https://github.com/douggilliland/Retro-Computers/blob/master/6502/LB-6502/AciaTest/AciaTest.s ACIATest.s] | ||

| + | * Loopback serial data | ||

| + | * Works | ||

| + | |||

| + | === Simple Monitor 6502 === | ||

| + | |||

| + | * [https://raw.githubusercontent.com/douggilliland/Retro-Computers/master/6502/LB-6502/SimpleMon6502/SimpleMon6502.s SimpleMon6502.s] - GitHub repo | ||

| + | * Contains | ||

| + | ** ACIA init, read, write | ||

| + | ** Simplest commands mostly for function development | ||

| + | ** String functions | ||

| + | *** Read a string | ||

| + | *** Write a string (macro) | ||

| + | *** Write hex value as a string | ||

| + | * Dump page (256-bytes) of memory | ||

| + | |||

| + | === 6502 Enhanced BASIC === | ||

| + | |||

| + | * [https://github.com/douggilliland/Retro-Computers/tree/master/6502/LB-6502/EnhBASIC-6502 Enhanced BASIC Source Code on GitHub] | ||

| + | * Free space using [[LB-MEM-02]] card | ||

| + | |||

| + | <pre> | ||

| + | ?FRE(0) | ||

| + | 31999 | ||

| + | </pre> | ||

| + | |||

| + | ==== Enhanced BASIC Bug Fixes ==== | ||

| + | |||

| + | * [https://raw.githubusercontent.com/douggilliland/Retro-Computers/master/6502/LB-6502/EnhBASIC-6502/bugsnquirks.txt Enhanced BASIC Quirks and fixes] | ||

| + | ** Fixes the IRQ_vec missing error when assembling the code | ||

| + | |||

| + | <pre> | ||

| + | ; Ibuffs can now be anywhere in RAM, ensure that the max length is < $80, | ||

| + | ; the input buffer must not cross a page boundary and must not overlap with | ||

| + | ; program RAM pages! | ||

| + | |||

| + | ;Ibuffs = IRQ_vec+$14 | ||

| + | Ibuffs = VEC_SV+$16 | ||

| + | ; start of input buffer after IRQ/NMI code | ||

| + | Ibuffe = Ibuffs+$47; end of input buffer | ||

| + | </pre> | ||

| + | |||

| + | * Added some of the patches from [https://raw.githubusercontent.com/douggilliland/Retro-Computers/master/6502/LB-6502/EnhBASIC-6502/bugsnquirks.txt Enhanced BASIC Quirks and fixes] | ||

| + | ** [https://github.com/douggilliland/Retro-Computers/tree/master/6502/LB-6502/EnhBASIC-6502/Patched Patched code is here] | ||

| + | |||

| + | * Boots to request memory size | ||

| + | |||

| + | [[FILE:EnhBASIC_BOOT.PNG]] | ||

| + | |||

| + | * Runs on card | ||

| + | |||

| + | [[FILE:EnhBASIC_LOOP.PNG]] | ||

| + | |||

| + | === OSI BASIC === | ||

| + | |||

| + | * [https://github.com/douggilliland/Retro-Computers/tree/master/6502/LB-6502 LB-6502 GitHub] | ||

| + | ** Generated from [https://github.com/mist64/msbasic msbasic Source Code] | ||

| + | * Grant Searle's 6502 design | ||

| + | ** [http://searle.x10host.com/6502/osi_bas.zip Link to Grant's files] | ||

| + | ** [https://github.com/douggilliland/Retro-Computers/tree/master/6502/LB-6502/OSI_BAS Local copy] | ||

| + | * Source code | ||

| + | ** [https://github.com/douggilliland/Retro-Computers/blob/master/6502/LB-6502/OSI_BAS/osi_bas.s osi_bas.s] <== the Microsoft OSI BASIC and I/O routines SOURCE all in a single file | ||

| + | ** Grant's I/O routines are at the end of it | ||

| + | * Files to allow the source to be assembled on a Windows based machine | ||

| + | ** assemble.bat <== double click to assemble osi_bas.s and link to binary file "osi_bas.bin" | ||

| + | ** This should be exactly 16K | ||

| + | ** [https://github.com/douggilliland/Retro-Computers/blob/master/6502/LB-6502/OSI_BAS/osi_bas.cfg osi_bas.cfg] <== configuration file for the linker (ensure ORG and entries in this file match if you change any) | ||

| + | ** ca65.exe <== the assembler from the cc65 package. Use this. The new version on the cc65 site crashes! | ||

| + | ** ld65.exe <== linker from the cc65 package | ||

| + | ** srec_cat.exe <== Converts bin file to .hex file | ||

| + | * Output files | ||

| + | ** osi_bas.bin <== the ROM fine in pure binary | ||

| + | ** osi_bas.lst <== Assembly listing file | ||

| + | ** rom.hex <== the ROM fine in standard INTEL-HEX format | ||

| + | * To allow simple re-assembly, extract all files to the same folder | ||

| + | ** Use srec_cat utility to convert the "bin" file to HEX or s19 (etc) | ||

| + | * All source code, assembler binaries and the HEX dump of the ROM is [http://searle.x10host.com/6502/osi_bas.zip here] | ||

| + | ** It is in standard INTEL-HEX format for uploading to a suitable programmer. | ||

| + | * Having trouble running code | ||

| + | |||

| + | ==== Hacking MBASIC ==== | ||

| + | |||

| + | * [https://www.pagetable.com/?p=46 Create your own Version of Microsoft BASIC for 6502] | ||

| + | |||

| + | <video type="youtube">gOwi2p1pzVM</video> | ||

| + | |||

| + | === VLT-2 for 6502 === | ||

| + | |||

| + | * [http://forum.6502.org/viewtopic.php?p=41243#p41243 VTL02 (VTL-2 for the 6502) by Mike Barry] - on the 6502.org site | ||

| + | * [https://github.com/Klaus2m5/VTL02 Klaus's repo] | ||

| + | * [https://github.com/douggilliland/Retro-Computers/tree/master/6502/VTL-2 VTL-2 GitHub] | ||

| + | * [http://forum.6502.org/viewtopic.php?p=41243#p41243 Thread about improvements to VLT-2] | ||

| + | * [https://github.com/douggilliland/Retro-Computers/blob/master/6502/VTL-2/Altair_680-VTL-2%20Manual-05-Beta_1-Searchable.pdf VTL-2 Manual] | ||

| + | |||

| + | === Programming References === | ||

| + | |||

| + | ==== 6502 Instruction Set ==== | ||

| + | |||

| + | * [http://www.6502.org/users/obelisk/6502/instructions.html#:~:text=The%20Instruction%20Set.%20The%206502%20has%20a%20relatively%20basic%20set#:~:text=The%20Instruction%20Set.%20The%206502%20has%20a%20relatively%20basic%20set The 6502 Instruction Set] | ||

| + | * [https://retrogamecoders.com/6502-processor/ 6502 Programmer’s Reference] | ||

| + | * [https://6502-toolchain.readthedocs.io/en/latest/isa_reference/index.html 65(c)02 Instruction Set Reference] | ||

| + | * [https://c64os.com/post/6502instructions#:~:text=6502%20/%206510%20Instruction%20Set%20Every%20Commodore%2064%20programmer%20should 6502 / 6510 Instruction Set] | ||

| + | |||

| + | === Additional Tools === | ||

| + | |||

| + | * [https://kh-labs.org/6502/ 6502 Emulator] - Simple emulator but it works | ||

| + | * [https://www.masswerk.at/6502/index.html virtual 6502 / Emulator] | ||

| + | * [http://www.6502.org/tools/asm/ 6502.org Tools for the 6502] | ||

| + | ** [https://6502-toolchain.readthedocs.io/en/latest/isa_reference/index.html Cross development package for 65(C)02 systems, including a powerful macro assembler, a C compiler, linker, librarian and several other tools] | ||

== Mechanicals == | == Mechanicals == | ||

| − | [[file:LB-665CXX- | + | [[file:LB-665CXX-01_REV2_MECHS.PNG]] |

== Checkout == | == Checkout == | ||

| − | === Rev 1 ============= | + | === Rev 3 === |

| + | |||

| + | ==== PCB Updates ==== | ||

| + | |||

| + | * Add bulk electrolytic cap | ||

| + | * Make PH2OUT on VPB backplane line (swap wth VDA) | ||

| + | * Change to vertical reset switch | ||

| + | * Add an LED that is written by writing D0 to ROM area | ||

| + | |||

| + | === Rev 2 === | ||

| + | |||

| + | ==== Rev 2 Checkout ==== | ||

| + | |||

| + | * Install jumper J2:1-2 since CPU is R65C02 | ||

| + | * [http://land-boards.com/blwiki/index.php?title=LB-BKOUT-01#NOP_Tester NOP tester] - 6502 nop = 0xEA | ||

| + | ** Works | ||

| + | * Add LED | ||

| + | ** 1.8K resistor from U2-17 to Ground | ||

| + | ** Wire U2-11 to U1-33 CPUD0 | ||

| + | |||

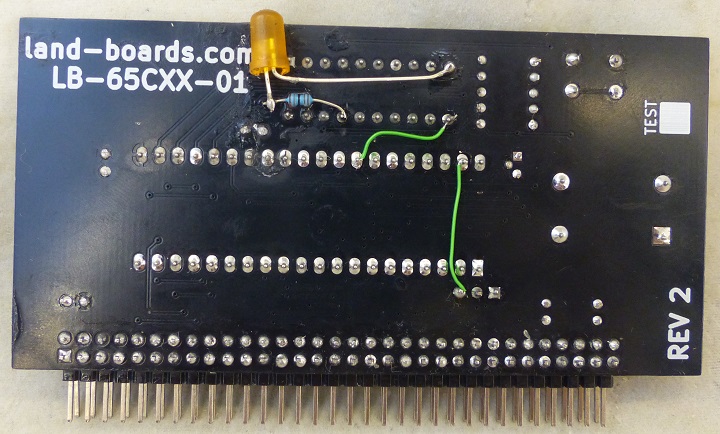

| + | [[file:LB-65CXX-01_P1090727-720px.jpg]] | ||

| + | |||

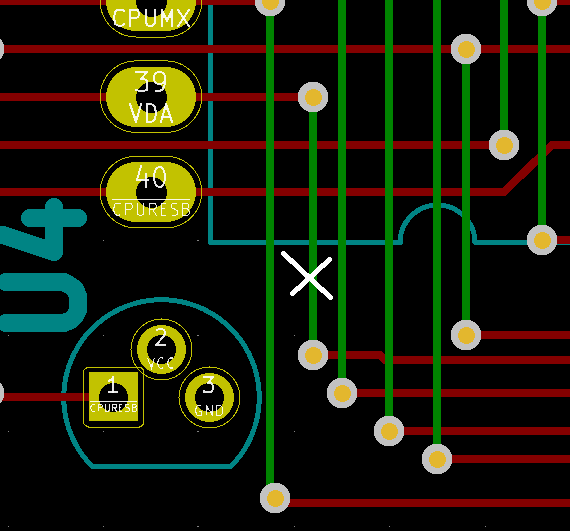

| + | * Cut etch U1-39 in rear (removes PH2OUT from backplane) | ||

| + | |||

| + | [[file:LB-6502_VPA_Rework.PNG]] | ||

| + | |||

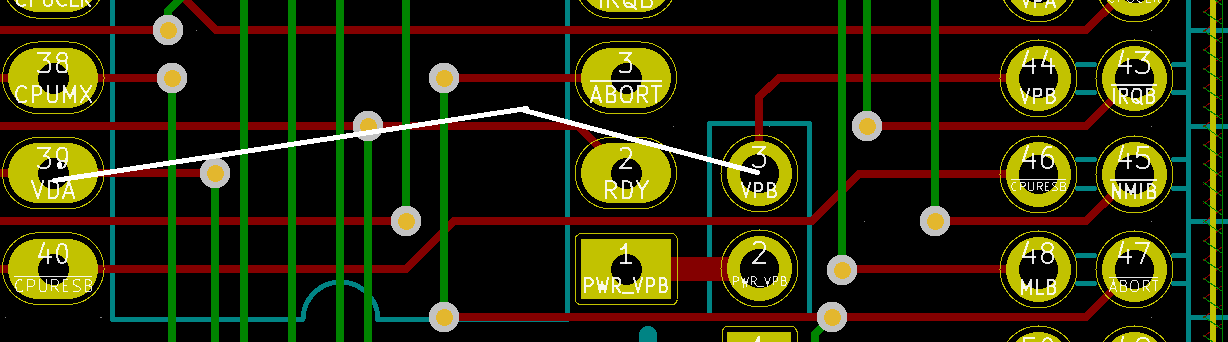

| + | * Add wire U1-39 to J2-3 (PH2OUT/VPB on VPB output) | ||

| + | |||

| + | [[file:LB-6502_VPB_Rework.PNG]] | ||

| + | |||

| + | ==== Rev 2 Changes ==== | ||

| + | |||

| + | * Add pull-up resistor on ABORT* line (U1-3) | ||

| + | * Add pull-up resistor on BE line (U1-36) | ||

| + | |||

| + | [[file:LB-65CXX-01_CPU_Rev2.PNG]] | ||

| + | |||

| + | === Rev 1 === | ||

* Install jumper J2:1-2 if CPU is not a WDC 65C02 or WDC 65C816 | * Install jumper J2:1-2 if CPU is not a WDC 65C02 or WDC 65C816 | ||

| − | * | + | * If WDC 65C02 or WDC 65C816 is used: |

| − | ** | + | ** Add pull-up resistor on ABORT* line (U1-3) |

| + | ** Add pull-up resistor on BE line (U1-36) | ||

== Assembly Sheet == | == Assembly Sheet == | ||

| + | |||

| + | === Rev 2 === | ||

| + | |||

| + | * [https://land-boards.com/LB-65CXX-01/LB-65CXX-01_Rev2_ibom.html Interactive BOM] | ||

=== Rev 1 === | === Rev 1 === | ||

* [https://land-boards.com/LB-65CXX-01/LB-65CXX-01_Rev1_ibom.html Interactive BOM] | * [https://land-boards.com/LB-65CXX-01/LB-65CXX-01_Rev1_ibom.html Interactive BOM] | ||

Latest revision as of 09:11, 7 October 2024

Features

- 65C02 or 65C816 CPU

- 2 MHz (typical) Oscillator on card

- Reset switch/power monitor

- Address decoder PLD drives RAM/ROM/IO chip selects

- 100x50mm card

Design

Memory Map

0x0000-0x7FFF - 32KB SRAM 0x8000-0x8FFF - 4KB I/O space 0x9000-0xBFFF - Free space (12 KB SRAM Using 128KB SRAM) 0xC000-0xFFFF - 16KB EPROM space

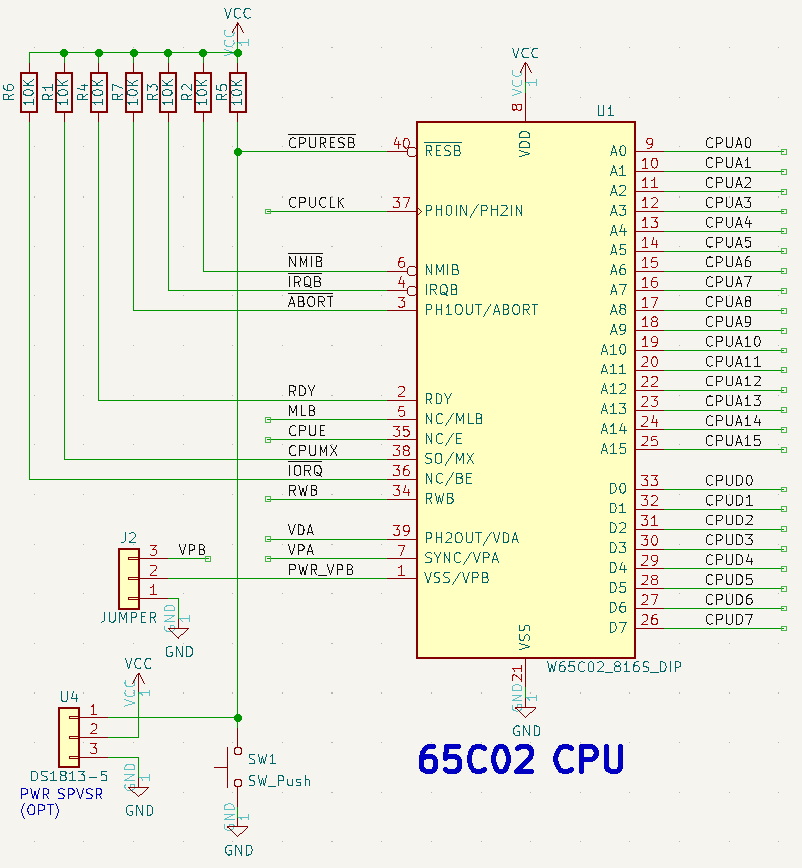

CPU

- 65C02 or 65C816 CPU

- 65C816 requires mods to the PCB (see Checkout notes below) or Rev 2 PCB

- 2 MHz

- Install jumper J2:1-2 if CPU is not a WDC 65C02 or WDC 65C816

R65C02 vs W65C02 vs W65C816 CPUs

| U1 Pin | U1 Pin Name | Sig Name | Pullup | R65C02 sig | W65C02 sig | W65C816 sig |

|---|---|---|---|---|---|---|

| 1 | VSS/VPB | J2 selects | N | VSS (IN) | VPB (OUT) | VPB (OUT) |

| 3 | PH1OUT/ABORT | ABORT* | REV2 | PH1OUT (OUT) | PH1OUT (OUT) | ABORT (IN) |

| 5 | NC/MLB | MLB | N | NC | MLB (OUT) | MLB (OUT) |

| 7 | SYNC/VPA | VPA | N | SYNC (OUT) | SYNC (OUT) | VPA (OUT) |

| 35 | NC/E | CPUE | N | NC | NC | EM/NAT (OUT) |

| 36 | NC/BE | IORQ* | REV2 | NC | BE (IN) | BE (IN) |

| 37 | PH0IN/PH2IN | CPUCLK | N | PH0IN | PH2IN | PH2IN |

| 38 | SO/MX | CPUMX | REV1/2 | SO* (IN) | SOB (IN) | MX (OUT) |

| 39 | PH2OUT/VDA | VDA | N | PH2OUT (OUT) | PH2OUT (OUT) | VDA (OUT) |

VDA/VPA (65C816)

- VDA/VDA

- 00, Internal operation (invalid address bus)

- 01, Valid Program Address

- 10, Valid Data Address

- 11, Opcode-fetch

Chip Set

- Picture shows 3 MHz CPU

- Received 2 MHz CPU

- As received:

Oscillator

PLD

- ATF16V8B part

- TL866ii Plus Programmer

PLD Listing

Name LB-65CXX-01_PLD; Partno ATF16V8B; Date 09/12/24; Revision 01; Designer DOUG G; Company LAND BOARDS LLC; Assembly LB65CXX01_U2; Location Rustbelt, US; Device G16V8; /* 65C02 Control */ /* Control inputs */ PIN 1 = CLK; PIN 2 = CPUA12; PIN 3 = CPUA13; PIN 4 = CPUA14; PIN 5 = CPUA15; PIN 6 = CPUREAD; PIN 8 = VPA; PIN 9 = VDA; /* Pin 39, PH2OUT - Enable line */ /* Address Decode and Chip Select outputs */ PIN 13 = !IOCS; PIN 14 = !ROMCS; PIN 15 = !MEMRD; PIN 16 = !RAMCS; PIN 18 = RDY; RAMCS = !CPUA15 & CPUREAD /* 0x0000-0x7FFF */ # !CPUA15 & !CPUREAD & VDA; IOCS = CPUA15 & !CPUA14 & CPUA13 & !CPUA12 & CPUREAD /* 0x8000-0x8FFF */ # CPUA15 & !CPUA14 & CPUA13 & !CPUA12 & !CPUREAD & VDA; ROMCS = CPUA15 & CPUA14 & CPUREAD; /* 0xC000-0xFFFF (16KB space) */ RDY = VDA; MEMRD = CPUREAD;

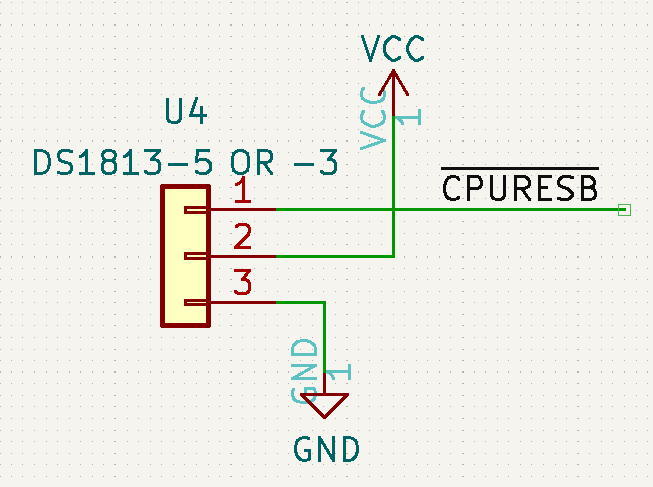

Reset Controller

- DS1813-5 Reset Controller

- 5V Power Monitor

- Reset controller

- Reset pushbutton to ground

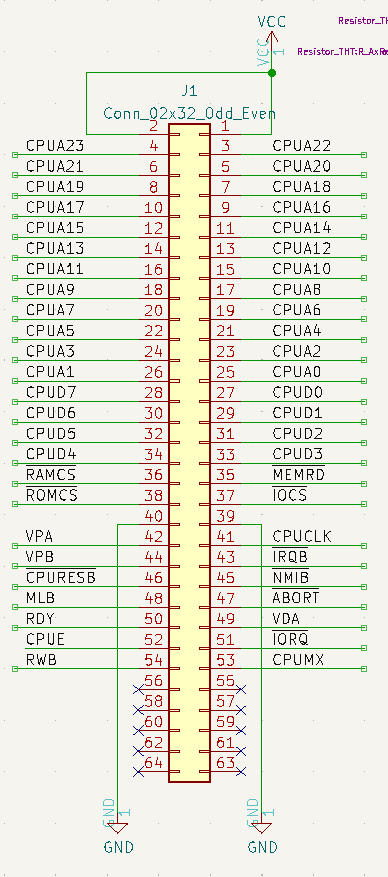

Backplane connector

Software

- LB-6502 GitHub

- SIMPLE-6502 Software - Reference software

Assembly Language Development Toolchain

- cc65 Assembler, Linker, Compiler

- Example batch file to assemble code and produce .hex file

ca65 AciaTest.s -o AciaTest.o -l ld65 -C AciaTest.cfg AciaTest.o -o AciaTest.bin srec_cat.exe AciaTest.bin -binary -o AciaTest.hex -Intel

MEMORY {

ROM: start = $C000, size = $3FFA, fill = yes, fillval=$FF, file = %O;

VECTS: start = $FFFA, size = $6, fill = yes, fillval=$FF, file = %O;

}

SEGMENTS {

CODE: load = ROM, type = ro;

VECTS: load = VECTS, type = ro;

}

ACIA Test Code

- ACIATest.s

- Loopback serial data

- Works

Simple Monitor 6502

- SimpleMon6502.s - GitHub repo

- Contains

- ACIA init, read, write

- Simplest commands mostly for function development

- String functions

- Read a string

- Write a string (macro)

- Write hex value as a string

- Dump page (256-bytes) of memory

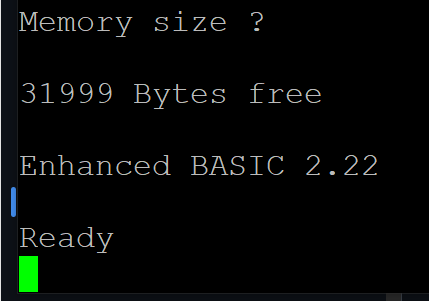

6502 Enhanced BASIC

- Enhanced BASIC Source Code on GitHub

- Free space using LB-MEM-02 card

?FRE(0) 31999

Enhanced BASIC Bug Fixes

- Enhanced BASIC Quirks and fixes

- Fixes the IRQ_vec missing error when assembling the code

; Ibuffs can now be anywhere in RAM, ensure that the max length is < $80,

; the input buffer must not cross a page boundary and must not overlap with

; program RAM pages!

;Ibuffs = IRQ_vec+$14

Ibuffs = VEC_SV+$16

; start of input buffer after IRQ/NMI code

Ibuffe = Ibuffs+$47; end of input buffer

- Added some of the patches from Enhanced BASIC Quirks and fixes

- Boots to request memory size

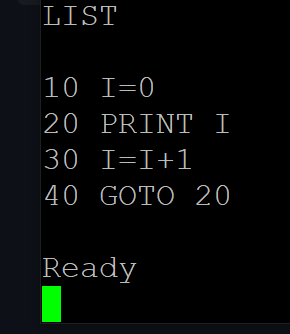

- Runs on card

OSI BASIC

- LB-6502 GitHub

- Generated from msbasic Source Code

- Grant Searle's 6502 design

- Source code

- osi_bas.s <== the Microsoft OSI BASIC and I/O routines SOURCE all in a single file

- Grant's I/O routines are at the end of it

- Files to allow the source to be assembled on a Windows based machine

- assemble.bat <== double click to assemble osi_bas.s and link to binary file "osi_bas.bin"

- This should be exactly 16K

- osi_bas.cfg <== configuration file for the linker (ensure ORG and entries in this file match if you change any)

- ca65.exe <== the assembler from the cc65 package. Use this. The new version on the cc65 site crashes!

- ld65.exe <== linker from the cc65 package

- srec_cat.exe <== Converts bin file to .hex file

- Output files

- osi_bas.bin <== the ROM fine in pure binary

- osi_bas.lst <== Assembly listing file

- rom.hex <== the ROM fine in standard INTEL-HEX format

- To allow simple re-assembly, extract all files to the same folder

- Use srec_cat utility to convert the "bin" file to HEX or s19 (etc)

- All source code, assembler binaries and the HEX dump of the ROM is here

- It is in standard INTEL-HEX format for uploading to a suitable programmer.

- Having trouble running code

Hacking MBASIC

VLT-2 for 6502

- VTL02 (VTL-2 for the 6502) by Mike Barry - on the 6502.org site

- Klaus's repo

- VTL-2 GitHub

- Thread about improvements to VLT-2

- VTL-2 Manual

Programming References

6502 Instruction Set

- The 6502 Instruction Set

- 6502 Programmer’s Reference

- 65(c)02 Instruction Set Reference

- 6502 / 6510 Instruction Set

Additional Tools

- 6502 Emulator - Simple emulator but it works

- virtual 6502 / Emulator

- 6502.org Tools for the 6502

Mechanicals

Checkout

Rev 3

PCB Updates

- Add bulk electrolytic cap

- Make PH2OUT on VPB backplane line (swap wth VDA)

- Change to vertical reset switch

- Add an LED that is written by writing D0 to ROM area

Rev 2

Rev 2 Checkout

- Install jumper J2:1-2 since CPU is R65C02

- NOP tester - 6502 nop = 0xEA

- Works

- Add LED

- 1.8K resistor from U2-17 to Ground

- Wire U2-11 to U1-33 CPUD0

- Cut etch U1-39 in rear (removes PH2OUT from backplane)

- Add wire U1-39 to J2-3 (PH2OUT/VPB on VPB output)

Rev 2 Changes

- Add pull-up resistor on ABORT* line (U1-3)

- Add pull-up resistor on BE line (U1-36)

Rev 1

- Install jumper J2:1-2 if CPU is not a WDC 65C02 or WDC 65C816

- If WDC 65C02 or WDC 65C816 is used:

- Add pull-up resistor on ABORT* line (U1-3)

- Add pull-up resistor on BE line (U1-36)