Difference between revisions of "SIMPLE-68008"

Jump to navigation

Jump to search

Blwikiadmin (talk | contribs) (→Design) |

Blwikiadmin (talk | contribs) (→Design) |

||

| Line 21: | Line 21: | ||

== Design == | == Design == | ||

| + | |||

| + | * CPU | ||

[[file:SIMPLE-68008_U5_CPU.PNG]] | [[file:SIMPLE-68008_U5_CPU.PNG]] | ||

| − | + | * EPROM | |

| − | [[file:]] | + | [[file:SIMPLE-68008_U8_EPROM.PNG]] |

| − | + | * SRAM | |

| − | [[file:]] | + | [[file:SIMPLE-68008_U7_SRAM.PNG]] |

| − | [[file:]] | + | * Dual UART |

| + | |||

| + | [[file:SIMPLE-68008_U6_DUART.PNG]] | ||

| + | |||

| + | * PLDs | ||

| + | |||

| + | [[file:SIMPLE-68008_U5_CPU.PNG]] | ||

| − | + | * Reset | |

| − | [[file:]] | + | [[file:SIMPLE-68008_U4_RESET.PNG]] |

| − | + | * Clock | |

| − | [[file:]] | + | [[file:SIMPLE-68008_U1_OSC.PNG]] |

== Headers / Connectors == | == Headers / Connectors == | ||

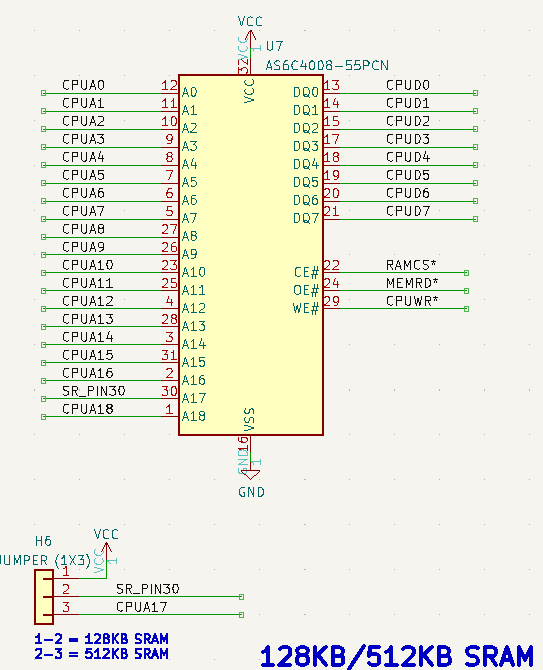

Revision as of 20:09, 3 March 2023

Contents

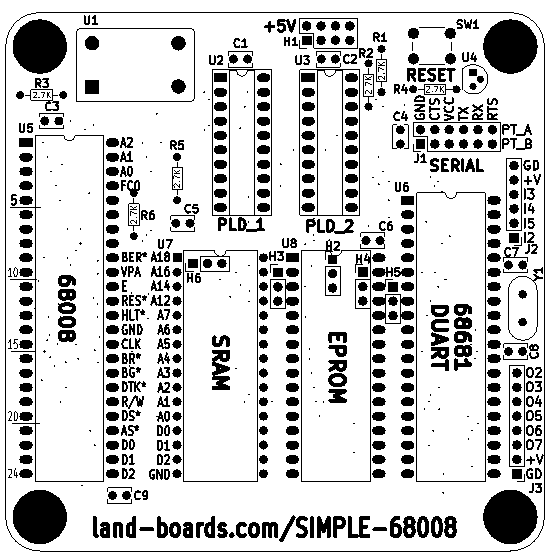

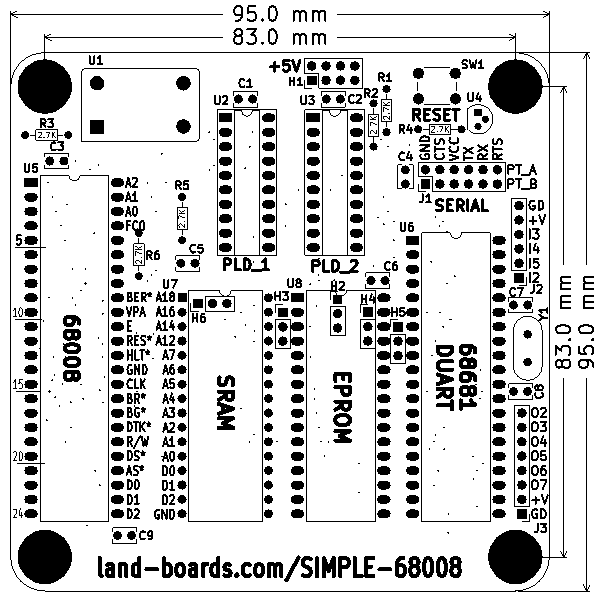

Features

- 68008 CPU

- 10 MHz clock

- 512KB SRAM

- Up to 448B EPROM/EEPROM

- 68681 Dual Serial Port (ACIA)

- Headers for FTDI

- 38,400 baud

- Reset switch with optional Power Supervisor

- 95x95mm card

- (4) 6-32 mounting holes

Memory Map

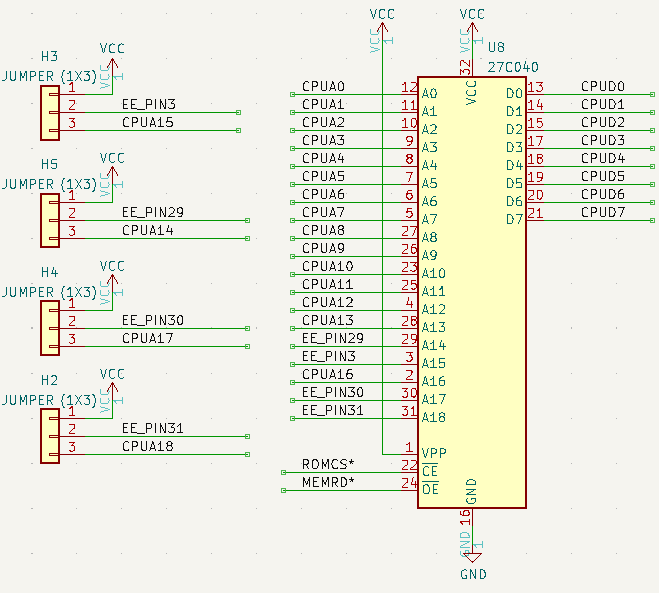

- 0x00000-0x7FFFF 32KB SRAM

- 0x80000-0x8FFFF Serial (ACIA)

- 0x99000-0xFFFFF Up to 8KB EPROM

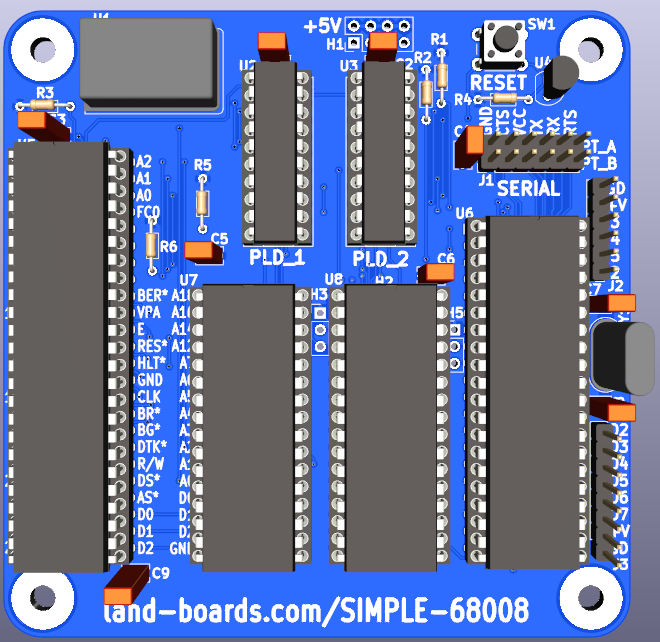

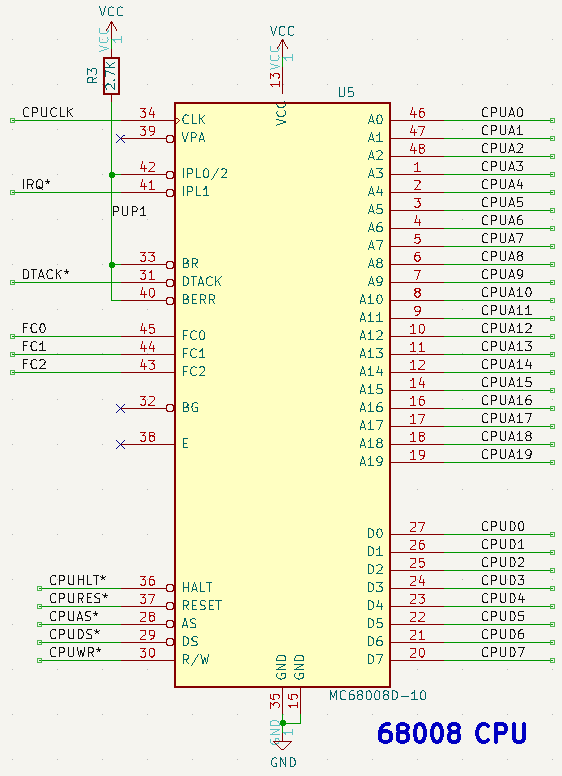

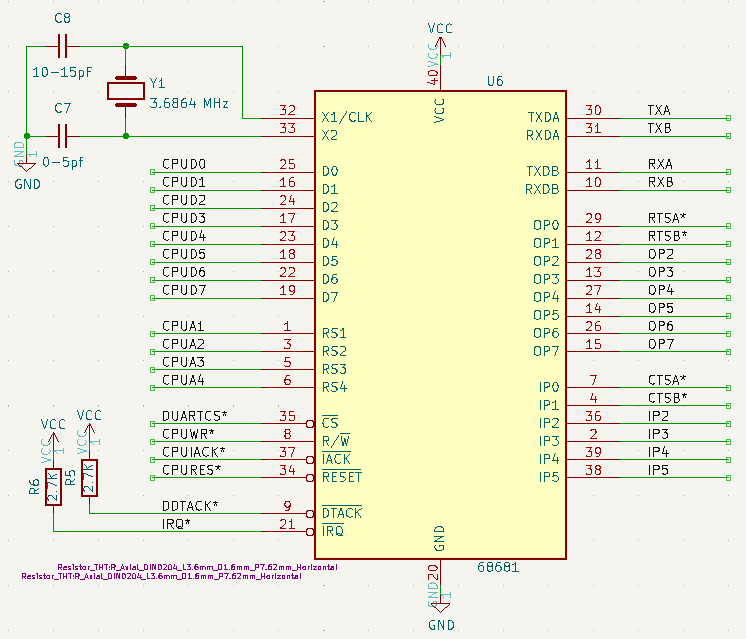

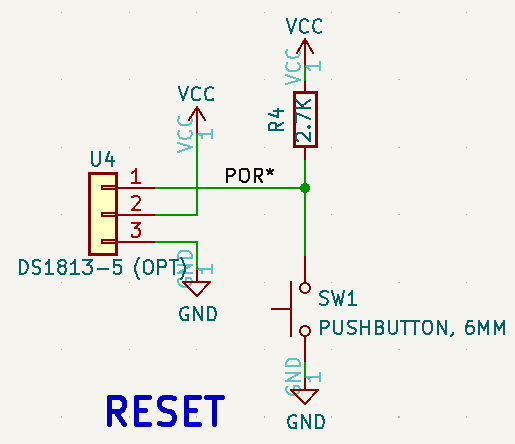

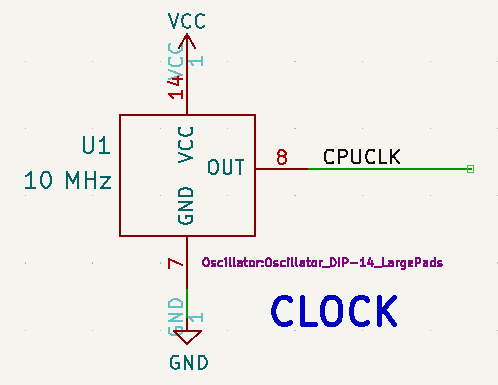

Design

- CPU

- EPROM

- SRAM

- Dual UART

- PLDs

- Reset

- Clock

Headers / Connectors

J1 - 2 port FTDI / TTL Serial

- 2x6 header

- Direct connect to DTE RS-232 card

- Flip order to connect to USB to TTL Serial (FTDI)

- TX<>RX

- RTS<>CTS

- Pinout

- GND

- CTS* (in)

- +5V

- Transmit (out)

- Receive (in)

- RTS* (out)

J2 - Input Port

- Input 2

- Input 5

- Input 4

- Input 3

- Vcc

- GND

J3 - Output Port

- GND

- Vcc

- Output 7

- Output 6

- Output 5

- Output 4

- Output 3

- Output 2

H1 - 5V Power

- 2x4 header

H3-H5 - EPROM/EEPROM Select Jumpers

- H2 = EE PIN 31

- H3 = EE PIN 3

- H4 = EE PIN 30

- H5 = EE PIN 29

| 27040 | 27020 | 27010 | 27512 | 27256 | 27128 | 2764 | PIN(32) | PIN(28) | PIN(28) | PIN(32) | 2764 | 27128 | 27256 | 27512 | 27010 | 27020 | 27040 | |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| VPP | VPP | VPP | N/A | N/A | N/A | N/A | 1 | N/A | N/A | 32 | N/A | N/A | N/A | N/A | VCC | VCC | VCC | |

| A16 | A16 | A16 | N/A | N/A | N/A | N/A | 2 | N/A | N/A | 31 (H2) | N/A | N/A | N/A | N/A | PGM | PGM | A18 | |

| A15 | A15 | A15 | A15 | VPP | VPP | VPP | 3 (H3) | 1 | 28 | 30 (H4) | VCC | VCC | VCC | VCC | N/C | A17 | A17 | |

| A12 | A12 | A12 | A12 | A12 | A12 | A12 | 4 | 2 | 27 | 29 (H5) | PGM | PGM | A14 | A14 | A14 | A14 | A14 | |

| A7 | A7 | A7 | A7 | A7 | A7 | A7 | 5 | 3 | 26 | 28 | A13 | A13 | A13 | A13 | A13 | A13 | A13 | |

| A6 | A6 | A6 | A6 | A6 | A6 | A6 | 6 | 4 | 25 | 27 | A8 | A8 | A8 | A8 | A8 | A8 | A8 | |

| A5 | A5 | A5 | A5 | A5 | A5 | A5 | 7 | 5 | 24 | 26 | A9 | A9 | A9 | A9 | A9 | A9 | A9 | |

| A4 | A4 | A4 | A4 | A4 | A4 | A4 | 8 | 6 | 23 | 25 | A11 | A11 | A11 | A11 | A11 | A11 | A11 | |

| A3 | A3 | A3 | A3 | A3 | A3 | A3 | 9 | 7 | 22 | 24 | OE* | OE* | OE* | OE* | OE* | OE* | OE* | |

| A2 | A2 | A2 | A2 | A2 | A2 | A2 | 10 | 8 | 21 | 23 | A10 | A10 | A10 | A10 | A10 | A10 | A10 | |

| A1 | A1 | A1 | A1 | A1 | A1 | A1 | 11 | 9 | 20 | 22 | CE* | CE* | CE* | CE* | CE* | CE* | CE* | |

| A0 | A0 | A0 | A0 | A0 | A0 | A0 | 12 | 10 | 19 | 21 | D7 | D7 | D7 | D7 | D7 | D7 | D7 | |

| D0 | D0 | D0 | D0 | D0 | D0 | D0 | 13 | 11 | 18 | 20 | D6 | D6 | D6 | D6 | D6 | D6 | D6 | |

| D1 | D1 | D1 | D1 | D1 | D1 | D1 | 14 | 12 | 17 | 19 | D5 | D5 | D5 | D5 | D5 | D5 | D5 | |

| D2 | D2 | D2 | D2 | D2 | D2 | D2 | 15 | 13 | 16 | 18 | D4 | D4 | D4 | D4 | D4 | D4 | D4 | |

| GND | GND | GND | GND | GND | GND | GND | 16 | 14 | 15 | 17 | D3 | D3 | D3 | D3 | D3 | D3 | D3 |